由于芯片工藝不斷改進,從0.35um、0.18um、0.13um到目前的40nm甚至28nm,芯片的內核電壓也在不斷降低,從3.3V、1.8V、1.5V到40nm器件的0.9V,芯片對電源的波動越來越敏感。

與SI相比,電源完整性PI是一個比較新的概念,實際上PI也屬于SI研究的范疇,它和SI之間的關系非常密切。

保持電源的完整性,就是保持電源的穩定供電。在實際系統中,要做到這一點并不容易,因為系統中總是存在著不同頻率的噪聲。

首先需要把電源分配系統與外界很好的隔離起來,電源系統與外界主要的連接途徑是電壓調整模塊,通常總是需要在電壓調整模塊的附近使用T型或者PI型濾波網絡。以放置低頻噪聲串入。同時大電容也提供了一個電荷的蓄水池,及時提供電壓調整模塊所不能供給的電流。

另外,系統內部的一些元件會產生高頻的電源噪聲,例如在數字邏輯門在翻轉的時候,瞬間會從電源平面汲取一定的電流。電流值雖然不是很大,但是速度很快,如果是電源分配系統的阻抗,電源平面不能及時提供這些電流,那么就會在這里產生翻轉噪聲。如果PCB去耦處理不當,這個電源噪聲就會波及整個電源地平面。

與此相類似,當信號線穿過一個過孔,切換信號的參考平面時,例如由地平面切換到電源平面,相應的會在過孔附近的電源平面和地平面之間形成一個回路電流,這個回路電流同樣會成為系統噪聲,波及整個電源分布系統。

同步開關噪聲

同步開關噪聲(SSN)是指由于多個輸出同時發生翻轉而引起的感應噪聲。

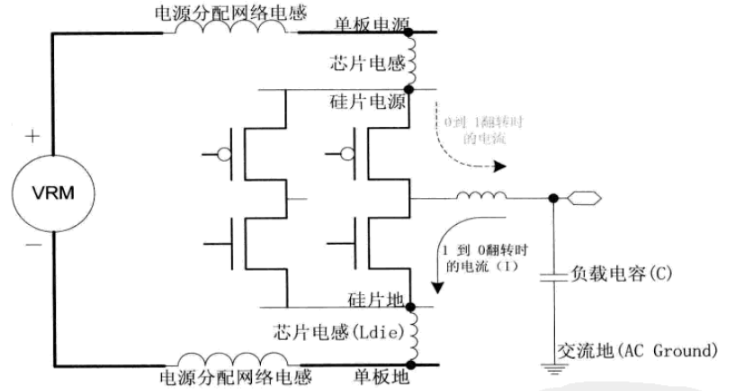

要搞清楚SSN的原理,必須從不同的層面來分析。下圖所示,電源分配系統的感抗表示,同時也把硅片到PCB電源之間的連線感抗也表示出來。

SSN模型

從芯片級來考慮,如果多個IO同時由“1”到“0”翻轉,會在地腳上產生較大的變化電流,上圖實線箭頭部分,由于芯片電感的存在,而電感的特性是產生一個反向電動勢來抵抗電流的變化,因此在硅片內部的地平面和單板地之間將形成一定的電壓波動,這種現象又稱為地彈(ground-bounce)。

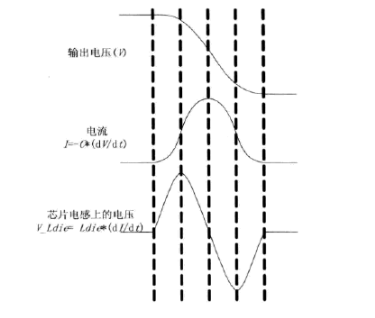

要知道PCB的地和硅片的地之間的電壓差關系,首先要分析輸出信號的電壓變化。當輸出信號由“1”翻轉到“0”時,在輸出驅動器的下拉MOS管和芯片電感上將產生一個相應的電流變化(I),這個電流滿足I=-C*(dV/dt),這里的負號表示電流的方向(灌電流)。如下圖I的變化情況,首先由0變為最大值,然后再回到0。

SSN產生原理

這樣的電流變化會在“芯片電感”兩端產生一個電壓的波動(V_Ldie) ,根據電感的特性,這個電壓值可以表示為V_Ldie=Ldie*(dI/dt),如上圖。

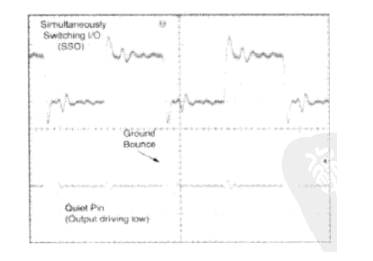

因此,在硅片地和PCB地之間就有一個V_Ldie的電壓差,假設PCB地保持不變,硅片地上就有一個相應的噪聲信號,這個噪聲信號會對輸出0的靜態信號造成影響,也有可能使得輸入信號誤采樣,如下圖,SSN對輸出低信號的影響。

SSN對輸出低信號的影響

-

電源

+關注

關注

184文章

17805瀏覽量

251039 -

pcb

+關注

關注

4324文章

23137瀏覽量

398889 -

MOS管

+關注

關注

108文章

2430瀏覽量

67213 -

電源完整性

+關注

關注

9文章

211瀏覽量

20749 -

數字邏輯

+關注

關注

0文章

73瀏覽量

16670

發布評論請先 登錄

相關推薦

如何保持電源的完整性 淺談SSN產生原理

如何保持電源的完整性 淺談SSN產生原理

評論