與模擬電路不同,數(shù)字電路需要快速的開關(guān)時間,因為它可以在“ 0”和“ 1”以及“ 1”和“ 0”信號電平之間進(jìn)行切換。當(dāng)速度增加時,切換周期減小。當(dāng)多個輸出同時從“高”邏輯切換到“低”時,存儲在I / O負(fù)載電容中的電荷流入器件。該電流通過具有接地阻抗的引腳通過內(nèi)部接地流出器件。開關(guān)電流以該阻抗產(chǎn)生電壓。因此,設(shè)備與電路板接地之間存在電壓差。該電壓差稱為接地反彈。接地反彈會導(dǎo)致板上的其他設(shè)備將“ LOW”輸出視為“ HIGH”。可以采用以下解決方案來減少地面反彈:

引腳擺率控制(允許設(shè)計者放慢驅(qū)動器的速度,以便降低跳動率)。快速擺率導(dǎo)致反射,串?dāng)_和地面反彈。

提供多個電源和接地引腳(允許將高速I / O引腳放置在靠近接地引腳的位置,以減少開關(guān)影響)。

減少高速PCB接地反彈的設(shè)計注意事項

在處理PCB中的高速信號時,設(shè)計人員應(yīng)考慮以下設(shè)計注意事項:

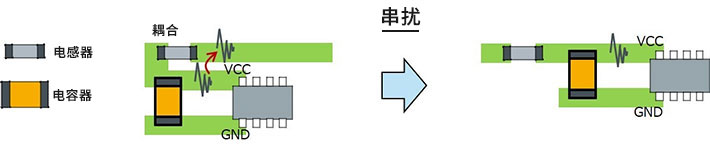

為相應(yīng)的VCC / GND對添加去耦電容。去耦電容應(yīng)盡可能靠近器件的電源和接地引腳。如果電源和GND通過通孔到達(dá)引腳,則應(yīng)在引腳和通孔之間放置去耦電容。

通過將去耦電容器靠近IC電源引腳放置,可降低電源軌噪聲。

在輸出處添加外部緩沖器,以最大程度地減少器件引腳上的負(fù)載。

通過使用外部設(shè)備(例如緩沖IC)緩沖負(fù)載來控制負(fù)載電容。

盡量減少可同時切換并在整個設(shè)備中均勻分配它們的輸出數(shù)量。

盡可能消除上拉電阻(使用下拉電阻)。

使用提供單獨(dú)的VCC和接地層的多層PCB。

同步設(shè)計。此類設(shè)計不會受到瞬時引腳切換的影響。

更大的通孔尺寸,以將電容器焊盤連接至電源和接地層,以減小去耦電容器中的電感。

將過孔靠近電容器焊盤。

通過將過孔靠近電容器焊盤放置,可以減少接地反彈。

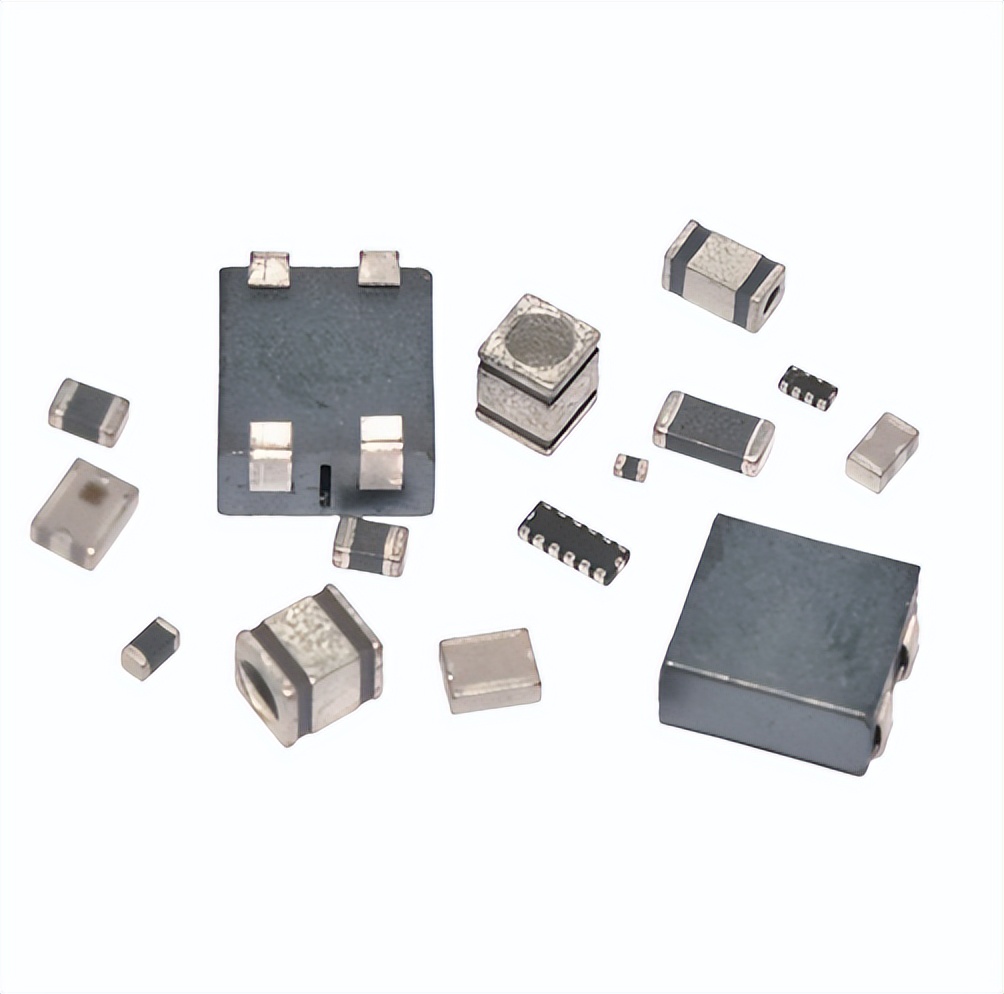

使用貼片電容可最大程度地減少引線電感。

注意:可通過電源平面提供均勻分布的電源來降低系統(tǒng)噪聲。

降低高速PCB設(shè)計中的EMI

PCB還影響系統(tǒng)的EMI / EMC性能。自動布線的電路板通常遵守設(shè)計規(guī)則(DRC),并且不滿足電磁兼容性要求。這樣的板需要固定,例如電纜和屏蔽外殼上的鐵氧體。因此,始終建議確保正確放置組件并以最佳方式布線走線。它有助于在給定的預(yù)算內(nèi)按時實現(xiàn)滿足所有電磁兼容性和信號完整性要求的產(chǎn)品。設(shè)計電磁兼容的PCB可以改善整個系統(tǒng)的性能。

每個PCB都容易受到電磁干擾。可以通過以下方式減少它:

使用低電感組件,例如具有低ESR和有效串聯(lián)電感(ESL)的貼片電容。

提供適當(dāng)?shù)慕拥兀詫崿F(xiàn)最短的電流返回路徑和最短的電流環(huán)路。

較短的返回路徑具有較低的阻抗,可提供更好的EMC性能。

始終在電源/信號平面旁邊使用接實地。

高速PCB設(shè)計人員的快速提示

確定最高頻率網(wǎng)絡(luò)并計算系統(tǒng)中最快的上升時間。

考慮一下受控阻抗值,端接和走線上的傳播延遲。

在微帶線(指的是在PCB的外層上由電介質(zhì)與參考平面(GND或VCC隔開)隔開的走線)和帶狀線(指的是在兩個參考平面的內(nèi)層上走線的走線)布線技術(shù)之間進(jìn)行選擇。確定哪種方法更符合EMC標(biāo)準(zhǔn),并能提供更好的信號完整性結(jié)果。

通過帶狀線和微帶路由進(jìn)行信號傳輸。

對于高質(zhì)量的信號傳輸,還應(yīng)考慮時鐘和差分路由技術(shù)。

通過差分路由傳輸信號。

考慮不同電源電壓的數(shù)量。為發(fā)送器路徑,接收器路徑,模擬信號,數(shù)字信號等功能組創(chuàng)建圖表。

區(qū)分高速信號和低速信號。

至少兩個獨(dú)立的功能組之間是否存在任何互連?注意它們,并始終考慮返回電流和與其他走線的串?dāng)_。

考慮一下空間寬度間隙。

兩層之間的最小距離應(yīng)該是多少?

鉆孔和過孔的最低要求是什么?使用盲孔和掩埋通孔是否可行?

責(zé)任編輯:tzh

-

電源

+關(guān)注

關(guān)注

184文章

17787瀏覽量

250895 -

pcb

+關(guān)注

關(guān)注

4323文章

23128瀏覽量

398695 -

IC

+關(guān)注

關(guān)注

36文章

5965瀏覽量

175822

發(fā)布評論請先 登錄

相關(guān)推薦

AN136-非隔離式開關(guān)電源的PCB布局注意事項

Tips:大功率電源PCB繪制注意事項

CC13xx/CC26xx硬件配置和PCB設(shè)計注意事項

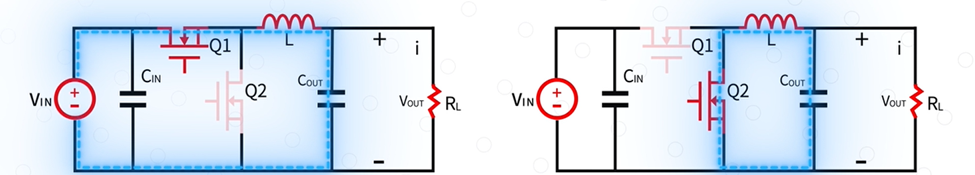

Buck電路中PCB layout布局設(shè)計和注意事項

pcb印制板設(shè)計規(guī)則要求有哪些?你知道多少!

PCB設(shè)計的EMC有哪些注意事項

FPGA的高速接口應(yīng)用注意事項

高頻高密度PCB布局設(shè)計注意事項

PCB板布局相關(guān)的注意事項

減少PCB地面反彈的設(shè)計注意事項

減少PCB地面反彈的設(shè)計注意事項

評論