克服PCB電磁問題

電磁問題一直困擾著PCB設(shè)計(jì)人員。系統(tǒng)設(shè)計(jì)工程師必須始終監(jiān)視電磁兼容性和干擾。不幸的是,即使很小的設(shè)計(jì)問題也可能導(dǎo)致電磁故障。隨著電路板設(shè)計(jì)的縮小以及客戶要求更高的速度,這些問題比以往任何時(shí)候都更加普遍。

起作用的兩個(gè)主要問題是電磁兼容性和電磁干擾。

電磁兼容性(EMC)涉及電磁能的產(chǎn)生,傳播和接收,通常是通過不良設(shè)計(jì)來實(shí)現(xiàn)的。電磁干擾或EMI是指EMC產(chǎn)生的有害影響,以及來自環(huán)境的電磁干擾。太多的EMI可能會(huì)導(dǎo)致產(chǎn)品損壞或損壞。任何PCB設(shè)計(jì)人員都應(yīng)遵循EMC設(shè)計(jì)規(guī)則,以最大程度地減少EMI的影響。

幸運(yùn)的是,適當(dāng)?shù)?/span>EMC設(shè)計(jì)可以減少電路板的EMI。

為什么避免電磁干擾很重要

電磁干擾源無處不在,我們 可以通過幾種方式對(duì)它們進(jìn)行分類:

l資料來源: 人為產(chǎn)生的EMI來自電子電路。另一方面,自然產(chǎn)生的EMI可能是由諸如宇宙噪聲和閃電之類的環(huán)境因素引起的。

l持續(xù)時(shí)間: 持續(xù)干擾是一種EMI源,它發(fā)出恒定的信號(hào),該信號(hào)通常以背景噪聲的形式出現(xiàn)。脈沖干擾是間歇性的,通常是由開關(guān)系統(tǒng),雷電和其他非恒定源引起的。

l帶寬: 類似于無線電的窄帶信號(hào)可能會(huì)受到振蕩器和發(fā)射機(jī)的干擾,盡管這些源只會(huì)間歇性地影響頻譜的某些部分。寬帶干擾會(huì)影響電視等高數(shù)據(jù)信號(hào),并且可能來自許多來源,包括弧焊機(jī)和太陽噪聲。

不論是人為制造的還是環(huán)境的,EMI都可能既昂貴又危險(xiǎn)。它可能會(huì)破壞通信通道和敏感設(shè)備。在無線設(shè)備使用率不斷上升的醫(yī)療領(lǐng)域,EMI是一個(gè)值得注意的問題。不幸的是, EMI會(huì)影響 呼吸機(jī),ECG監(jiān)護(hù)儀,心臟監(jiān)護(hù)儀和除顫器等醫(yī)療設(shè)備的功能。在其他行業(yè)中,EMI可能會(huì)破壞傳感器和導(dǎo)航系統(tǒng)。在所有情況下,結(jié)果都是對(duì)設(shè)備的干擾,可能會(huì)對(duì)用戶的健康和安全負(fù)責(zé)。

但是,最常見的EMI來源-也是設(shè)計(jì)人員最有問題的來源-內(nèi)部。不良的PCB設(shè)計(jì)可能會(huì)導(dǎo)致不兼容的信號(hào)在板上相互干擾。這種干擾最終可能導(dǎo)致電路板發(fā)生故障。設(shè)計(jì)人員必須確保將干擾保持在最低水平,釋放的任何信號(hào)都應(yīng)兼容,以免造成干擾。

預(yù)防和解決電磁問題的EMC設(shè)計(jì)原則

電路板設(shè)計(jì)者必須遵循電磁兼容性設(shè)計(jì)原則,以將EMI降至最低。EMC問題的基本原因相當(dāng)普遍,并且大多數(shù)與設(shè)計(jì)缺陷有關(guān),這些設(shè)計(jì)缺陷會(huì)導(dǎo)致走線,電路,過孔,PCB線圈和其他元件之間的干擾。

這些基本的設(shè)計(jì)原則可以幫助防止和修復(fù)印刷電路板設(shè)計(jì)中的電磁問題。

1.接地層

設(shè)計(jì)PCB的接地層是最重要的一步,對(duì)于降低EMI至關(guān)重要。接地層是抵抗EMI的第一道防線,因?yàn)樗须娐范夹枰拥夭拍苷9ぷ鳌=档?/span>EMI的接地設(shè)計(jì)的一些常見最佳做法包括:

l最大化接地面積: 在PCB內(nèi)盡可能增加接地面積。信號(hào)可以在更大的范圍內(nèi)更容易地分散,從而減少發(fā)射,串?dāng)_和噪聲。如果接地層太小,則可以添加另一層并創(chuàng)建多層PCB。該設(shè)計(jì)解決方案提供了更多處理高速跟蹤的選項(xiàng)。

l使用實(shí)心平面: 尤其是在多層PCB中,實(shí)心接地平面是理想的選擇。銅剝皮和散亂的接地層通常會(huì)導(dǎo)致更高的阻抗水平。另一方面,堅(jiān)固的接地層提供了較低的高度。

l連接每個(gè)組件: 將每個(gè)零件連接到接地平面或點(diǎn)。接地層充當(dāng)電路板設(shè)計(jì)的中和劑,而浮動(dòng)組件并未充分利用它。

l小心分開的平面: 高度復(fù)雜的PCB設(shè)計(jì)通常包括許多穩(wěn)壓電壓,每個(gè)電壓都有自己的接地層。然而,太多的接地平面增加了制造成本。通常通過使用分割平面來避免此問題,分割平面在單層上創(chuàng)建多個(gè)接地部分。但是,設(shè)計(jì)人員應(yīng)始終謹(jǐn)慎使用分割平面。確保有充分的理由使用分離平面;如果使用分離平面,請(qǐng)確保僅將其連接在單個(gè)點(diǎn)上。分體接地PCB中的多個(gè)接地連接會(huì)產(chǎn)生環(huán)路,從而導(dǎo)致天線輻射EMI。

l連接旁路或去耦電容器: 如果設(shè)計(jì)中包括旁路或去耦電容器,則將其連接至接地層。此行為通過減小環(huán)路尺寸來幫助減小返回電流。

l最小化信號(hào)長度: 走線的長度非常重要,因?yàn)樾盘?hào)往返于源所花費(fèi)的時(shí)間必須兼容。否則會(huì)輻射EMI。保持跡線的長度應(yīng)盡可能短,并且長度應(yīng)相等。

2.走線布局

跡線對(duì)于電路板設(shè)計(jì)尤為重要。正確使用走線可確保正確傳播電流。但是,如果未按照頂級(jí)EMC設(shè)計(jì)規(guī)則排列走線,則會(huì)出現(xiàn)許多問題。

跡線實(shí)質(zhì)上是在電路處于活動(dòng)狀態(tài)時(shí)包含流動(dòng)電子的導(dǎo)電路徑。因此,這些走線與創(chuàng)建輻射天線是一個(gè)錯(cuò)誤。簡單的彎曲或交叉會(huì)導(dǎo)致PCB電磁干擾。

PCB設(shè)計(jì)中走線布局的一些最佳規(guī)則包括:

l避免直角: 過孔,走線和其他零件的角度應(yīng)避免為45度至90度。 電容隨著走線達(dá)到 45度以上的角度而增加。結(jié)果,特性阻抗改變,導(dǎo)致反射。這種反射會(huì)導(dǎo)致EMI。您可以通過舍入需要轉(zhuǎn)彎的跡線或?qū)⑺鼈兝@過兩個(gè)或多個(gè)45度或更小的角度來避免此問題。

l將信號(hào)分開: 將高速走線與低速信號(hào)分開,將模擬信號(hào)與數(shù)字信號(hào)分開。緊密接近會(huì)導(dǎo)致干擾。

l縮短返回路徑: 使返回電流路徑盡可能短,并沿電阻最小的路徑布線。返回路徑的長度應(yīng)與傳輸軌跡的長度相同或更短。

l間距: 兩個(gè)并行運(yùn)行的高速信號(hào)會(huì)通過串?dāng)_產(chǎn)生EMI,其中一條跡線是“攻擊者”,另一條跡線是“受害者”。攻擊者通過電感和電容耦合影響受害者跡線,在受害者跡線中產(chǎn)生正向和反向電流。您可以通過在跡線之間保持最小間距來最大程度地減少串?dāng)_。通常,將跡線分隔為跡線寬度的兩倍。例如,如果走線的寬度為千分之五千英寸,則在兩條平行走線之間的最小距離至少為千分之千英寸。

l仔細(xì)使用過孔:過 孔在PCB設(shè)計(jì)中是必需的,因?yàn)檫^孔可讓您在布線時(shí)利用電路板上的多層。但是,設(shè)計(jì)人員在使用它們時(shí)必須小心。通孔會(huì)在混合中添加自己的電感和電容效應(yīng),可能會(huì)由于特性阻抗的變化而導(dǎo)致反射。通孔還會(huì)增加走線長度,需要匹配。如有可能,避免使用過孔作為差分走線。但是,如果不可能,請(qǐng)?jiān)趦蓷l走線中都使用它們以補(bǔ)償延遲。

3.組件安排

電子元件是電子電路的基礎(chǔ)。但是,如果安排不當(dāng),可能會(huì)導(dǎo)致幾個(gè)EMI問題。在設(shè)計(jì)PCB時(shí),請(qǐng)注意每片的EMI影響。PCB設(shè)計(jì)中組件布局的一些最佳做法包括:

l將模擬和數(shù)字部分分開: 與走線一樣,始終將模擬和數(shù)字電路和組件分開。靠近放置模擬電路和數(shù)字電路會(huì)導(dǎo)致串?dāng)_,其中包括其他問題。為避免這種情況,請(qǐng)使用屏蔽層,多層結(jié)構(gòu)和分開的接地層,以使模擬信號(hào)和數(shù)字信號(hào)盡可能彼此遠(yuǎn)離。通常,最好將模擬和數(shù)字信號(hào)完全放在單獨(dú)的地面上。

l模擬和高速部件分開: 模擬電路承載大電流,這可能會(huì)導(dǎo)致高速走線和開關(guān)信號(hào)出現(xiàn)問題。使它們彼此遠(yuǎn)離,并用接地信號(hào)保護(hù)模擬電路。在多層PCB上,對(duì)模擬走線進(jìn)行布線,以使模擬電路與開關(guān)或高速信號(hào)之間存在接地層。

l小心高速組件:組件 越快越小,可能產(chǎn)生的EMI越大。您可以通過屏蔽和濾波來抵抗這種自然的EMI,盡管在電路板設(shè)計(jì)中將這些組件與其他組件分開也是一個(gè)好主意。采取的另一措施是使高速信號(hào)和時(shí)鐘盡可能短,并與接地層相鄰。這些措施有助于將串?dāng)_,噪聲和輻射水平控制在可接受的水平范圍內(nèi)。

4. EMI屏蔽

無論您遵循什么設(shè)計(jì)規(guī)則,某些組件都會(huì)產(chǎn)生EMI,尤其是小型高速零件。幸運(yùn)的是,屏蔽和濾波可以將EMI的影響降至最低。一些屏蔽和過濾選項(xiàng)包括:

l組件和電路板的屏蔽: 物理屏蔽是封裝了整個(gè)或部分電路板的金屬封裝。他們的目標(biāo)是防止EMI進(jìn)入電路板電路,盡管具體方法根據(jù)EMI的來源而有所不同。對(duì)于來自系統(tǒng)內(nèi)部的EMI,可以使用組件屏蔽罩來封裝產(chǎn)生EMI的特定組件,從而將其接地,從而減小天線環(huán)路的尺寸并吸收EMI。其他屏蔽可能會(huì)包裹整個(gè)電路板,以防止外部源產(chǎn)生EMI。例如,法拉第籠(Faraday Cage)是一種厚實(shí)的防護(hù)罩,旨在阻擋RF波。這些設(shè)備通常由金屬或?qū)щ娕菽瞥伞?/span>

l低通濾波: 有時(shí),PCB可以包括低通濾波器以消除組件的高頻噪聲。這些濾波器抑制了來自這些部分的噪聲,從而使電流在返回路徑上繼續(xù)流動(dòng)而不受干擾。

l電纜屏蔽: 承載模擬和數(shù)字電流的電纜會(huì)產(chǎn)生最大的EMI問題。它們通過產(chǎn)生寄生電容和電感來產(chǎn)生這些問題,這是高頻信號(hào)的一個(gè)特殊問題。幸運(yùn)的是,屏蔽這些電纜并將其前后分別接地有助于消除EMI干擾。

-

印制電路板

+關(guān)注

關(guān)注

14文章

957瀏覽量

40831 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

394文章

4692瀏覽量

85887 -

PCB打樣

+關(guān)注

關(guān)注

17文章

2968瀏覽量

21747 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3494瀏覽量

4597

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

PCB上壓接孔和過孔的孔徑和公差要求相同,制造時(shí)有何影響

PCB板的電磁協(xié)同設(shè)計(jì)

模擬隔離對(duì) PCB 設(shè)計(jì)有何影響

何為電磁干擾(EMI)掃描儀,哪里需要它?

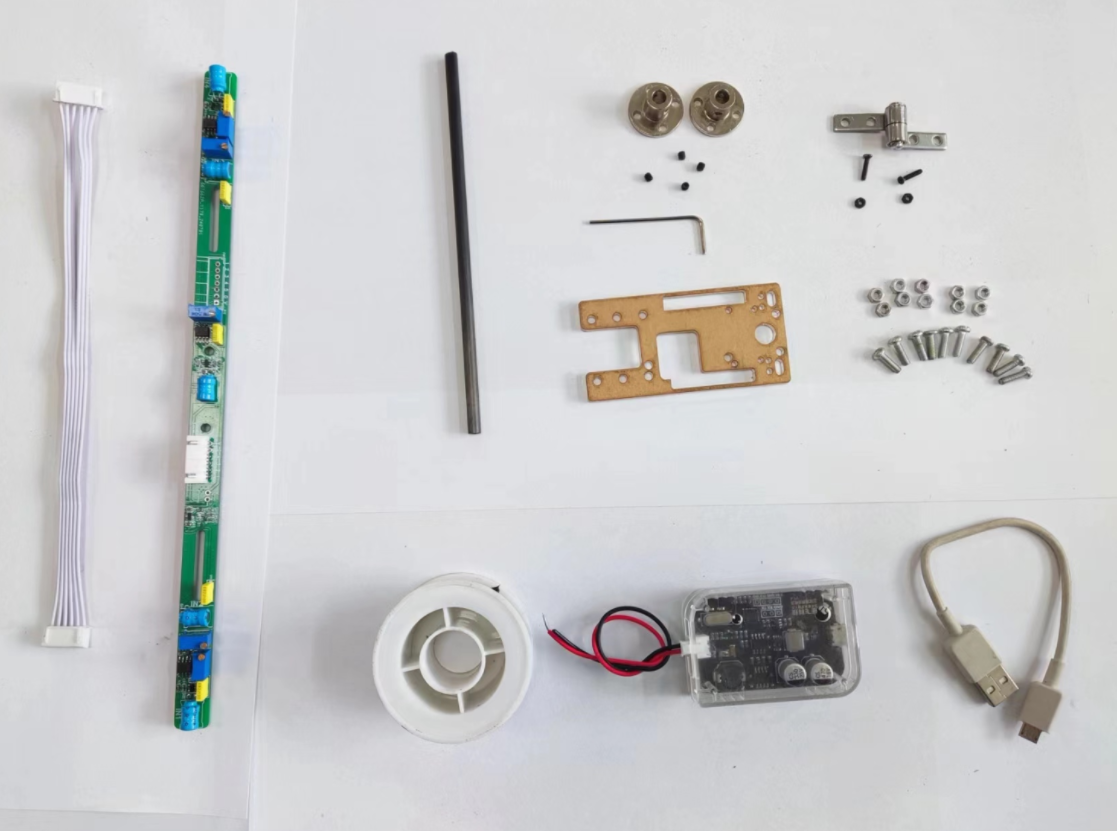

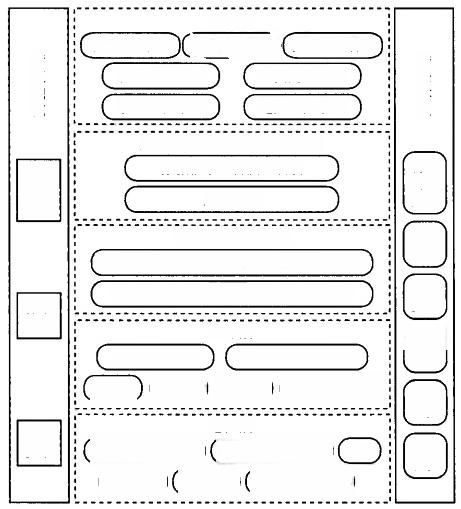

20.0-電磁桿的組裝和實(shí)物介紹“這個(gè)是就是你想要的“-智能車電磁組 電磁循跡小車

電磁繼電器由什么組成

客戶有哪些封裝案例,一句克服使用讓PCBA工廠淚流滿面

這幾招教你解決PCB設(shè)計(jì)中的電磁干擾(EMI)問題

上海5月24-25日《PCB電磁兼容設(shè)計(jì)與評(píng)審方法》公開課報(bào)名中

上海5月17-18日《PCB電磁兼容設(shè)計(jì)與評(píng)審方法》公開課報(bào)名中

淺談煤礦井下無入值守變電所技術(shù)研究與應(yīng)用

線圈式電磁炮原理 線圈式電磁炮模型的組成

【電磁兼容技術(shù)案例分享】由SGMII通訊導(dǎo)致的輻射發(fā)射高頻單支超標(biāo)問題解決案例

PCB入何克服由電磁所引起的問題

PCB入何克服由電磁所引起的問題

評(píng)論