串行輸入,串行輸出移位寄存器每級將數據延遲一個時鐘時間。它們將為每個寄存器存儲一點數據。串行輸入,串行輸出移位寄存器的長度可能為一到64位,如果級聯寄存器或封裝,則長度會更長。下面是一個單級移位寄存器,用于接收與寄存器時鐘不同步的數據。

當時鐘由低變高時,DFF(觸發器)類型的D引腳上的“數據輸入”不會改變電平。我們可能希望將數據同步到電路板上的系統級時鐘,以提高數字邏輯電路的可靠性。

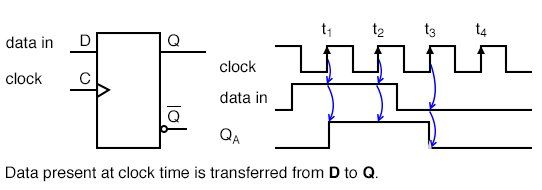

上面所示的明顯點(與下圖相比)是,在DFF類型的D引腳上存在的任何“數據輸入”都在時鐘時間從D傳輸到輸出Q。由于我們的示例移位寄存器使用的是上升沿敏感的存儲元件,因此當時鐘從低到高轉換時,輸出Q跟隨D輸入,如上圖的向上箭頭所示。

毫無疑問,在時鐘時間存在什么邏輯電平,因為數據在時鐘沿之前和之后都穩定。在多級移位寄存器中很少出現這種情況。但是,這是一個簡單的例子。我們只關心從低到高的正時鐘沿。下降沿可以忽略。很容易看到Q在上面的時鐘時間跟隨D。將其與下圖比較,其中“數據輸入”似乎隨時鐘的上升沿而變化。

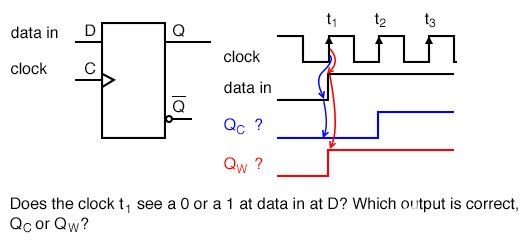

由于“數據輸入”似乎在上述時鐘時間t1發生了變化,因此DFF類型在時鐘時間會看到什么?簡短的簡化答案是,它會在時鐘之前看到D處存在的數據。那就是在時鐘時間t1傳輸到Q的內容。正確的波形是Q?。如果在t1處Q還不是零,則Q變為零。所述d寄存器不看到一個直到時間t2,在該時間Q變高。

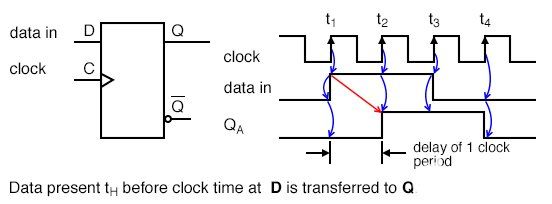

由于在D處出現的上述數據在某個時鐘時刻被計時到Q,并且Q直到下一個時鐘時刻才能改變,因此DFF將數據延遲一個時鐘周期,前提是該數據已與該時鐘同步。QA波形與“數據輸入”相同,但延遲一個時鐘周期。接下來將詳細介紹D型觸發器的輸入在時鐘時間的情況。

請參考下圖。由于“數據輸入”似乎在時鐘時間(以上)發生變化,因此我們需要更多信息來確定DFF看到的內容。如果“數據輸入”來自另一個移位寄存器級,另一個相同的DFF,我們可以根據數據手冊信息得出一些結論。數字邏輯制造商在數據表中提供了有關其零件的信息,以前僅在稱為數據手冊的集合中可用。數據手冊仍然可用;但是,制造商的網站是現代資源。

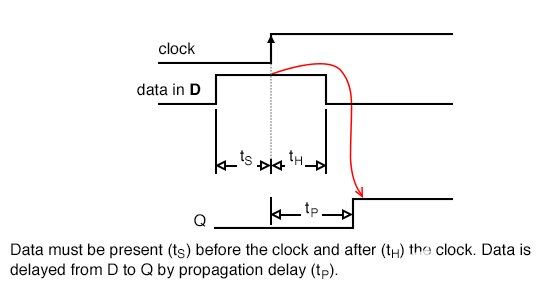

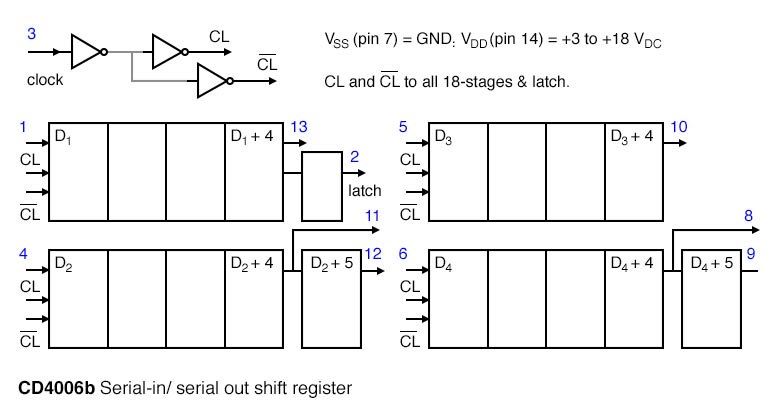

下面的數據是從CD4006b數據表中提取的,用于在5VDC下工作,這是一個說明時序的示例。[*]

tS= 100ns

tH= 60ns

tP= 200-400ns典型值/最大值

tS是建立時間,時間數據必須在時鐘時間之前存在。在這種情況下,數據必須在時鐘之前的D100ns出現。此外,必須在時鐘時間之后將數據保持時間tH= 60ns。必須滿足這兩個條件,才能將數據從D可靠地時鐘到觸發器Q。滿足60ns的建立時間沒有問題,因為如果D處的數據來自另一個移位寄存器級,則該數據在整個先前的時鐘周期內一直存在。

例如,在1 Mhz的時鐘頻率下,時鐘周期為1000 μs,這是很多時間。實際上,數據將在時鐘之前存在1000μs,這比60ns的最低要求tS大得多。之所以滿足保持時間tH= 60ns,是因為連接到另一級Q的D的變化不能快于前一級tP= 200ns的傳播延遲。只要前一個DFF的傳播延遲大于保持時間,就可以滿足保持時間。

對于CD4006b,由另一級Q驅動的D處的數據變化不會快于200ns。總而言之,如果觸發器級聯到多級移位寄存器中,則輸出Q在接近時鐘時間跟隨輸入D。

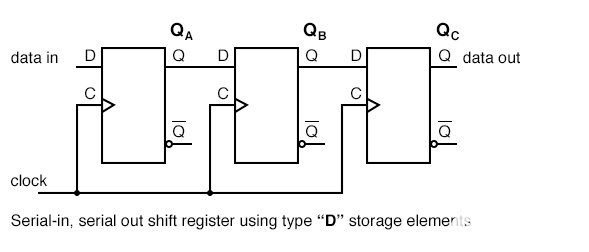

三個D型觸發器在Q到D之間級聯,并且時鐘并行,以在上面形成三級移位寄存器。

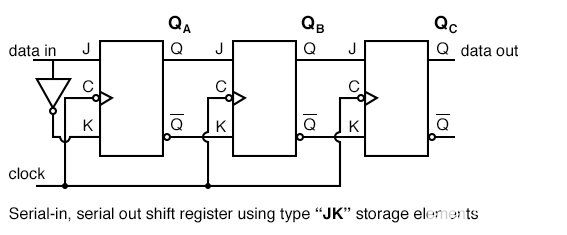

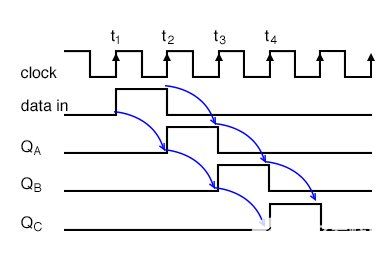

鍵入JK翻轉Flopss級聯Q可J,Q”至K的時鐘在平行于上述得到的移位寄存器的另一種形式。串行輸入/串行輸出移位寄存器具有時鐘輸入,數據輸入和最后一級的數據輸出。通常,其他級輸出不可用,否則它將是一個串行輸入,并行輸出移位寄存器。以下波形適用于串行輸入,串行輸出移位寄存器的前兩個版本之一。三對箭頭表示三級移位寄存器臨時存儲3位數據,并將其從輸入到輸出延遲三個時鐘周期。

在時刻t1“數據中”的0是從計時d到Q的所有三個階段。特別地,階段A的D看到邏輯0,該邏輯0被計時到QA,在這里它一直保持到時間t2。在時刻t2“數據在”的1從計時d至QA。在階段乙和?,一個0,從先前級供給的計時至Q乙和Q?。

在時刻t3“數據中”的0是從計時d至QA。由于“ data in”為0,QA變為低電平并在其余時鐘中保持低電平。由于前一級為1,QB在t3處變高。由于前一階段的較低,在t3之后QC仍然較低。由于從前一級QB饋入D的高電平,QC最終在時鐘t4處變為高電平。所有早期階段都有0s移入其中。并且,在t5的下一個時鐘脈沖之后,所有邏輯1s將被移出,取而代之的是0s

串行輸入/串行輸出設備

CD4006b 18位串行輸入/輸出移位寄存器

CD4031b 64位串行輸入/輸出移位寄存器

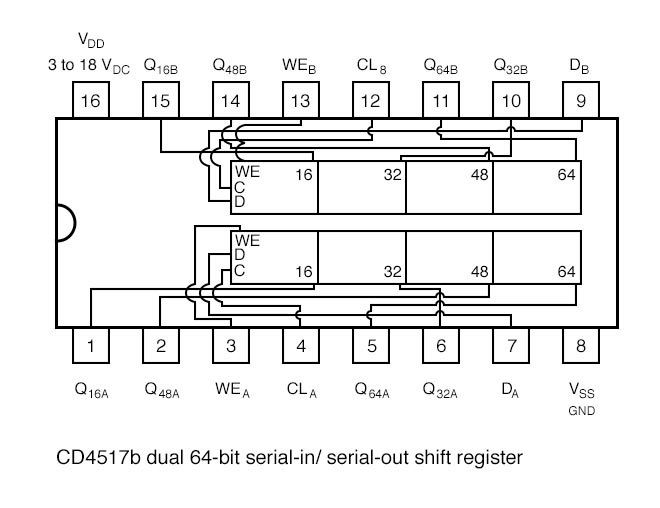

CD4517b雙64位串行輸入/輸出移位寄存器

以下串行輸入/串行輸出移位寄存器是4000系列CMOS(互補金屬氧化物半導體)系列器件。因此,他們將接受3到15伏的VDD正電源。VSS引腳接地。移位時鐘的最大頻率隨VDD變化,為幾兆赫茲。

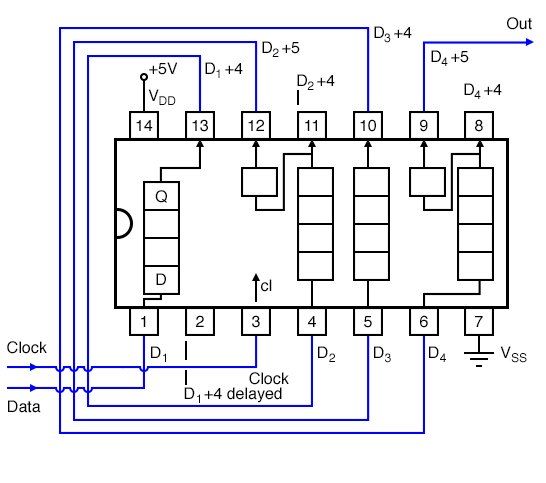

18位CD4006b由兩級4位和另外兩級5位組成,輸出抽頭為4位。因此,5位級可以用作4位移位寄存器。要獲得完整的18位移位寄存器,必須將一個移位寄存器的輸出級聯到另一個移位寄存器的輸入,依此類推,直到所有級都創建一個移位寄存器,如下所示。

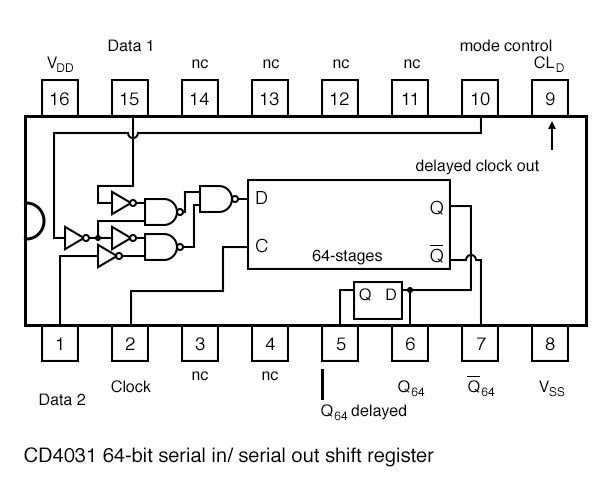

CD4031 64位串行輸入/輸出移位寄存器如下所示。未連接許多引腳(nc)。Q和Q“是可從第64階段,實際上Q64和Q”64。還有一個Q64從半級“延遲”,它延遲了半個時鐘周期。一個主要功能是數據選擇器,它位于輸入到移位寄存器的數據上。

“模式控制”在兩個輸入之間進行選擇:數據1和數據2。如果“模式控制”為高,將從“數據2”中選擇數據以輸入到移位寄存器。在“模式控制”為邏輯低的情況下,選擇“數據1”。下面的兩個圖中顯示了此示例。

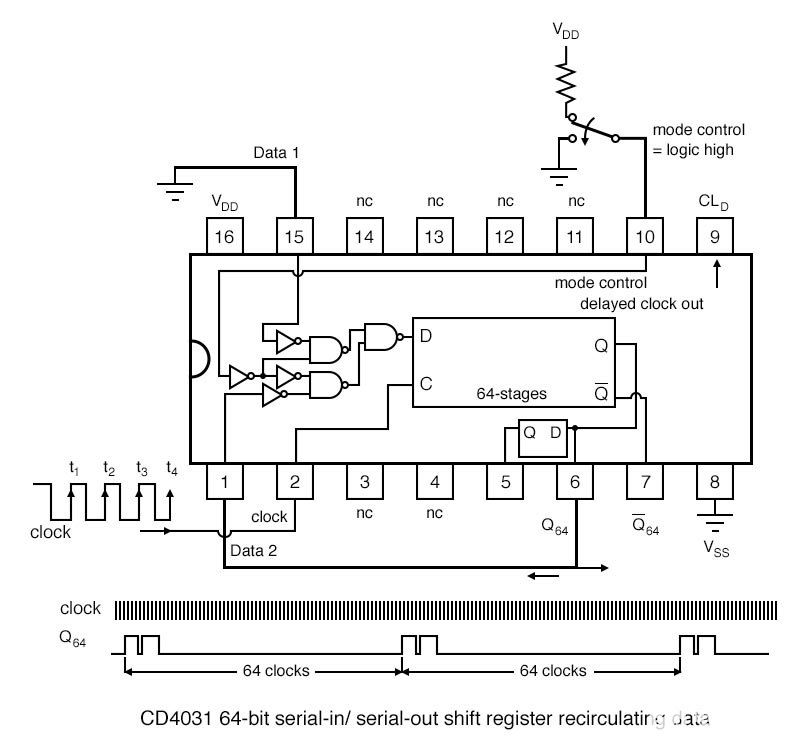

上面的“數據2”連接到移位寄存器的Q64輸出。當“模式控制”為高電平時,Q64輸出被路由回到移位器數據輸入D。數據將從輸出循環到輸入。如上所示,數據將每64個時鐘脈沖重復一次。出現的問題是該數據模式如何首先進入移位寄存器?

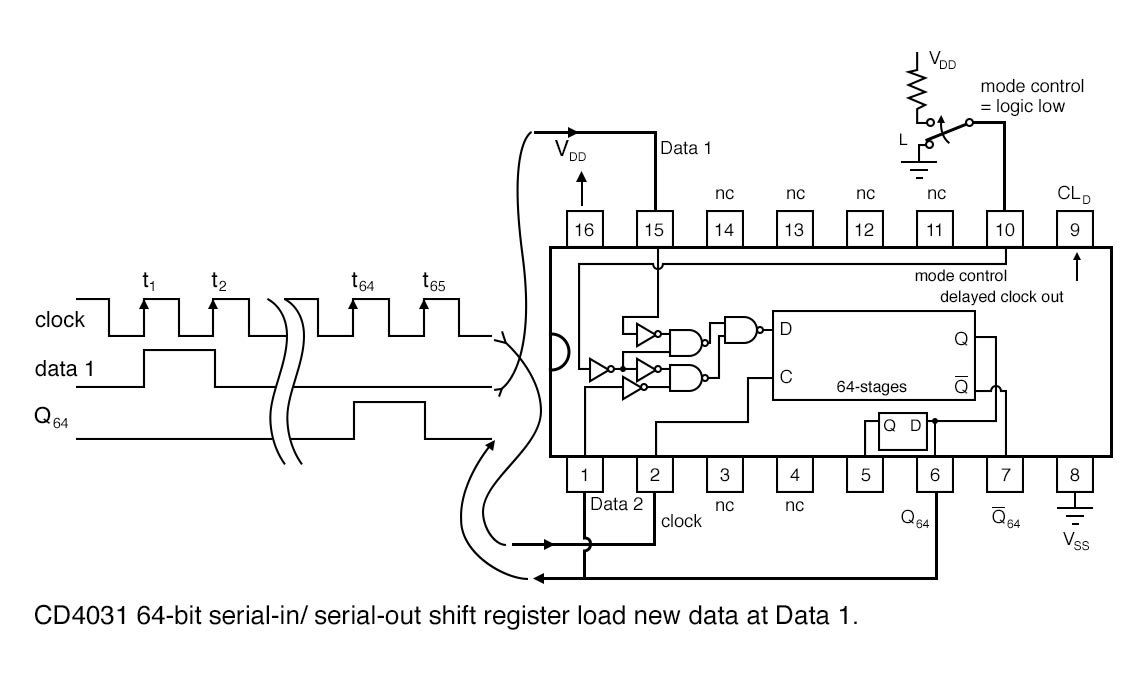

當“模式控制”為低電平時,選擇CD4031“數據1”作為輸入到移位器。輸出Q64不再循環,因為下部數據選擇器門已禁用。“禁用”是指在較低的NAND門上兩次反轉為低電平的邏輯低“模式選擇”阻止其將較低引腳(數據2)上的任何信號傳遞至柵極輸出。因此,它被禁用。

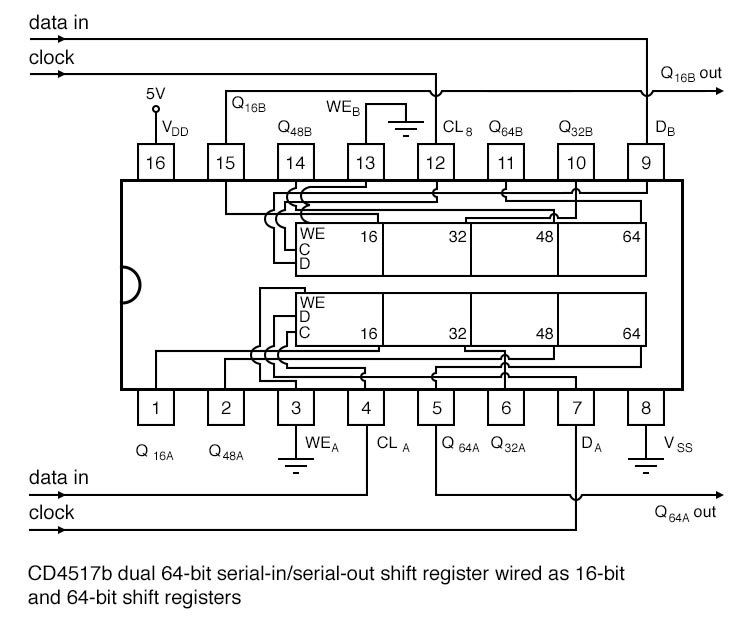

上面顯示了CD4517b雙64位移位寄存器。請注意在第16、32和48階段的抽頭。這意味著可以使用64位移位器之一來配置這些長度的移位寄存器。當然,可以將64位移位器級聯以產生80位,96位,112位或128位移位寄存器。級聯兩個移位器時,時鐘CLA和CLB需要并聯。WEB和WEB為正常變速操作接地。

數據輸入到移位寄存器A和B是d阿和d乙分別。假設我們需要一個16位的移位寄存器。可以用CD4517b進行配置嗎?同一部分的64移位寄存器怎么樣?

上面我們顯示了CD4517b,它被連接為B部分的16位移位寄存器。B部分時鐘CLA。數據在CLB處計時。然后從Q16B提取延遲了16個時鐘的數據。寫入使能WEB接地。上面我們還顯示了與獨立部分A的64位移位寄存器連接的相同CD4517b。對于A部分中的時鐘是CLA。在CL的數據進入A。從Q64A拾取延遲了64個時鐘脈沖的數據。WEA(A部分的寫使能)已接地。

fqj

-

寄存器

+關注

關注

31文章

5343瀏覽量

120365 -

移位器

+關注

關注

0文章

16瀏覽量

8469

發布評論請先 登錄

相關推薦

具有施密特觸發輸入的 SN74HCS164 8 位并行輸出串行移位寄存器數據表

具有施密特觸發器輸入和反相輸出的8位并行輸出串行移位寄存器SN74HCS264數據表

具有施密特觸發輸入的SN74HCS164-Q1汽車類 8位并行輸出串行移位寄存器數據表

高速 CMOS 邏輯8位并行輸入/串行輸出移位寄存器CDx4HC(T)166數據表

CDx4HC165、CDx4HCT165高速CMOS邏輯8位并行輸入/串行輸出移位寄存器數據表

8位串行輸入/串行輸出或并行輸出移位寄存器74LVC595A產品數據表

移位寄存器的功能是什么 移位寄存器的工作原理

8位并行輸入/串行輸出移位寄存器74LV165-Q100數據手冊

詳解移位寄存器,串行輸入和串行輸出的分析

詳解移位寄存器,串行輸入和串行輸出的分析

評論