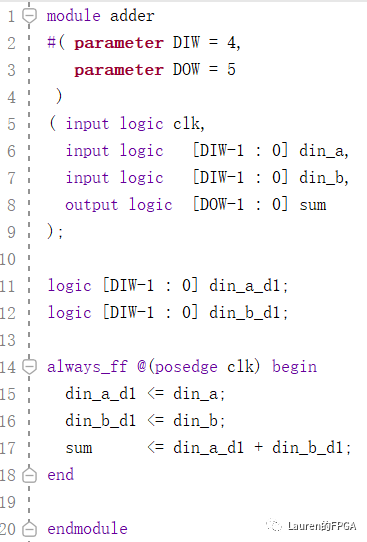

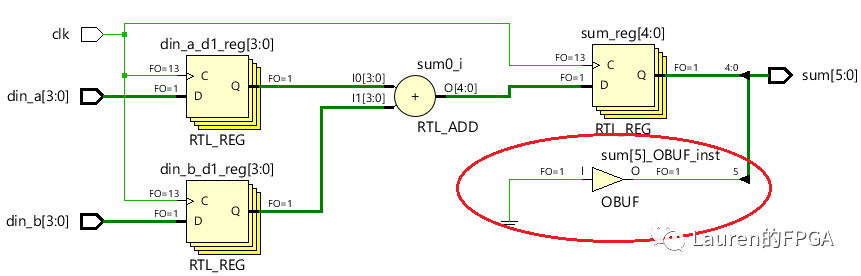

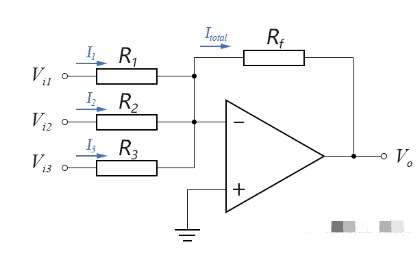

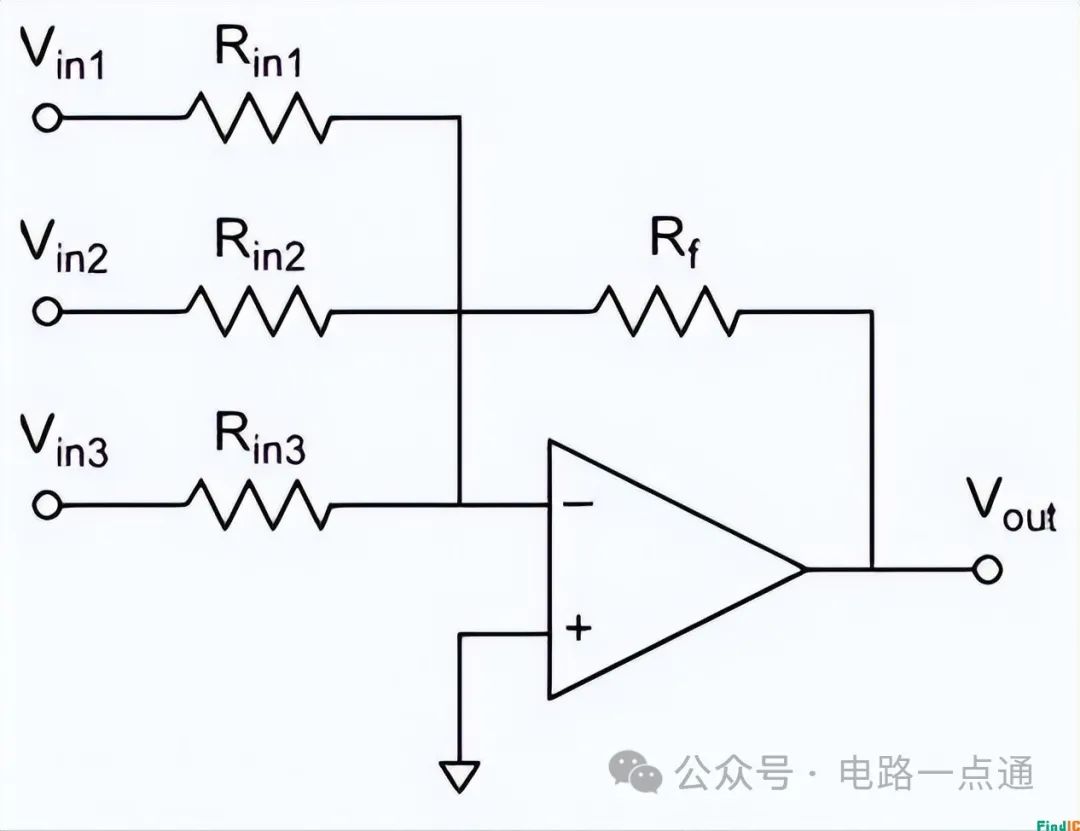

采用HDL代碼描述加法運算只需要用操作符“+”即可,這看似很簡單,這里我們以兩個4-bit數相加為例,對輸入/輸出數據均寄存,從而形成如下圖所示電路。

此電路對應的HDL代碼如下圖所示。這里采用了SystemVerilog語言。有兩點值得注意:一是兩個N位數相加,無論是有符號數還是無符號數,其結果都有可能是N+1位,故輸出比輸入位寬多1位,這樣才能保證不會發生溢出(Overflow)。二是默認情況下,代碼中的logic表示的都是無符號數,但是對于下面這段代碼,無符號數和有符號數均適用,這是因為有符號數是以二進制補碼表示的。

為了進一步說明,我們看如下例子。數據a二進制形式位1001,既可以看作無符號數9(十進制),也可以看作有符號數-7(十進制);數據b二進制形式為1010,既可以看作無符號數10(十進制),也可以看作有符號數-6(十進制)。最終結果的二進制形式為10011,既可以看作無符號數19(十進制),也可以看作有符號數-13(十進制)。

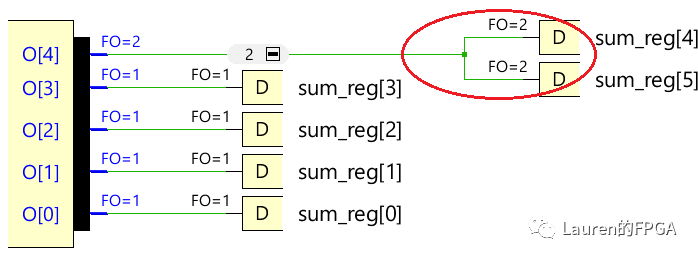

這里兩個4-bit數相加和設置為5-bit,如果和設置為6-bit,有符號數和無符號數的結果是否一致呢?對于無符號數,sum[5]補0,如圖中紅色方框所示。

對于有符號數,sum[5]則是sum[4]的復制版本,實質上是符號位擴展。

本質上,在賦值時,如果把一個N位數據a賦值給一個位寬M的數據b(這里M>N),且兩個數據均為同一類型(都是有符號或無符號),此時是將N位數據做符號位擴展為M位再賦值給b。因此,對于兩個N位數據相加,如果輸出位寬選擇大于N+1,那么上述代碼只適合于無符號數,對于有符號數需要在logic后加關鍵字signed,如下圖所示。

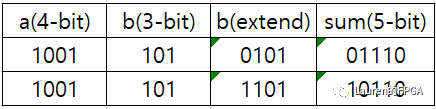

如果兩個位寬不等的數相加,同樣需要指明是有符號數還是無符號數。例如,一個4-bit數和一個3-bit數相加,如下圖所示。如果a二進制為1001,對應無符號數9(十進制),b二進制形式為101,對應無符號數5(十進制),兩個無符號數相加,先將b高位補0,最終和為01110;如果將a和b看作有符號數,則要將b符號位擴展為1101,最終和為10110。符號位擴展是工具完成的,無需人工干預。

總體而言,在描述加法運算時,如果兩個數據均為N位,那么和要設置為N+1位,此時無符號數的描述方式也適合于有符號數。如果兩個數一個是N位,一個是M位,且M>N,那么和要設置為M+1位,此時要明確指出是有符號數還是無符號數。

原文標題:加法運算很簡單?

文章出處:【微信公眾號:Lauren的FPGA】歡迎添加關注!文章轉載請注明出處。

-

電路圖

+關注

關注

10347文章

10721瀏覽量

531005 -

HDL

+關注

關注

8文章

327瀏覽量

47406 -

代碼

+關注

關注

30文章

4791瀏覽量

68694

原文標題:加法運算很簡單?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

邏輯異或運算符在Python中的用法

C語言指針運算符詳解

技術干貨驛站 ▏解鎖C語言高效編程秘訣:深入解析運算符與優先級

技術干貨驛站 ▏深入理解C語言:編程高手必備,全方位解析運算符的核心技能!

用HDL代碼描述加法運算要用操作符“+” 看似很簡單實則不然

用HDL代碼描述加法運算要用操作符“+” 看似很簡單實則不然

評論