前言:多年前,網上出現一組介紹集成電路(芯片)制造的漫畫,而且有英文版。無論從專業角度還是漫畫角度看,筆者認為漫畫畫的很棒!可惜網上漫畫清晰度不高。筆者對這些漫畫進行了清晰化,并配上了通俗的說明文字和示意圖,整理成此文,試圖以漫畫為主、示意圖和文字為輔,對芯片制造過程進行講解。重點介紹在芯片上集成上百億只電路元件的“十八般武功”,力求形象生動和便于理解。網上引用這組漫畫的文章都未標出漫畫原創作者,若讀者有相關信息,請不吝賜教。筆者核實后,將在文中列出漫畫原創作者。

小小芯片把人類帶進信息化智能化世界,芯片和軟件構成了信息化社會這座高樓大廈的基礎。如果您對芯片還比較陌生,但近兩年來,您已經知道了芯片超級重要后,一定想多了解一些芯片知識。下文將用漫畫、示意圖和說明等形式,通俗直觀地對芯片及其制造過程進行介紹。

示意圖1帶您認識一下用于制造芯片的硅片(晶圓),實現芯片功能的最小單元——晶體管,以及硅片、芯片和晶體管三者的關系。圖中麒麟990是華為先進的5G智能手機芯片,采用7nm工藝制造,面積僅為113平方毫米(約1厘米見方,小手指甲大小),上面卻集成了約103億只晶體管。一只晶體管的三維(3D)結構如右上圖所示。芯片制造廠采用的12英寸硅片的面積為70659平方毫米,用它大約可以生產600顆麒麟990芯片。

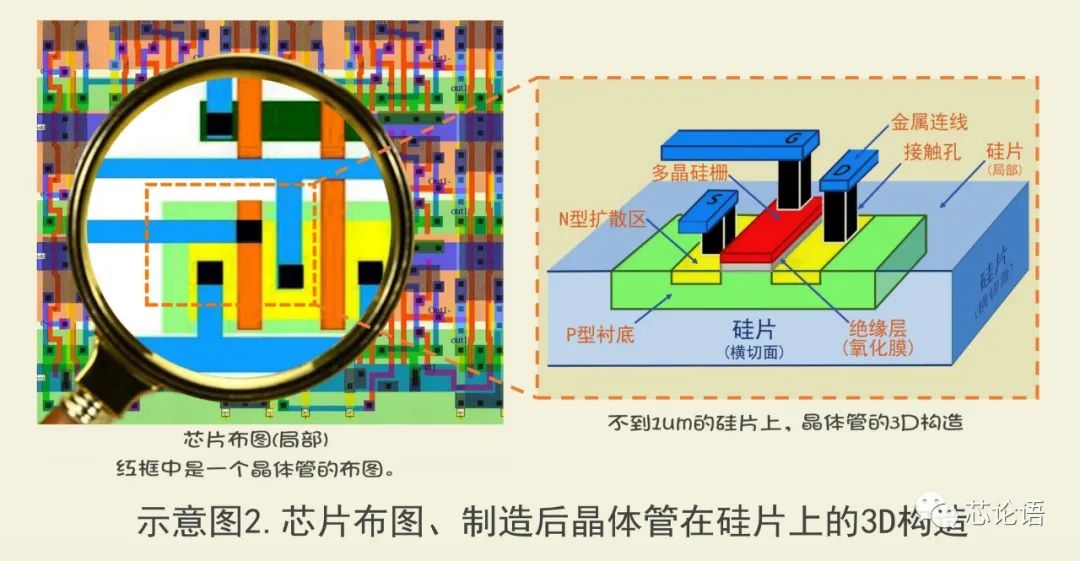

示意圖2左圖是一張芯片布圖(Layout)的局部,把它放大后,在其中找到了一個晶體管的布圖,如紅方框區域所示。一個晶體管在芯片中僅占頭發絲橫切面百分之一不到的面積,但它卻是由復雜的電路結構組成。晶體管從分布上看是平面的,但從橫切面上看是立體的,晶體管三維立體結構如上右圖所示。芯片制造完成后,晶體管會“依托”硅片并“扎根”于硅片,上百億只晶體管由縱橫而不交錯的金屬線條連接起來,實現了芯片的功能。

如何在小手指甲大小的硅片上集成上百億只晶體管等電路?在芯片制造時都用到了哪些高精尖的技術?下面就讓機器人小寶帶您走進芯片制造的微觀世界,看看集成電路制造的神奇。

芯片細微無法言表,漫畫粗曠只能示意。

一、芯片制造過程概述

芯片制造過程大致分為四個階段。下圖中,1-2的工序是芯片設計流程,3-4-5-6的工序是硅片制造流程,7-8-9-10-11的工序是在硅片上制造電路元件的電路制造流程,12-13的工序是收尾流程。其中,硅片制造流程實際是芯片原材料加工過程,一般是在另外的專業工廠中完成。所以,硅片制造可以不包括在芯片制造過程中。本文為了讓讀者對芯片制造有全局了解,特把硅片制造也包含在芯片制造過程中。

(注:此漫畫及后文所有漫畫皆來源于網絡文章,并經過了筆者加工整理。)

(一)芯片設計流程

芯片設計流程中包括了電路設計和光刻掩膜版制作。電路設計就是通常所說的集成電路設計(芯片設計),它是芯片產業鏈(設計、制造、封裝、測試和應用)的首要環節,電路設計的結果是芯片布圖(Layout)。光刻掩膜版制作是把芯片布圖拆分成幾十層~上百層用于制造芯片的圖紙,并把每層圖紙制作成光刻掩膜版(Mask),它們將在芯片制造過程中使用。假設一個芯片布圖拆分為n層光刻掩膜版,硅片上的電路制造流程各項工序就要循環n次。

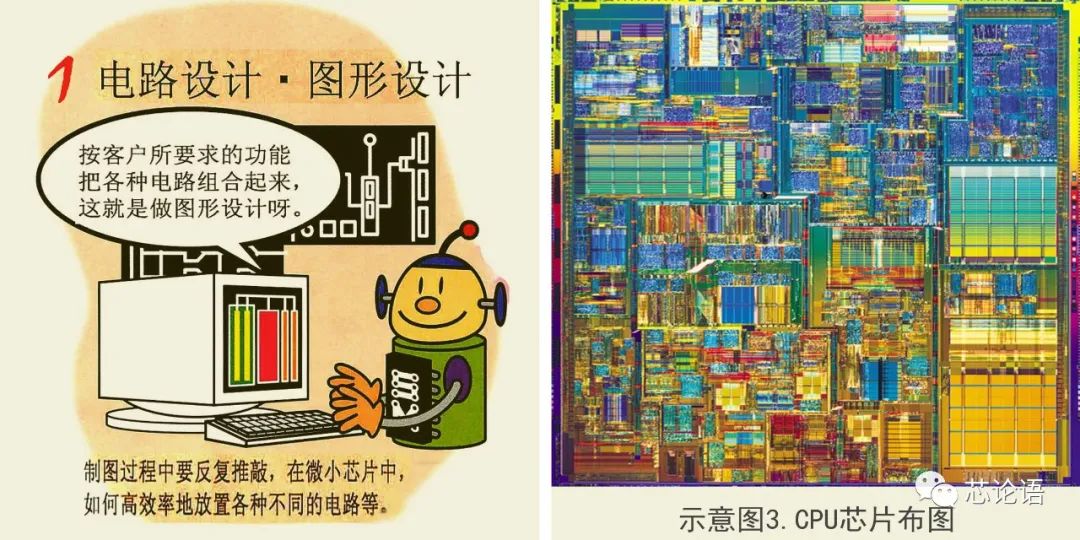

1.電路設計:這是晶體管等電路元件擺放、連線和模擬的“設計功”。設計人員要在圖形工作站上,利用EDA軟件,把上百億只晶體管等電路元件合理擺放(Place)在設計區域,上下左右、縱橫而不交錯地準確連接(Route)起來,從而實現預想的電路功能。并且芯片布圖在送去制造之前,要反復進行精確地電路功能模擬(Simulation),以保證芯片設計萬無一失。

示意圖3是Intel公司2000年發布的奔騰P4 CPU的芯片布圖,該芯片采用180nm的工藝制造,其上集成了4200萬只晶體管,該芯片是臺式計算機的CPU。20年后的今天,華為手機CPU芯片麒麟990采用7nm工藝制造,集成了103億只晶體管,規模是Intel P4的245倍,并且速度更快。現在智能手機的處理能力比二十年前的臺式計算機要強很多倍,芯片技術的快速發展功不可沒。

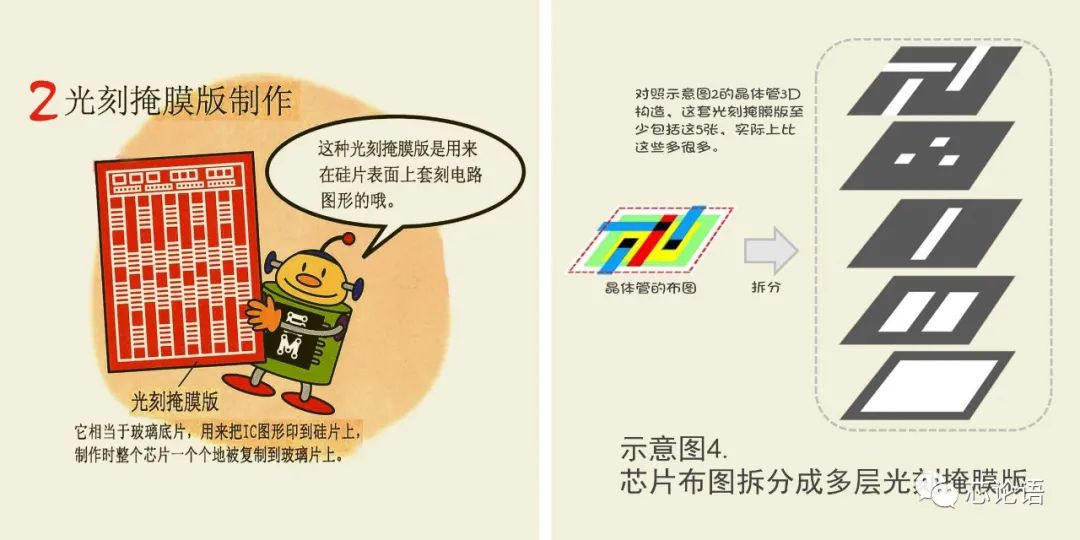

2.光刻掩膜版制作:這是把芯片布圖拆分成光刻掩膜版的“分層功”。這個工序是芯片制造前的準備工作,分層就是按照芯片制造的工藝要求,把芯片布圖拆分成多達幾十層的光刻掩膜圖形,并制成一層層的光刻掩膜版。傳統光刻掩膜版是在很薄很平整的石英玻璃上沉積一層厚約150nm的鉻膜,并按光刻圖形做出透光與不透光的圖形。

示意圖4是一個晶體管(示意圖2所示)的一套光刻掩膜版圖,如果芯片上集成上百億只晶體管的話,光刻掩膜版上圖形數量將是它一百多億倍,復雜程度可想而知。光刻掩膜版類似于傳統照相底版,它上面的圖形只有透光和不透光的分區,并精細的多。而照相底版有半透光的過渡性區域,而且精度無法和光刻掩膜版相提并論。

(二)硅片制造流程

硅片制造流程包括了單晶硅棒拉制、硅棒切片、硅片研磨和硅片氧化共4個工序。硅片也叫晶圓,硅片制造也叫做硅晶圓制造。硅片制造一般是在另外的專業工廠完成,然后以原材料產品形式出售給芯片制造廠。硅片典型直徑尺寸有4英寸(100mm)、6英寸(150mm)、8英寸(200mm)和12英寸(300mm)。

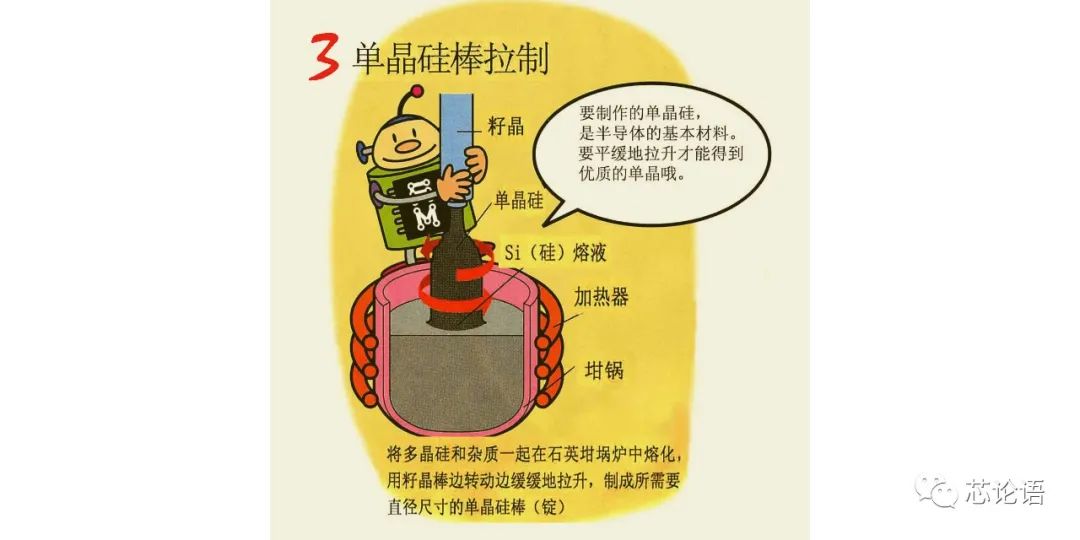

3.單晶硅棒拉制:多晶硅到單晶硅的“單晶生長功”。根據晶核排列是否同向,硅材料可分為單晶硅和多晶硅,半導體行業使用單晶硅,而且純度要求為99.999999999%以上(業內簡稱 11N)。單晶硅棒拉制就是在多晶硅溶液中放入籽晶棒,在熔體溫度、提拉速度、籽晶/石英坩堝的旋轉速度等合適的條件下,隨著籽晶棒邊轉動邊緩緩地拉升,溶液中的晶核沿籽晶同向生長,一個以籽晶棒為中心的單晶硅棒就拉制出了。硅棒直徑與條件控制和提拉速度有關。

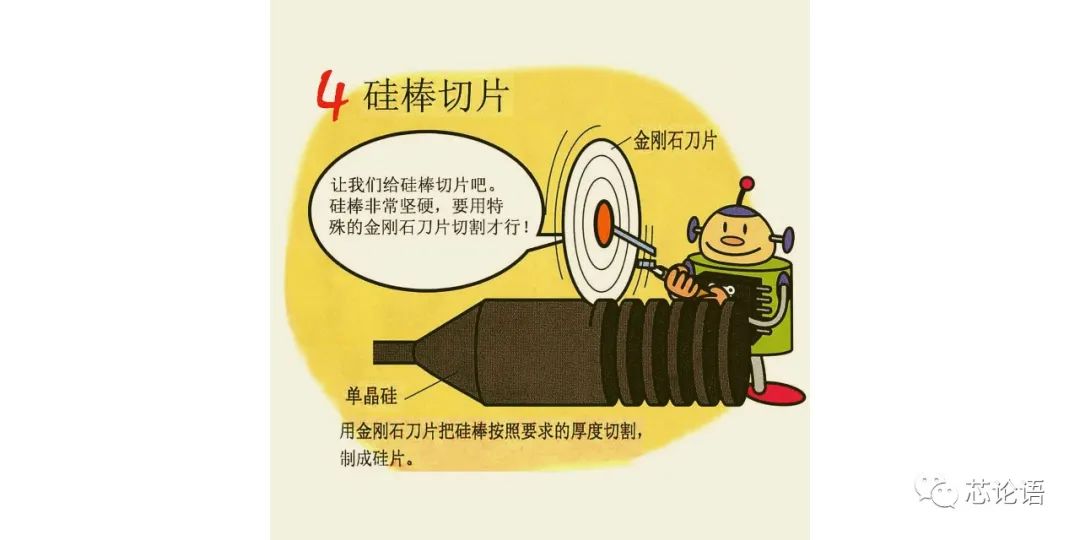

4.硅棒切片:硬碰硬地切片,要有切得很薄的“刀功”。這道工序是把硅棒切割成硅片。由于硅棒直徑和應用不同,硅棒切片的厚度也有差別。半導體用的硅片的切片厚度在450μm~750μm范圍,太薄易脆裂不適合芯片制造。但太陽能用的硅片卻是越薄越好,切片厚度僅為200μm左右(約2根頭發絲的厚度),切割縫隙在120μm左右。由于硅棒非常堅硬,又要切的很薄,很考驗設備的“刀功”。常見的硅棒切片方法為金剛線切割法和砂線切割法。

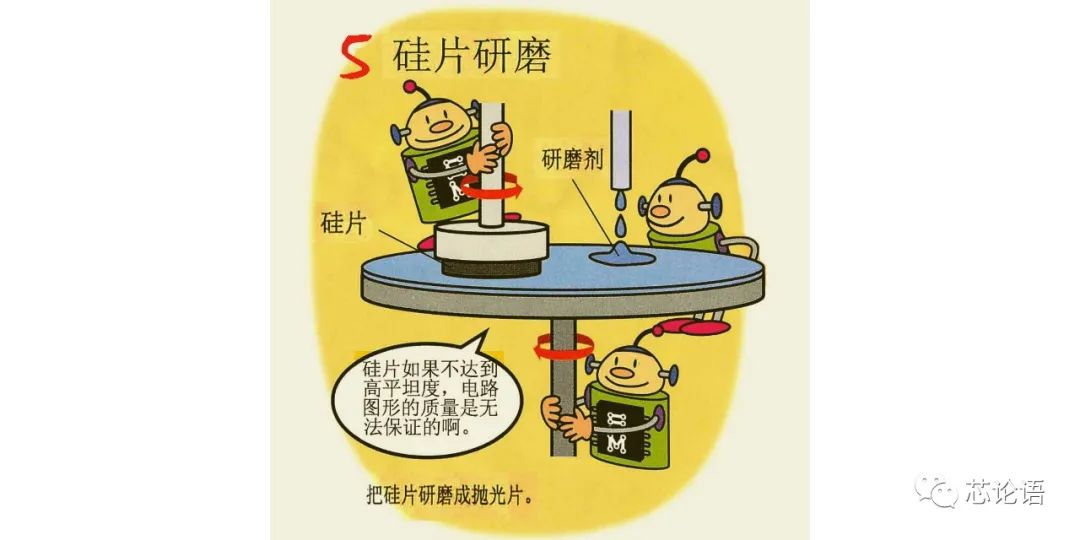

5.硅片研磨:一絲不茍的“磨平功”。成語中的“絲”如果是指頭發絲的話,我這句話還應改為“萬分之一絲不茍的‘磨平功’”。因為,半導體用的大硅片表面局部平整度(SFQD)要求小于設計線寬的2/3,如果大硅片用來制造14nm工藝的芯片,SFQD要求控制在10nm以內,即頭發絲的萬分之一。若選用7nm工藝,SFQD應小于5nm,硅片平整度要求更高。這道工序對研磨劑和研磨機都提出了很高的技術要求。

6.硅片氧化:讓半導體不導電的“絕緣功”。半導體硅片可以經過加工變成導體,也可以經過加工變成絕緣體。這道工序是在硅片上生成一層很薄的氧化膜,使硅片表面成為絕緣體,為其后在硅片上制作電路元件做準備。氧化膜的成份是SiO2,具有良好的化學穩定性和電絕緣性,可用于晶體管柵極氧化膜、電絕緣層、電容器介質和屏蔽層等。硅片氧化工序還將在電路制造流程中多次應用,如果先做光刻再做氧化,將會在指定區域生成氧化膜,形成局部的絕緣保護。

(三)電路制造流程

準備好了硅片和光刻掩膜版,芯片制造就進入到了硅片表面電路制造的流程。該流程中包括了光刻膠涂布、硅片表面上圖形形成、刻蝕、氧化、擴散、CVD、粒子注入和平坦化等工序。電路制造流程是一個循環流程,芯片成套的光刻掩膜版有多少層,這個流程就要循環多少次。每層光刻掩膜版表達的圖形內容不同,流程中的個別工序也有可能被跳過。

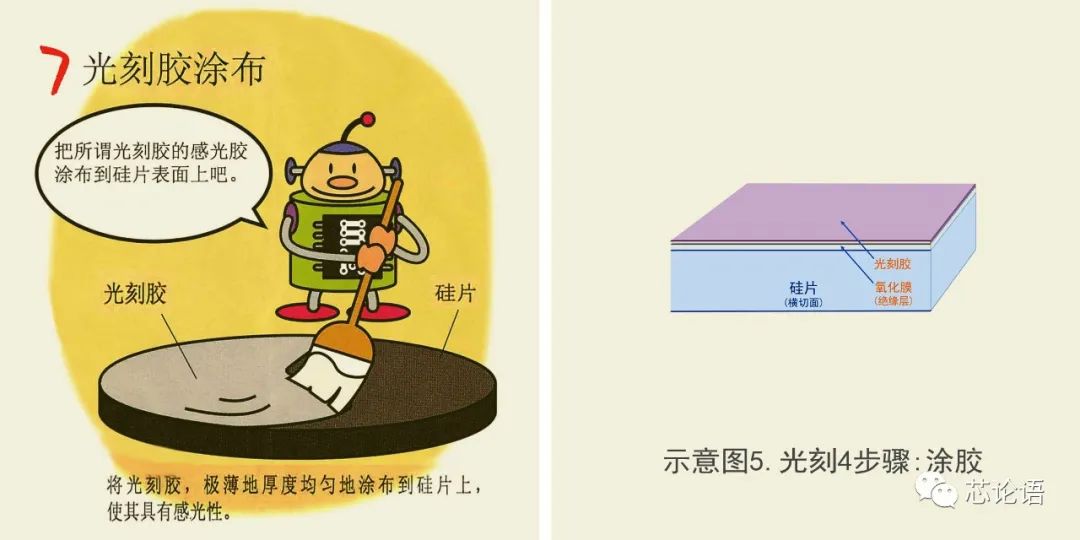

7.光刻膠涂布:在硅片上涂布光刻膠要有很好的“均勻功”。一般旋轉涂布光刻膠的厚度與***曝光的光源波長有關(不同級別的曝光波長對應不同的光刻膠種類和分辨率)。厚度一般在200nm~500nm的范圍。光刻膠是芯片制造的重要原材料,2019年7月日本為了抗議韓國法院對“韓國勞工”裁決,就用了光刻膠等原材料卡韓國的“脖子”,使韓國芯片產業一度困難。

示意圖5是一小塊硅片上的硅片基底、氧化膜和感光膠的三層結構示意圖。

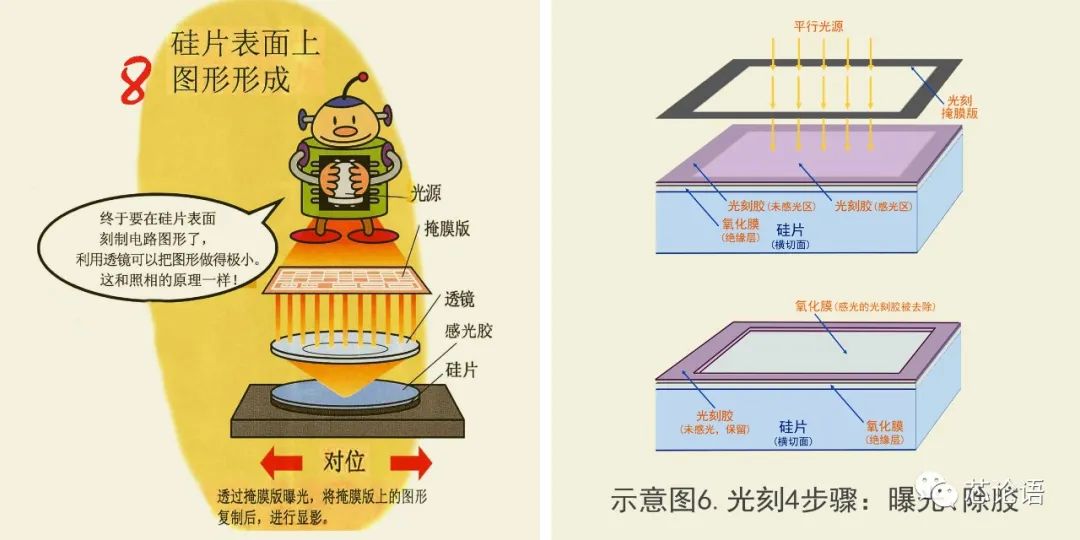

8.硅片表面圖形形成:像傳統照片洗印一樣的“精準曝光功和洗印功”。這道工序用來把光刻掩膜版上的圖形投影到已涂布好的光刻膠上,進行精準曝光。這項工作由大名鼎鼎的***來完成。在曝光之后,接下來要除去感光了的光刻膠,留下了未感光的光刻膠(假定使用了正性感光膠)。光刻掩膜版上的電路圖形就精確地以光刻膠圖形“做”在硅片的氧化膜上了。

示意圖6是光刻工藝中的曝光(上圖)和除膠(下圖)工序示意圖,等同于傳統照相過程中的曝光和洗印。感光膠有正負之分,感光的正性感光膠在顯影除膠工序中被除去,保留了未被感光的部分。負性感光膠相反,未被感光的部分被除去,保留了被感光的部分。

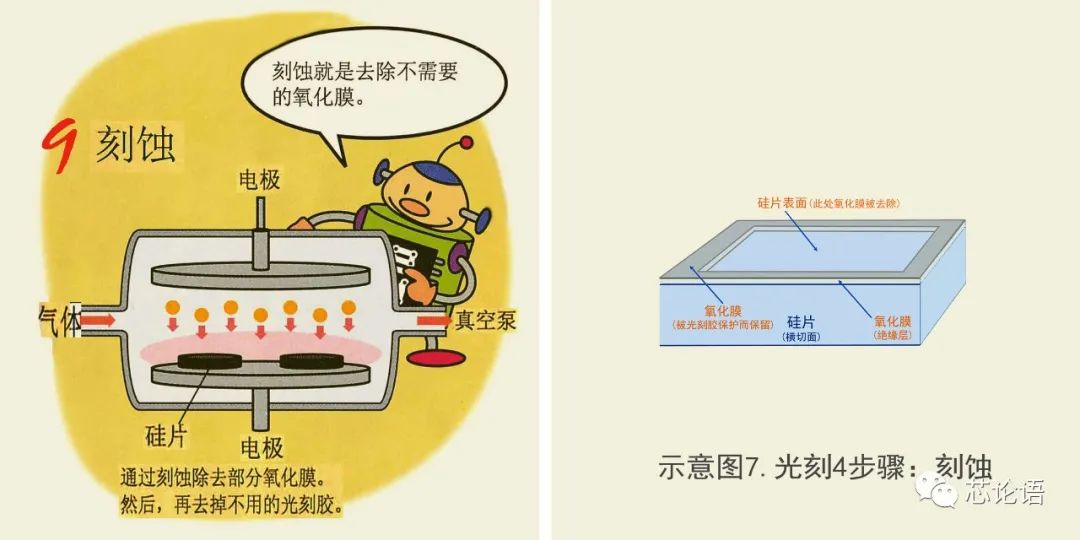

9.刻蝕:對光刻膠圖形下的氧化膜進行“精準雕刻”。這道工序用來把光刻膠覆蓋的氧化膜保留,其它部分去掉。然后再把其余的光刻膠去除。這時,光刻掩膜版上的電路圖形就精確地以氧化膜形式“做”在了硅片上。這項工作由刻蝕機來完成。工序7、8、9組成了芯片制造流程中最重要的光刻工藝(也稱為平面加工工藝)。

示意圖7是把晶體管的第一張光刻掩膜版(示意圖4)上的電路圖形制作在氧化膜上的示意。同理,電路圖形也可以制作在柵極多晶硅膜、絕緣鈍化膜、蒸鋁連線層上等。

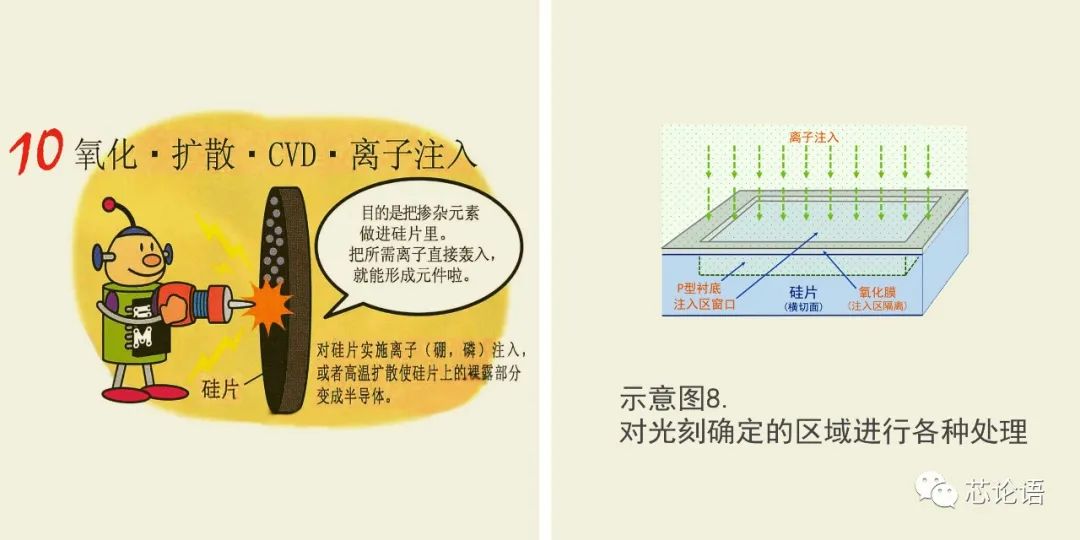

10.氧化、擴散、CVD和粒子注入:這是在硅片上“分區精加工的硬功”。使用上述工序7、8、9的光刻工藝后,就可以在芯片的上指定區域進行多種精加工。氧化是在指定區域生成氧化膜;擴散是對指定區域定量摻入其它元素原子,改變該區域的電性能;CVD是在指定區域沉積一層氧化硅、碳化硅、多晶硅等半導體材料層;離子注入是向指定區域定量注入雜質的原子或粒子,使該區域的電性能發生變化。

示意圖8是制作晶體管的P型襯底(示意圖2綠色區)的示意圖。前道的光刻工藝在氧化膜上開了一個離子注入窗口,在這道精加工的工序中進行離子注入,使窗口下的硅片變為P型襯底。

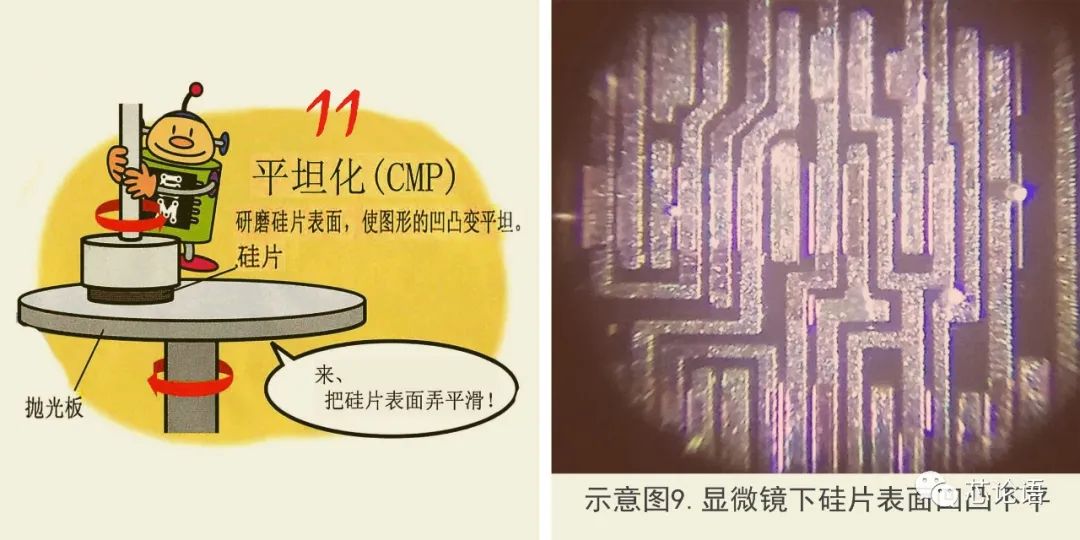

11.平坦化:電路圖形表面“精確磨平功”。在硅片上做了幾層電路圖形的“光刻”和“加工”循環(工序7、8、9、10)以后,有些地方刻蝕下去,有些地方生長上來,電路圖形表面已變得凹凸不平。為了進行下一層的“光刻”和“加工”循環流程,首先要對電路圖形表面進行平坦化。平坦化打磨要十分精確,打磨太深會損壞已做好的電路圖形,打磨太淺電路圖形表面依然不夠平整。平坦化工序完成后,跳回到工序7的光刻膠涂布,按照下一張光刻掩版開始下一循環的“光刻”和“精加工”過程。

示意圖9是高倍電子顯微鏡下看到的凹凸不平下層電路圖形。

(四)收尾流程

收尾流程中包括了電極形成和硅片檢查兩道工序,這是芯片制造最后的收尾工序,之后就可以進行芯片封裝了。

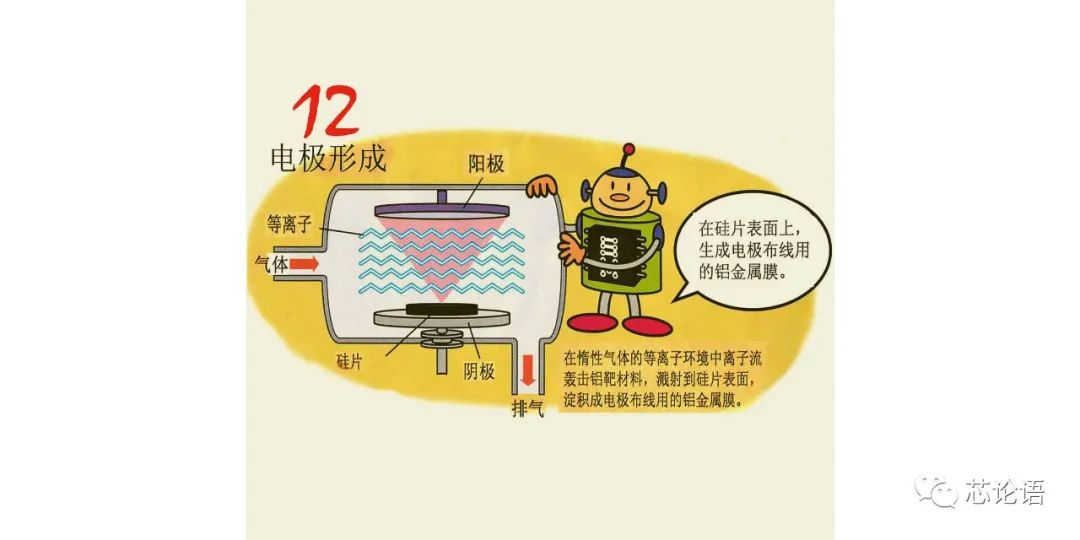

12.電極形成:金屬材料蒸發和淀積的“金屬化功”。在電路制造循環完成之后,還要完成一層晶體管等電路元件表層的鋁金屬連線,并要把芯片引出電信號的連接電極做好。把鋁、銅等金屬蒸發成氣體,傳送到芯片表面,并淀積生成一層金屬薄膜叫做金屬化工藝,金屬化是一項難度很大的技術功夫。

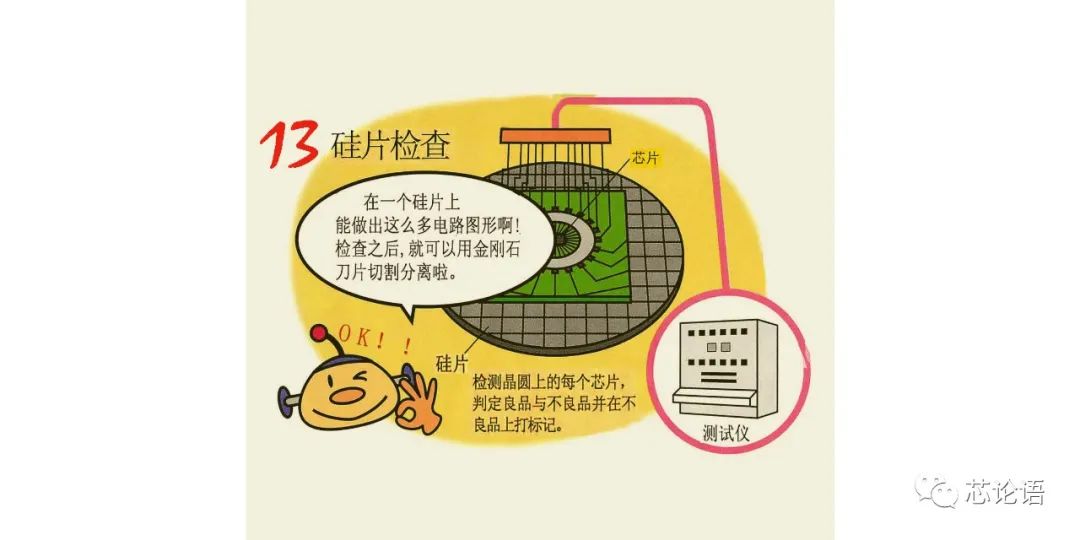

13.硅片檢查:從批量芯片中找出不良芯片的“火眼金睛功”。在芯片封裝之前,要對硅片上成百上千的芯片進行檢查,標記出不良的芯片,以便在后續的芯片封裝時棄之不用。

二、芯片封裝流程概述

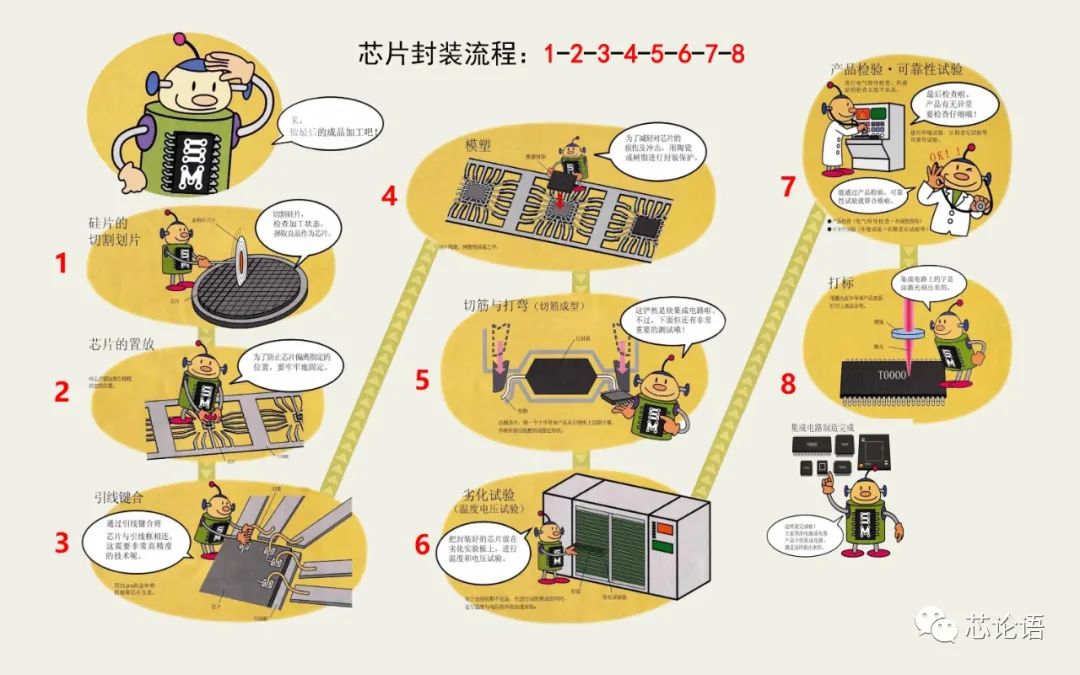

芯片封裝流程包括了硅片切割、芯片置放、引線鍵合、塑封模壓、切筋成型、劣化試驗、產品檢驗、激光打標八個工序,如下圖所示。該封裝流程封裝的芯片都是四邊引線的塑料封裝(包括DIP、SOP、QFP、PQFP、LCC、PLCC等),這是傳統的二維(2D)封裝形式,本文對其中的每道工序不做詳細介紹。

(注:此漫畫來源于網絡文章,并經過了筆者加工整理。)

示意圖10是目前芯片封裝形式的全景圖。分割線左側是傳統的2D塑料封裝形式,右側是更先進的新型封裝形式,包括:以陣列引腳封裝(PGA)、球柵陣列封裝(BGA)、觸點陣列封裝(LGA)等為代表的球陣封裝;晶圓級封裝(WLP);系統級封裝(SIP);堆疊封裝(PoP);多芯片組封裝(MCP)和芯片級封裝(CSP)等。其中除了球陣封裝外,其它都屬于系統級或者三維(3D)先進封裝。而且隨著技術進步,新型封裝技術將不斷推陳出新,以滿足各種新的應用需求。

(注:此圖片來源于網絡:今日半導體,并經過了筆者加工整理。)

結語:芯片設計和硅片生產是芯片制造的前期準備,電路制造有三個重點內容要了解,一是硅片上的電路是按光刻掩膜版的順序,一層層用光刻平面工藝循環加工而成,芯片上的電路元件是立體的。二是光刻工藝有4個步驟:涂膠、曝光、除膠、刻蝕,光刻是芯片技術的核心。三是每一循環加工都是由光刻和加工兩個階段組成,光刻指定了后續加工的范圍、區域和窗口,后續加工是對硅片上材料真正的處理過程,包括氧化、擴散、CVD、離子注入、鈍化等處理。

在芯片制造過程中,芯片設計階段用到了電路元件擺放、連線和功能模擬的“設計功”、把芯片布圖拆分成光刻掩膜版的“分層功”;硅片生產階段用到了“單晶生長功”、“硅棒切片功”、“硅片磨平功”和“半導體絕緣功”;在電路制造階段用到了光刻的“精準定位功”和“精細加工功”;在芯片封裝階段也有各種各樣的真功夫。芯片制造中的真功夫是芯片高技術含量的具體體現。用漫畫把這些真功夫都一一表達出來,其實是一件很難的事情。在此,筆者向文中所引用漫畫原創作者致敬。

責任編輯:xj

原文標題:【芯論語】漫畫在芯片上“集成”上百億只“電路”元件的“十八般武功”

文章出處:【微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

-

芯片

+關注

關注

455文章

50816瀏覽量

423617 -

電路元件

+關注

關注

0文章

115瀏覽量

11041

原文標題:【芯論語】漫畫在芯片上“集成”上百億只“電路”元件的“十八般武功”

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ASIC集成電路與通用芯片的比較

什么是專用集成電路 通信專用集成電路有哪些類型

專用集成電路設計流程是什么 專用集成電路的特點有哪些

專用集成電路包括什么和什么兩種 專用集成電路包括什么功能設備

專用集成電路的設計流程有哪些 專用集成電路包括什么功能和作用

專用集成電路 通用集成電路有哪些區別 專用集成電路和通用集成電路的區別與聯系

專用集成電路技術是什么技術 通用和專用集成電路區別

專用集成電路芯片類型是什么

專用集成電路 通用集成電路區別在哪

通用集成電路和專用集成電路按什么分類

芯片、半導體、集成電路傻傻分不清?芯片和集成電路有什么區別?

集成電路制造的起源和發展

集成電路(芯片)制造的短篇漫畫

集成電路(芯片)制造的短篇漫畫

評論