引言

近來,幾乎每個賽靈思 IP 都使用 AXI 接口。Zynq?、Zynq MP、MicroBlaze? 和全新的 Versal? 處理器都無一例外使用 AXI 接口。因此,AXI 接口已成為幾乎所有新的賽靈思器件設(shè)計中不可或缺的一部分。充分了解其基礎(chǔ)知識對于賽靈思器件的設(shè)計和調(diào)試都很有幫助。

本篇博文將介紹賽靈思器件上的 AXI3/AXI4 的相關(guān)基礎(chǔ)知識。首先,我們將從一些通俗易懂的知識、理論和術(shù)語開始講解。

何謂 AXI?

AXI表示Advanced eXtensibleInterface(高級可擴展接口),它是由Arm定義的接口協(xié)議,包含在“高級微控制器總線架構(gòu)AMBA”標(biāo)準(zhǔn)中。

AXI3/AXI4規(guī)格可通過Arm網(wǎng)站免費獲取(鏈接),因此如果您對其感興趣,我鼓勵您務(wù)必下載。

AXI4 接口 (AMBA 4.0) 分 3 種類型:

AXI4 (AXI4-Full):用于滿足高性能存儲器映射需求。

AXI4-Lite:用于簡單的低吞吐量存儲器映射通信(例如,往來于狀態(tài)寄存器的通信)。

AXI4-Stream:用于高速流傳輸數(shù)據(jù)。

注:本文不涵蓋 AXI4-Stream 相關(guān)內(nèi)容。此處“AXI”表示 AXI3、AXI4 和 AXI4-Lite。

注:AXI3 接口與 Full AXI 接口接近。

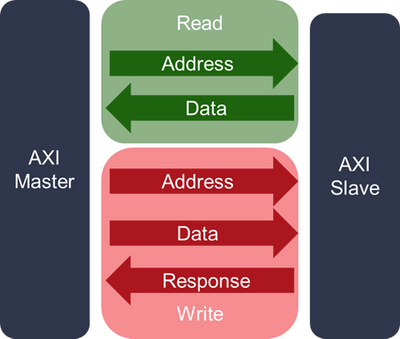

AXI 讀寫通道

AXI 協(xié)議定義了 5 條通道:

其中 2 條用于讀取傳輸事務(wù)

讀地址

讀數(shù)據(jù)

另 3 條用于寫入傳輸事務(wù)

寫地址

寫數(shù)據(jù)

寫響應(yīng)

通道 (channel) 是與 VALID 和 READY 信號關(guān)聯(lián)的 AXI 信號的獨立集合。

注:AXI4/AXI3/AXI4-Lite 接口只能用于讀取(僅包含 2 條讀取通道)或者只能用于寫入(僅包含 3 條寫入通道)。

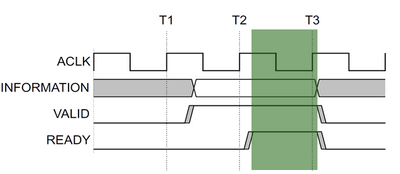

任一通道上發(fā)射的每一條數(shù)據(jù)都稱為一次傳輸 (transfer)。當(dāng) VALID 和 READY 信號均居高不下并且時鐘存在上升沿時,就會發(fā)生傳輸。例如,在下圖中,在 T3 處正在發(fā)生傳輸:

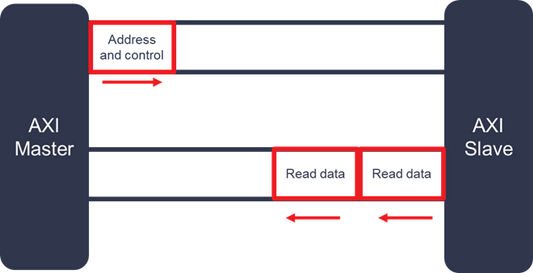

AXI 讀取傳輸事務(wù)

AXI 讀傳輸事務(wù)需要在 2 條讀取信道上發(fā)生多次傳輸。

首先,地址讀通道 (Address Read Channel) 從主設(shè)備 (Master) 發(fā)送到從設(shè)備 (Slave),以便設(shè)置地址和部分控制信號。

然后,此地址的數(shù)據(jù)通過讀數(shù)據(jù)通道 (Read data channel) 從從設(shè)備發(fā)送到主設(shè)備。

請注意,根據(jù)下圖所示,每個地址中可發(fā)生多次數(shù)據(jù)傳輸。此類型的傳輸事務(wù)稱為突發(fā) (burst)。

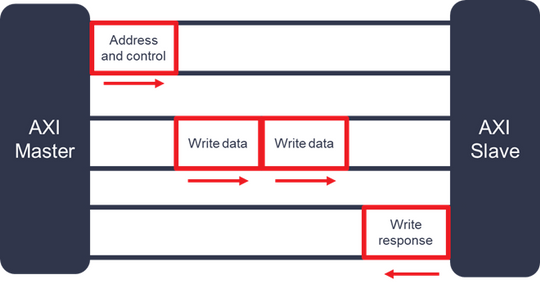

AXI 寫入傳輸事務(wù)

AXI 寫入傳輸事務(wù)需要在 3 條讀取信道上存在多次傳輸。

首先,寫地址通道 (Address Write Channel) 從主設(shè)備發(fā)送到從設(shè)備,以便設(shè)置地址和部分控制信號。

然后,此地址的數(shù)據(jù)通過寫數(shù)據(jù)通道 (Write data channel) 從主設(shè)備發(fā)射到從設(shè)備。

最后,寫入響應(yīng)通過寫響應(yīng)通道 (Write Response Channel) 從從設(shè)備發(fā)送到主設(shè)備,以指示傳輸是否成功。

寫響應(yīng)通道 (Write Response Channel) 上可能的響應(yīng)值包括:

OKAY (0b00):正常訪問成功。表示已成功完成正常訪問

EXOKAY (0b01):專屬訪問成功。

SLVERR (0b10):從設(shè)備錯誤。已成功訪問從設(shè)備,但從設(shè)備希望向發(fā)端主設(shè)備返回錯誤條件(例如,數(shù)據(jù)讀取無效)。

DECERR (0b11):解碼器錯誤。通常由互連組件生成,用于指示傳輸事務(wù)地址處沒有任何從設(shè)備

注:讀取傳輸事務(wù)同樣包含響應(yīng)值,但此響應(yīng)通過讀響應(yīng)通道 (Read Response Channel) 來發(fā)射

AXI4 接口要求

在 AXI4 規(guī)格中記錄了部分要求。

最值得注意的是:

斷言 VALID (AxVALID/xVALID) 信號時,它必須保持處于已斷言狀態(tài)直至從設(shè)備發(fā)出 AxREADY/xREADY 斷言后出現(xiàn)上升時鐘沿為止。

發(fā)送信息的 AXI 接口的 VALID 信號不得從屬于接收該信息的 AXI 接口的 READY 信號。

但是,READY 信號的狀態(tài)可從屬于 VALID 信號

寫響應(yīng)必須始終位于所屬的寫入傳輸事務(wù)中最后一次寫入傳輸之后

讀數(shù)據(jù)必須始終位于數(shù)據(jù)相關(guān)的地址之后

從設(shè)備必須等待發(fā)出 ARVALID 和 ARREADY 斷言后,才能發(fā)出 RVALID 斷言以指示該有效數(shù)據(jù)可用

-

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

131280 -

AXI

+關(guān)注

關(guān)注

1文章

127瀏覽量

16631 -

AXI4

+關(guān)注

關(guān)注

0文章

20瀏覽量

8894

發(fā)布評論請先 登錄

相關(guān)推薦

AXI VIP設(shè)計示例 AXI接口傳輸分析

如何使用AXI VIP在AXI4(Full)主接口中執(zhí)行驗證和查找錯誤

XILINX FPGA IP之AXI Traffic Generator

看看在SpinalHDL中AXI4總線互聯(lián)IP的設(shè)計

AXI4接口協(xié)議的基礎(chǔ)知識

一文詳解ZYNQ中的DMA與AXI4總線

ZYNQ中DMA與AXI4總線

深入AXI4總線一握手機制

關(guān)于AXI4-Stream協(xié)議總結(jié)分享

AXI4 、 AXI4-Lite 、AXI4-Stream接口

AXI3與AXI4寫響應(yīng)的依賴區(qū)別?

FPGA AXI4協(xié)議學(xué)習(xí)筆記(二)

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

SoC設(shè)計中總線協(xié)議AXI4與AXI3的主要區(qū)別詳解

何謂 AXI?關(guān)于AXI3/AXI4的相關(guān)基礎(chǔ)知識

何謂 AXI?關(guān)于AXI3/AXI4的相關(guān)基礎(chǔ)知識

評論