作者:貓叔

git有多好用我就不用多說了,可謂是程序員必備技能之一。對于一般的軟件代碼來說,只需把源文件進行git管理即可。但對于FPGA工程師來說,使用git多多少少有些蛋疼,主要有下面幾個問題:

① 有bd文件的工程中,只把bd文件加入git是不行的;

② 很多公司都會有一些積累下來的hdl文件,放到某個文件夾中,所有的工程目錄下都會有這個文件夾,因此這個文件中會有很多不是當前工程的文件,因此git的文件中,必須包含當前工程的files list,否則就得重新添加文件;

③ 如果把整個Vivado工程都放入git,非必要文件太多,既浪費git服務器的空間,Push和Pull的速度也會很慢;

④ 很多FPGA工程師有自己的一套git管理Vivado的流程,但每次push前和Clone后都需要做很多操作。

最近我也一直在研究Vivado工程git的管理方式,查了網上很多方法,但有些操作略復雜,有些方法完全不起效,但好在最終綜合整理出了一種相對簡單的方式進行,也許這種方式不是最合適的,如果你有更好的方法,希望能分享出來。

我們這篇文章只講Vivado的工程,不包括HLS或者Sdk工程,因為這這兩個工具都是純C/C++/TCL的,git管理起來比較簡單

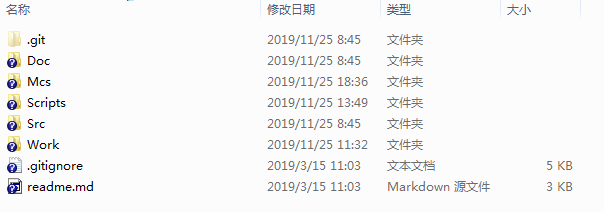

1. 工程目錄

我們采用如下的目錄結構,這種方式也是Xilinx官網某個教程上推薦的,

Work目錄:Vivado的工程全都放在Work目錄下,包括bd以及它的相關文件;

Src目錄:放hdl的源文件以及IP Core的源文件;

Doc目錄:放跟工程相關的文檔,如果沒有的話可以不加;

Mcs目錄:放工程生成的bit和mcs文件,這個文件也看個人用途,如果覺得bit文件太大不想放在git上也無所謂,但個人覺得在調試的時候經常會用到之前測試好了某個bit;

Scripts目錄:也是進行git管理的關鍵,里面放各種Tcl腳本;

如果工程中有SDK/HLS/SsyGen,可以在該目錄下再增加文件夾專門放置對應的工程文件。

2. 操作步驟

1. 在打開的Vivado工程中,通過Tcl Console將目錄切換到Work目錄:

cd [get_property directory [current_project ]]

2. 生成新建工程的Tcl腳本,執行:

write_project_tcl {./Scripts/s1_recreate_project.tcl}

3. 依次生成bd文件的tcl腳本,比如工程中有兩個bd文件aa.bd和bb.bd,打開aa.bd,并執行:

write_bd_tcl {./Scripts/s2_aa_bd.tcl}

打開bb.bd,并執行:

write_bd_tcl {./Scripts/s3_bb_bd.tcl}

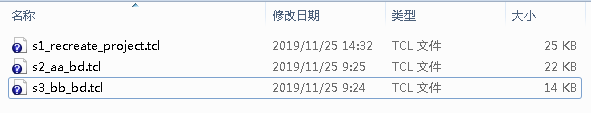

這樣,在Scripts文件夾中,就會多出三個文件:

4. 在.gitignore文件中,把整個Work目錄全部ignore掉,Src文件夾中根據實際情況進行ignore即可,HDL文件都保留,IP Core只留.xci文件;Scripts目錄全部保留。

5. 到這一步,就可以進行Commit和Push了。

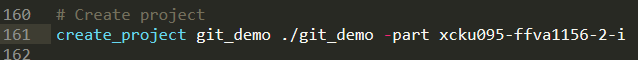

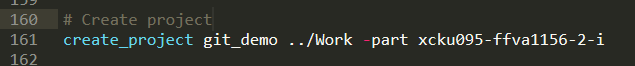

6. 把程序Clone下來后,首先要修改s1_recreate_project.tcl,需要修改的地方有兩個:一個是新建工程時的路徑,原始文件為:

替換為:

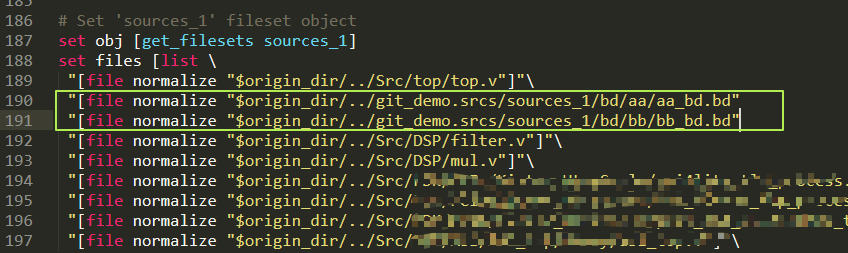

第二處需要更改的是刪除files list中的bd文件信息,如下圖中框起來的部分,這部分內容是將文件添加到工程中,但此時我們的bd文件還沒有生成,因此這兩個要刪掉。bd文件是我們通過后面的tcl腳本添加進來的。

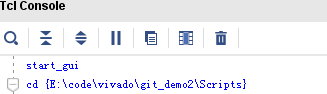

7. 切換到Scripts目錄

8. 依次執行:

source ./s1_recreate_project.tcl source ./s2_aa_bd.tcl source ./s3_bb_bd.tcl

OK,到這里工程就Clone完成了!!!

下面說一下我操作的過程中碰到的幾個問題:

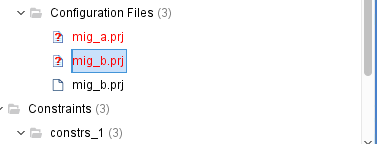

1. 如果是DDR3的MIG IP Core,會有Configuration Files,如果我們修改了MIG,并重新生成后,就會經常出現這個Configuration Files找不到的情況,像下面這樣:

這樣就要我們在導出s1_recreate_project.tcl前要先把這個文件替換成正確的文件。如果MIG是放在到bd中,那么在上述的第6步修改s1_recreate_project.tcl中,也要把mig_*.prj文件刪掉,因為這個文件是在新建MIG時自動生成的。

2. 有些朋友用bd的時候喜歡用wrapper.v的文件來封一層,這個wrapper.v是Vivado自動生成的,而且默認目錄就是在Work的工程目錄下,我們可以不用管這個wrapper.v的文件,等bd文件添加進去后,再手動生成一下即可;也可以不使用wrapper.v,直接例化bd文件。

3. 上面這種方法是在Vivado2017.2上進行的測試,如果是2017.4及以上的版本,write_project.tcl指令中需要增加-use_bd_files選項,也就是:

write_project_tcl -use_bd_files {./Scripts/s1_recreate_project.tcl}

如果不加這個選項,默認會把bd文件信息也導出,這樣在運行時會提示么有發現bd文件的錯誤。

4. 如果是低版本的工程進行git后,要用高版本的Vivado打開,我們可以在導出bd時去掉IP的版本信息,也就是:

write_bd_tcl -no_ip_version {./Scripts/s2_aa_bd.tcl}

總結

我嘗試了網上很多方法基本都不能直接使用,但他們既然把方法放到網上,說明是經過測試的,但可能測試的并不是特別全面,就是MIG的IP一樣,如果我的工程中沒有這個IP,那我也不知道在git時會出現這種問題。我也不能保證在使用別的IP時不會出現問題,但思路都是一樣的,就是把工程的tcl腳本和bd的tcl腳本分開,先新建工程把非bd文件的內容加進來,再把bd的文件內容添加進來。

編輯:hfy

-

Git

+關注

關注

0文章

201瀏覽量

15796 -

Vivado

+關注

關注

19文章

815瀏覽量

66770

發布評論請先 登錄

相關推薦

飛凌嵌入式ElfBoard ELF 1板卡-git管理源碼之git安裝和使用

云服務器 Flexus X 實例:部署 Gitea,擁有自己的 Git 倉庫,管理本地代碼

Flexus X 實例 C#/.Net Core 結合(git 代碼管理、docker 自定義鏡像)快速發布部署 - 讓你的項目飛起來~

Xilinx_Vivado_SDK的安裝教程

每次Vivado編譯的結果都一樣嗎

使用Vivado通過AXI Quad SPI實現XIP功能

Vivado使用小技巧

Vivado編輯器亂碼問題

打開esp-idf的任意一個component時,vscode會自動導入該component的git倉庫,怎么解決?

PMS系統是什么?PMS工程生產管理系統的功能

如何在AMD Vivado? Design Tool中用工程模式使用DFX流程?

深入探索Vivado非工程模式FPGA設計流程

詳解Vivado非工程模式的精細設計過程

Git進行Vivado工程管理的教程分享

Git進行Vivado工程管理的教程分享

評論