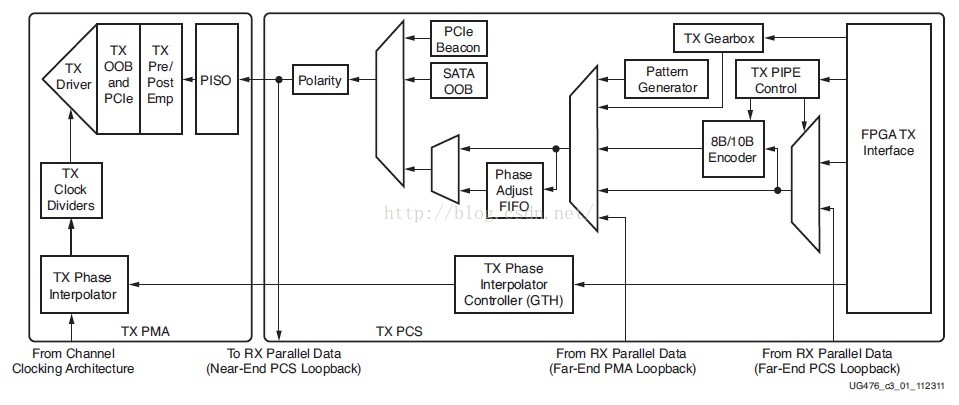

每一個收發器擁有一個獨立的發送端,發送端有PMA(Physical Media Attachment,物理媒介適配層)和PCS(PhysicalCoding Sublayer,物理編碼子層)組成,其中PMA子層包含高速串并轉換(Serdes)、預/后加重、接收均衡、時鐘發生器及時鐘恢復等電路。PCS子層包含8B/10B編解碼、緩沖區、通道綁定和時鐘修正等電路。對于GTX的發送端來說,結構如圖1所示。

FPGA內部并行數據通過FPGATX Interface進入TX發送端,然后經過PCS和PMA子層的各個功能電路處理之后,最終從TX驅動器中以高速串行數據輸出,下面將介紹各個功能電路。

FPGA TX Interface用戶接口:TX Interface是用戶數據發往GTX的接口,該接口的信號如表1所示。

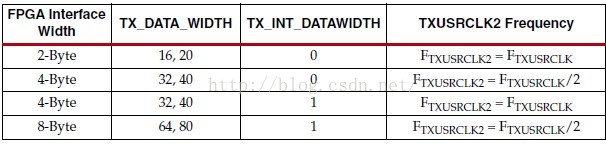

發送數據接口是TXDATA,采樣時鐘是TXUSRCLK2,在TXUSRCLK2的上升沿對TXDATA進行采樣。TXUSRCLK2的速率由線速率、TX Interface接口位寬和8B/10B是否使能決定(TXUSRCLK2頻率= 線速率/ TX_DATA_WIDTH ;比如線速率是10Gb/s,TX_DATA_WHDTH等于80,那么TXUSRCLK2的頻率是125MHz)。TXDATA的位寬可以配置成16/20/32/40/64/80位寬,通過TX_DATA_WIDTH 、TX_INT_DATAWIDTH、TX8B10BEN三個屬性設置可以配置成不同的位寬,具體屬性如表2所示。

GTX的TX Interface分成內部數據位寬和FPGA接口位寬,其中內部數據歸屬于TXUSRCLK時鐘域,FPGA接口數據歸屬于TXUSRCLK2時鐘域,而內部數據位寬支持2byte/4byte,FPGA接口數據位寬支持2byte/4byte/8byte,因此,決定了TXUSRCLK和TXUSRCLK2有一定的時鐘倍數關系,TXUSRCLK和TXUSRCLK2的時鐘倍數關系如表3所示,其中TX_INT_DATAWIDTH屬性設置為“0”,表示內部數據位寬為2byte,如果設置為“1”,則表示內部數據位寬為4byte(線速率大于6.6Gb/s的時候應當置“1”)。

TXUSRLK和TXUSRCLK2時鐘是相關聯的,在時鐘這兩個時鐘時應該遵循下面兩個準則:

1.TXUSRCLK和TXUSRCLK2必須是上升沿對齊的,偏差越小越好,因此應該使用BUFGs或者BUFRs來驅動這兩個時鐘(因為TX Interface和PCS子層之間沒有相位校正電路或者FIFO,所以需要嚴格對齊,本人自己的理解)。

2.即使TXUSRCLK、TXUSRCLK2和GTX的參考時鐘運行在不同的時鐘頻率,必須保證三者必須使用同源時鐘。

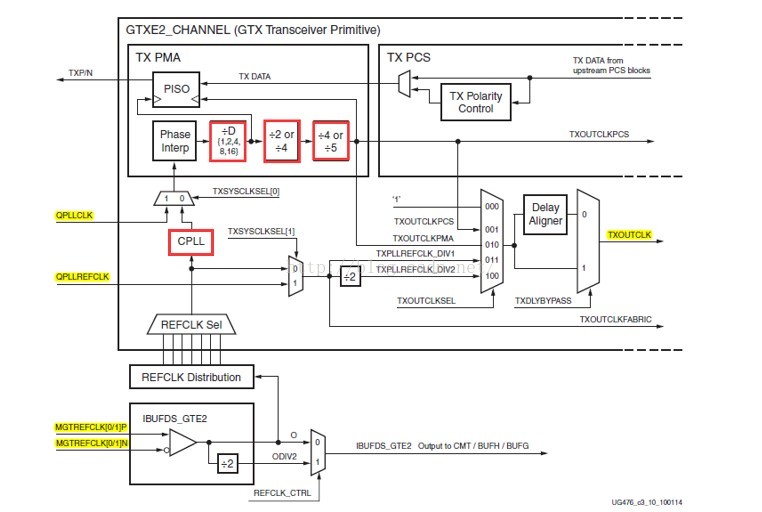

發送端的時鐘結構:為了能夠更好的理解GTX的發送端如何工作,理解發送端的時鐘結構很有必要,圖2是發送端的時鐘結構圖。

其中紅框部分和黃底部分的內容是我們需要重點了解的地方,圖中的MGTREFCLK是上一篇中提到的GTX的參考時鐘,經過一個IBUFDS_GTE2源語之后進入GTX,用以驅動CPLL或者QPLL。對于TX PMA來說,主要實現的功能是并串轉換,其并串轉換的時鐘可以由CPLL提供,也可以由QPLL提供,由TXSYSCLKSEL選擇,TX PMA子層里面有三個紅色方框部分是串行和并行時鐘分頻器,作用是產生并行數據的驅動時鐘,其中D分頻器主要用于將PLL的輸出分頻,以支持更低的線速率。

÷2/÷4這個選項由TX_INT_DATAWIDTH決定,如果TX_INT_DATAWIDTH為“0”,則選擇÷2,反之選擇÷4。

對于÷4/÷5,則由TX_DATA_WIDTH決定,如果是位寬是16/32/64,則選擇÷4,如果位寬是20/40/80,則選擇÷5。

對于TXUSRCLK和TXUSRCLK2由誰驅動呢,官方推薦使用TXOUTCLK驅動,這樣做能精簡設計,同時穩定,如何使用TXOUTCLK來做TXUSRCLK和TXUSRCLK2的驅動時鐘呢,根據TXUSRCLK和TXUSRCLK2的頻率關系,以一個Lane為例,圖3表示TXUSRCLK=TXUSRCLK2的驅動方式,圖4表示TXUSRCLK = 2*TXUSRCLK2的驅動方式。

對于圖4,CLKOUT0的值為CLKOUT1的2倍。

TX 8B/10B Encoder:高速收發器的發送端一般都帶有8b/10b編碼器。目的是保證數據有足夠的切換提供給時鐘恢復電路,編碼器還提供一種將數據對齊到字的方法,同時線路可以保持良好的直流平衡。在GTX應用中,如果發送的是D碼,則需要將TXCHARISK拉低,如果是K碼,則將相應的TXCHARISK拉高。

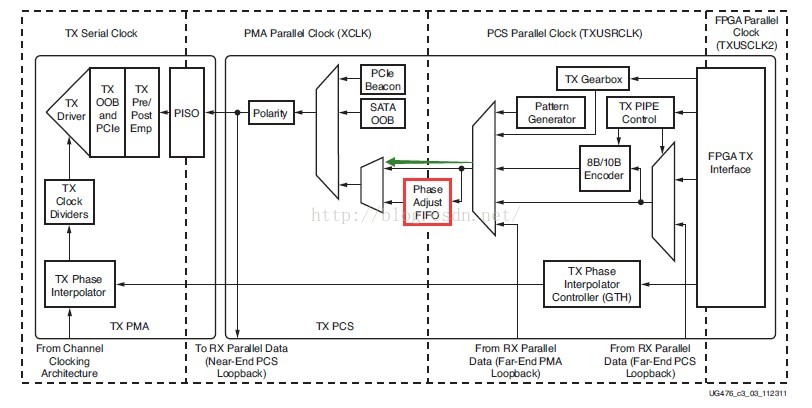

TX Buffer:了解發送的TXBuffer的作用,首先得搞清楚TX發送端的時鐘域,TX發送端的時鐘域如圖5所示。

圖5中紅色方框就是TXBuffer,我們都知道FIFO具有隔離時鐘域的功能,在這里也不例外,我們從圖中可以知道,TX Buffer連接著兩個不同的時鐘域XCLK和TXUSRCLK,在發送端的PCS子層內部包含兩個時鐘域,XCLK(PMA并行時鐘域)TXUSRCLK時鐘域,為了數據發送的穩定,XCLK和TXUSRCLK必須是速率匹配,相位差可以消除的,TX Buffer主要用于匹配兩時鐘域的速率和消除兩時鐘域之間的相位差。

TX Buffer也可以被旁路,TX發送端提供了一個相位對齊電路,可以解決XCLK和TXUSRCLK時鐘域之間的相位差,但是TX_XCLK_SEL需設置為“TXUSR”來保持XCLK時鐘域和TXUSRCLK保持同頻。

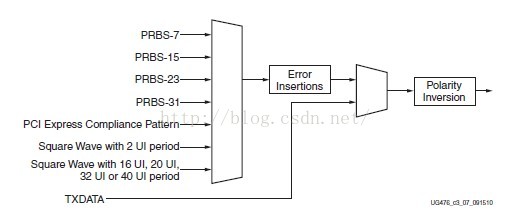

TX Pattern Generator:GTX擁有偽隨機數列產生電路,偽隨機數列是之中看似隨機,但是是有規律的周期性二進制數列,有良好的隨機性和接近白噪聲的相關函數,所以偽隨機數列可以用來做誤碼率測量、時延測量、噪聲發生器、通信加密和擴頻通信等等領域,在GTX中可以用來測試高速串行通道傳輸的誤碼率,圖6是GTX的PRBS生成電路。

可以使能或者旁路這個PRBS生成電路,如果旁路的話TXDATA會傳輸到發送端的PMA。一般使用PRBS模式測試模型如圖7所示。

TX Polarity Control:TX發送端支持對TX發送的數據進行極性控制,從PCS子層輸出的編碼數據在進入PISO串行化之前進行極性翻轉,這部分功能主要是用來彌補PCB的設計錯誤,如果PCB設計時不慎將TXP和TXN交叉連接的話,可以通過設置TXPOLARITY為“1”來翻轉信號的極性,。

編輯:hfy

-

FPGA

+關注

關注

1630文章

21769瀏覽量

604648 -

pcb

+關注

關注

4324文章

23135瀏覽量

398877 -

收發器

+關注

關注

10文章

3440瀏覽量

106110 -

驅動器

+關注

關注

53文章

8263瀏覽量

146681

發布評論請先 登錄

相關推薦

FPGA高速收發器的GTX發送端解析

FPGA高速收發器的GTX發送端解析

評論