晶振內部結構是怎么樣的?晶振該怎么選擇?晶振的布局走線怎么辦?

這些晶振問題,你都會嗎?晶振產生的時鐘被比喻成電路系統的心臟可不是隨便說說的。

好了,不長篇大論講理論,直接上干貨——晶振的必考知識點:

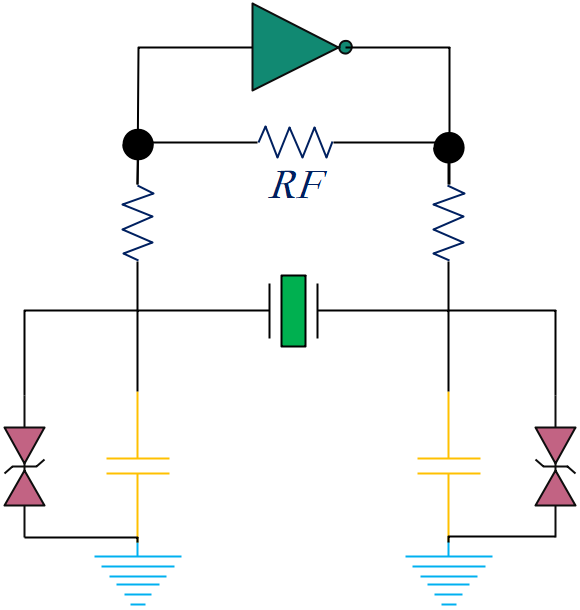

知識點一:5個要點搞定晶振電路PCB布線

位置要選對:晶振內部是石英晶體,如果不慎掉落或受不明撞擊,石英晶體易斷裂破損,所以晶振的放置遠離板邊,靠近MCU的位置布局。

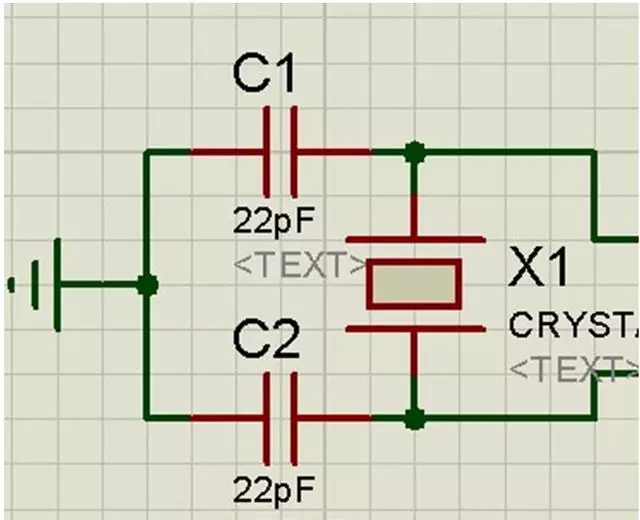

兩靠近:耦合電容應盡量靠近晶振的電源管腳,如果多個耦合電容,按照電源流入方向,依次容值從大到小擺放;晶振則要盡量的靠近MCU。

走線短:在電路系統中,高速時鐘信號線優先級最高,一般在布線時,需要優先考慮系統的主時鐘信號線。時鐘線是敏感信號,頻率越高,要求走線盡量的短,保證信號的失真度最小。

高獨立:盡可能保證晶振周圍的沒有其他元件。防止器件之間的互相干擾,影響時鐘和其他信號的質量。網傳是300mil內不要布線,實際在設計中并沒有如此嚴格。

外殼要接地:晶振的外殼必須要接地,除了防止晶振向外輻射,也可以屏蔽外來的干擾。

知識點二:查晶振問題不可缺少的三要素

01,檢查晶振本身

在運輸、焊接過程中,都可能會導致晶振內部的水晶片的損壞。如果我們在焊接晶振時,焊錫溫度過高,或者是菜鳥級別的焊接時間長,都會影響到晶振本身。如果晶振損毀,直接更換一個晶振,是查找晶振不起振的問題中最簡單的。

02,物料參數值錯誤

比如STM32使用外部晶振32.768Khz晶振,電容的容值建議在5pf-15pf之間,如果我們選擇不合適的容值,就會導致晶振不起振。

03,PCB布線問題

檢查PCB布線是否存在錯誤,如真是這個問題,那影響就非常大了,這一版就會浪費掉,還要投入更多成本,項目周期也會增加。

別再小瞧晶振了,先記住今天的知識點吧。

編輯:hfy

-

晶振

+關注

關注

34文章

2880瀏覽量

68118 -

PCB布線

+關注

關注

20文章

463瀏覽量

42081

發布評論請先 登錄

相關推薦

晶振電路PCB布線 晶振問題不可缺少的三要素

晶振電路PCB布線 晶振問題不可缺少的三要素

評論