實現(xiàn)的功能:8個數(shù)碼管輪流顯示8個數(shù)字,若頻率合適,可以實現(xiàn)8個數(shù)碼管同時被點亮的視覺效果

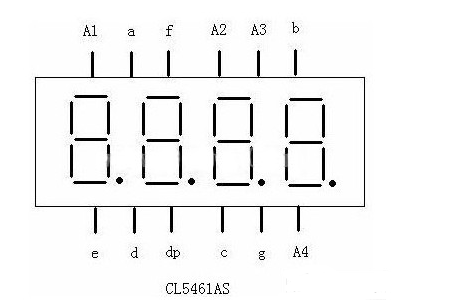

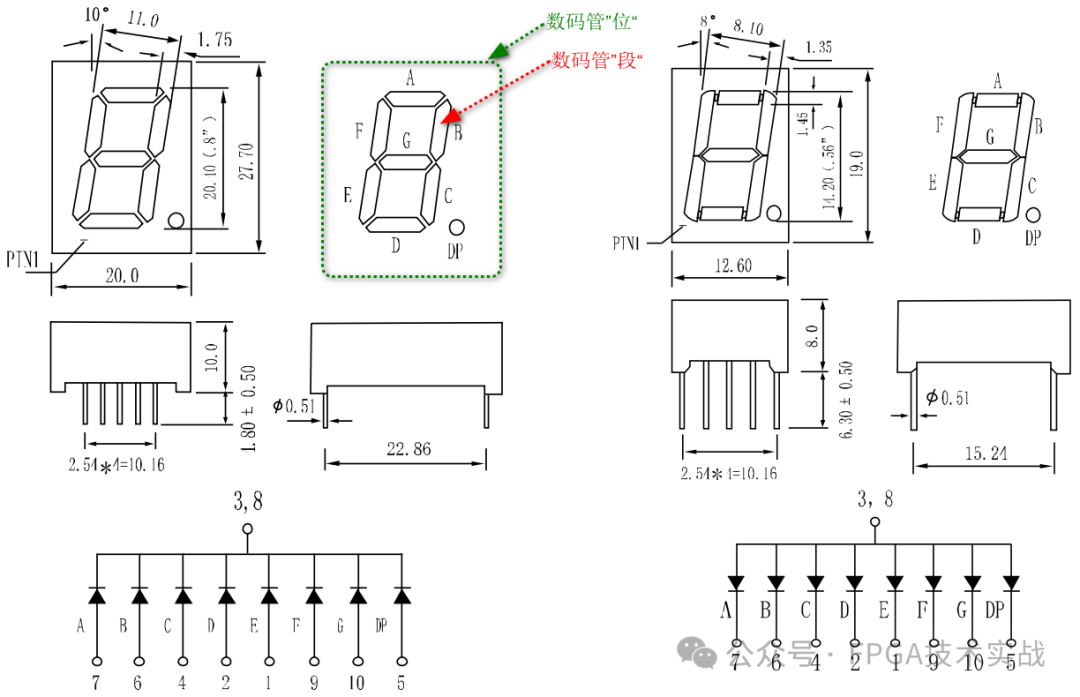

1.CL5461AS

CL5461AS 數(shù)碼管管腳圖如下圖所示,它將四個數(shù)碼顯示管的a~g 及小數(shù)點dp 管腳并聯(lián)在一起,作為數(shù)碼管數(shù)據(jù)輸入端;分別引出各個數(shù)碼管的陰極A1~A4。

只要在A1~A4 管腳上輪流加低電平其頻率大于40Hz,可實現(xiàn)四個數(shù)碼管同時被點亮的視覺效果。在點亮不同數(shù)碼管的同時輸入不同的數(shù)據(jù),即可在數(shù)碼管上同時顯示四位不同的數(shù)字。

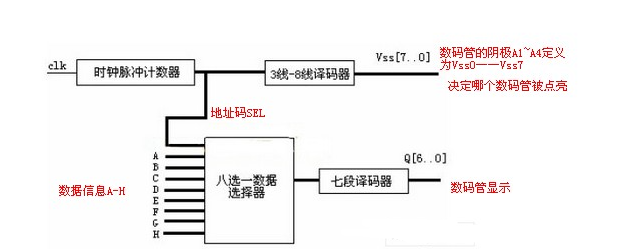

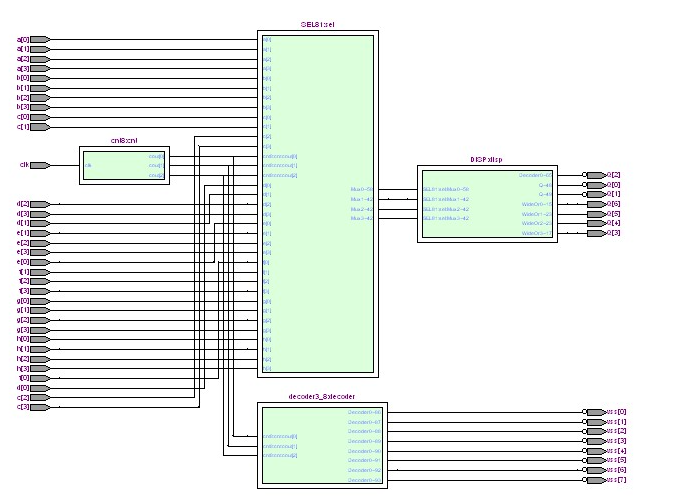

2.驅(qū)動八位數(shù)碼管顯示電路框圖

3.模塊及模塊功能

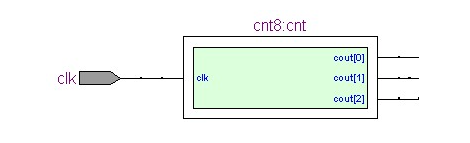

3.1時鐘脈沖計數(shù)器模塊

cnt8模塊輸入信號為時鐘脈沖clk,每遇到一個clk上升沿,內(nèi)部累加器加1,并把累加器的所得結(jié)果以二進制數(shù)的形式輸出。

1 module cnt8(clk,cout); 2 3 input clk; 4 output reg [2:0] cout; 5 6 always @(posedge clk) 7 begin 8 if(cout==7) 9 cout<=0; 10 else 11 cout<=cout+1; 12 end 13 14 endmodule

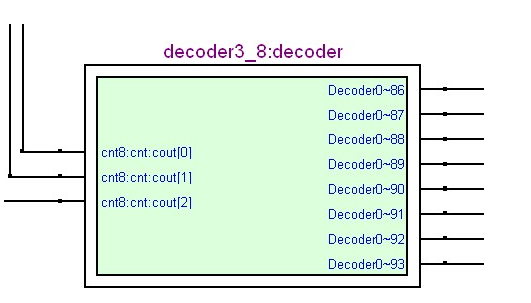

3.2 3-8譯碼器模塊

3-8模塊的輸入端A用于接收時鐘脈沖計數(shù)器cnt8模塊的輸出信號,經(jīng)過譯碼后,輸出信號Q分別接8個數(shù)碼管的陰極,是對應(yīng)的數(shù)碼管陰極為低電平,

對應(yīng)的數(shù)碼管被點亮。

1 module decoder3_8(A,vss); 2 3 input [2:0] A; 4 output reg [7:0] vss; 5 6 always @(A) 7 begin 8 case(A) 9 3'b000:vss=8'b11111110; 10 3'b001:vss=8'b11111101; 11 3'b010:vss=8'b11111011; 12 3'b011:vss=8'b11110111; 13 3'b100:vss=8'b11101111; 14 3'b101:vss=8'b11011111; 15 3'b110:vss=8'b10111111; 16 3'b111:vss=8'b01111111; 17 endcase 18 end 19 20 endmodule 21

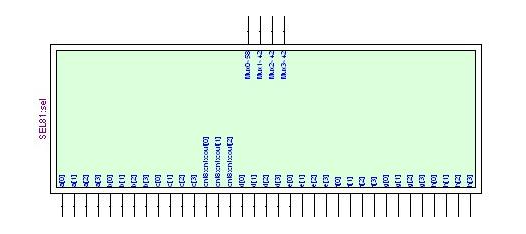

3.3 八選一數(shù)據(jù)選擇模塊

地址碼SEL來自時鐘脈沖計數(shù)器cnt8,由地址碼SEL[2:0]決定輸出哪個輸入數(shù)據(jù),輸出信號是Q[3..0].

1 module SEL81(sel,a,b,c,d,e,f,g,h,Q); 2 3 input [2:0] sel; 4 input [3:0] a,b,c,d,e,f,g,h; 5 output reg [3:0] Q; 6 7 always @(sel) 8 begin 9 case(sel) 10 3'b000:Q=a; 11 3'b001:Q=b; 12 3'b010:Q=c; 13 3'b011:Q=d; 14 3'b100:Q=e; 15 3'b101:Q=f; 16 3'b110:Q=g; 17 3'b111:Q=h; 18 endcase 19 end 20 endmodule

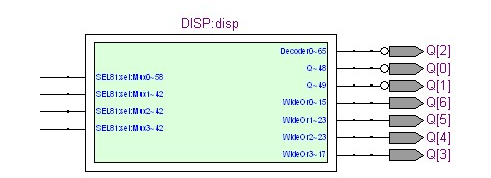

3.4 七段譯碼器模塊

DISP 模塊是七段譯碼器,將輸入的4 位二進制數(shù)轉(zhuǎn)換為數(shù)碼顯示管所對應(yīng)的數(shù)字。DISP 模塊輸入信號D[3..0]接到八選一數(shù)據(jù)選擇模塊的輸出信號Q[3..0];

七段譯碼器輸出信號Q[6..0]接數(shù)碼管的a~g 管腳。

1 module DISP(D,Q); 2 3 input [3:0] D; 4 output reg [6:0] Q; 5 6 always @(D) 7 begin 8 case(D) 9 4'b0000:Q=0111111; 10 4'b0001:Q=0000110; 11 4'b0010:Q=1011011; 12 4'b0011:Q=1001111; 13 4'b0100:Q=1100110; 14 4'b0101:Q=1101101; 15 4'b0110:Q=1111101; 16 4'b0111:Q=0100111; 17 4'b1000:Q=1111111; 18 default:Q=1101111; 19 endcase 20 end 21 endmodule 22

3.5 整體電路

1 module DisplayLED(clk,a,b,c,d,e,f,g,h,vss,Q); 2 3 input clk; 4 input [3:0] a,b,c,d,e,f,g,h; 5 output [7:0] vss; 6 output [6:0] Q; 7 8 wire [2:0] cnsel; 9 wire [3:0] qd; 10 11 12 13 cnt8 cnt (.clk(clk),.cout(cnsel)); 14 decoder3_8 decoder(.A(cnsel),.vss(vss)); 15 SEL81 sel(.sel(cnsel),.a(a),.b(b),.c(c),.d(d),.e(e),.f(f), 16 .g(g),.h(h),.Q(qd)); 17 DISP disp(.D(qd),.Q(Q)); 18 19 endmodule

編輯:hfy

-

數(shù)碼管

+關(guān)注

關(guān)注

32文章

1882瀏覽量

91126

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA設(shè)計驅(qū)動八位數(shù)碼管顯示電路方案

FPGA設(shè)計驅(qū)動八位數(shù)碼管顯示電路方案

評論