射頻PCB板設計是開發中關鍵一環,這里我們以WLAN芯片的PCB為例來具體談一下PCB layout的設計要點。

WLAN和藍牙芯片的開發板的設計重點,可以分為電源部分,晶振部分,射頻部分及接口(I/F)部分。下面我們分布談一下各部分的設計思想和注意點。

一、首先是電源部分

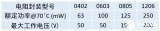

著手設計PCB之前,首先需要仔細查看SOC的電源拓撲結構,比如常見的40nm/28nm的WLAN芯片,它的電源常分為1.2V Buck Regulator,2.5V Regulator,3.3V Regulator。低電壓Reg主要供數字及PLL部分使用,高電壓Reg主要供射頻PA使用。各Buck輸出部分,一般都有輸出物理端口, 這是因為輸出端口接各個block是采用星型拓撲結構,在下一級有物理輸入接口,應用中需要接旁路電容。電源部分的layout設計主要有兩大問題,Cbuck的輸出電感,旁路電容的選取及設置,還有電源走線的設計。

旁路電容的選取對各Buck輸入/輸出 noise,輸出電壓性能有重要影響。現在的Buck DC regulator采用PFM (Pulse Frequency Modulation)方式的較多。相比以前的方式,PFM一般有更小的Vout Ripple電壓。輸出一般都串接大電感后在接去耦電容。

電感的選取,建議參考各家SOC Vendor推薦的型號。如果考慮成本選取其他Local廠商時,務必要check DCR(影響定格電流,效率),ACR(影響AC Loss)還有最大定格電流和電感&DC電流的profile圖。這幾個參數對電感來說都是相互關聯的,一般DCR高的話,定格電流就低。有條件的話,可以之間測一下Ind端AC信號,看看Peak-peak電壓變化情況。

下面是一例實測CBuck的輸出電壓,電流波形,輸出波形(藍色)相對穩定,電感上的電流波形保持穩定的線性特性,600mA的DC偏置輸出,AC電流變化差不多380mA 。 設計問題不大。

去耦電容的選取要考慮到電流capacity,定格最大電壓及誤差。要確保實際有效去耦電容的設置,要盡量靠近Reg輸入輸出端,在星型拓撲結構里,電容要安置在星型節點附近。 這是因為每個拓展出去的電源trace都會產生電感效應。主節點放置大容量的電容可以起到高頻噪聲濾波功能。 電源的布線,要重點考慮2點:1)避開對其他對noise敏感的布線的coupling;2)降低電源EMI loop的影響。先談談第1點,對noise敏感的布線,比如SOC的一些總線,RF相關端口,還需要查看datasheet的keep out區域。對一些功耗大的Reg電源布線要充分考慮到散熱設計。一般來說SOC的主Buck的輸入輸出pin也常分布在芯片的轉角附近,這樣的Pin布局,有利于PCB設計,電源的布線考慮到散熱效應,一般在layer1,layer2上的較多。電源的接地設計,依據PCB層數, 有條件的話, 可以單獨設置一層放PMU布線。在WLAN設計里,一般性都采用4層以上的PCB,第一層(top)一般設計成PMU的GND island,與周邊的其他布線加強隔離度。第2點是 EMI loop, 現代SOC的switching 電源本身就是個noise源,如何優化EMI Loop是個必須關心的問題。Cbuck的輸入側的Loop和輸出側的loop,每個loop經電源輸入或輸出端口,經過旁路電容,再到ground。每個Loop都要設計成盡可能短的物理layout,確保noise不會干擾的其他布線。電源走線在上下層改變時,要盡可能設計多的過孔。

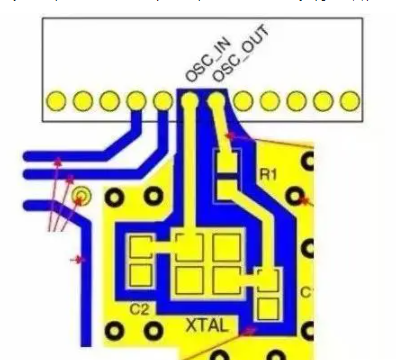

二、談談晶振(Xtal)部分。隨著SOC設計及工藝提高,以前常見的PLL LPF外接,最近一般都完全設計在芯片里面了。 所以晶振部分成了PLL這一環主要care的問題。一般現在的mobile應用, 常用到19.2MHz, 26MHz,及37.4MHz的頻率。Xtal 電容值的選取超過了本文的scope,這里略過主要談談xtal的布線。常見的xtal都是帶輸入,輸出的端子。 曾經有遇到過最深刻的一個問題就是Xtal對RF端口之間產生影響,晶振頻率的諧波能量導致了認證測試失敗。后來吸取教訓,在xtal的top layer布線(輸入,輸出及xtal cap的布線)設計成獨立的island。(參考下圖)如果space不允許的話,至少簡易在xtal靠近RF一層,在GND里加一條Slot, 也可以降低xtal諧波干擾的風險。

Xtal布線的下面一層,建議不要設計其他敏感的走線(比如I/F,其他電源走線等)。

三、談一下射頻部分的走線要點。

總的來說,現在主流的WLAN SOC芯片,Rx的性能相比Tx性能,spec上余量更多,所以布線的時候,一般常優先考慮Tx側的布線。比如FEM可以設計在離Tx近一點的地方。RF走線(50歐)設計,常用的方法是:1 )挖空下面一層的metal,使50ohm線寬變粗,減少走線和元件pad的不連續性。2 )RF走線兩端的GND一定要設計盡可能多的GND via。特別是在最后接ANT的地方, GND via過少直接會影響到RF loss。 3 )RF走線一般盡量少彎曲90度以上,space余度不多的地方,可以90度彎曲。4 )注意Tx和Rx之間的isolation,現在的WLAN芯片,很多都是2x2以上的MIMO,射頻部分的走線變得愈加復雜。雖然WLAN采用的是TDM方式,但是在FEM的layout pattern設計,還是兼顧電源,Tx和Rx的coupling影響。

四、接口部分的走線設計。

作者接觸到SDIO,SPI及PCIE的I/F較多。接口bus速度越快,對layout設計要求越高。 SDIO 3.0的話,保證每個走線都是50ohm并且長度要小于10cm,確保各數據線間的走線長度差要小于100mil (2.54mm 相當于17.5ps jitter)。 走線一般滿足thumb of rule即2:1的經驗公式,比如trace width=4mil, 則gap最好8mil以上。另外clock走線最容易產生noise,所以clock走線要與其他數據線隔開,最好加入gnd glitch。接口的走線一般都是比較noise敏感的,盡量避開和電源走線layer的交迭重合。 比如下面一例,電源層(藍色)和數據接口層(黃線)在層與層上面盡量做到沒有交迭重合。主要電源走線的下面layer一般布置了GND走線。

在實際應用中, 常常會首先遇到是單面PCB設計還是雙面PCB設計。如果是單面PCB設計的話,各路元件的布置需要遠近取舍,考慮優先度。 還有部分朋友接觸的可能不是SOC芯片,而是集成了SOC芯片的模塊,比如Murata, TDK等廠商的WLAN模塊。這些模板因為內部完成了對Xtal,RF FEM/Trace的集成,進一步降低了PCB的設計,但是對電源走線,還是需要PCB板級設計的注意。 小結此文主要介紹了射頻SOC芯片的PCB板設計的4大要點,其實每個要點都離不開GND的配置設計。 在客戶的設計案例中,我們也遇到不少因為layout設計缺陷而改版的案子,很多問題我們在上面都已談到,相信不少同領域的朋友應該會有同感。

編輯:hfy

-

WLAN

+關注

關注

2文章

658瀏覽量

73167 -

藍牙芯片

+關注

關注

17文章

378瀏覽量

46127 -

Pcb layout

+關注

關注

6文章

98瀏覽量

29186

發布評論請先 登錄

相關推薦

pcb設計中布局的要點是什么

PCB電路板設計與制作的步驟和要點

PCB Layout 的 9 個套路

PMP30916.1--8V 反相降壓/升壓 PCB layout 設計

PMP30930.1-EMI 優化型降壓 PCB layout 設計

TIDEP-01022-汽車網關 PCB layout 設計

TIDA-060029-LCR 表模擬前端 PCB layout 設計

PMP20587.1-反相降壓/升壓 PCB layout 設計

TIDA-010052-用于電機驅動的安全電源 PCB layout 設計

PMP30805.1-小型汽車 SEPIC PCB layout 設計

PMP30691.1-具有多路輸出軌 PCB layout 設計

PMP21783.1-60W、超寬范圍電源 PCB layout 設計

PMP31194.1-使用集成 FET 的汽車 SEPIC PCB layout 設計

基于WLAN芯片的PCB layout的設計要點

基于WLAN芯片的PCB layout的設計要點

評論