使用波形配置文件

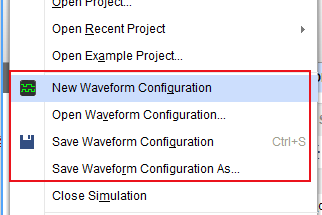

Vivado Simulator允許用戶自定義波形顯示方式,當前的顯示狀態稱作波形配置。波形配置可以保存為WCFG文件,供以后使用。一個波形配置對應一個Wave窗口,沒有保存的波形配置顯示為untitled。打開仿真后,File菜單中有與波形配置相關的指令:

這些控制功能依次是:

- New Waveform Configuration:創建一個新的波形配置,Vivado會打開一個新波形窗口,但是不包含任何HDL對象,設計者從Scope或Object窗口中人工添加;

- Open Waveform Configuration:打開配置文件同時打開一個波形窗口,會顯示存儲在WCFG文件中對象的波形數據;

- Saving a Wave Configuration:保存當前波形配置到WCFG文件中。

如果關閉了仿真,下次需要使用是只是想查看上次仿真的結果,而不是重新運行仿真,點擊Flow菜單下的Open Static Simulation,選擇WDB文件即可(在project.sim/sim_1/behav路徑下)。靜態仿真模式下,Vivado Simulator會從WDB文件中讀取數據并顯示。

運行仿真過程中,會將顯示的HDL對象的波形活動、Sope窗口中的對象、Objects窗口中的對象存儲到WDB文件中。但注意,Vivado不能打開2014.3版本之前創建的WDB文件。

窗口對象(wave object)

向波形配置中添加一個HDL對象,其實并不是直接添加該對象,Vivado會創建一個窗口對象,該對象與HDL對象有聯系也有區別。借助此特性,一個HDL對象可以創建多個與其相關的窗口對象,且每個窗口對象的顯示設置可以不同。比如一個用16進制顯示,另一個用10進制顯示。

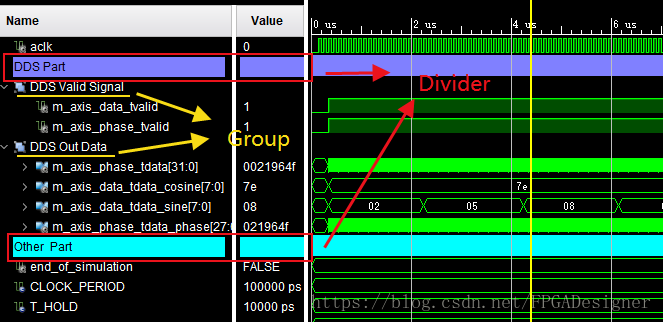

由HDL對象而來的窗口對象稱作設計窗口對象,除此之外,還有其它的對象類型:隔離帶(divider)、群組(group)、虛擬總線(virtual buses)。這些對象都是為了提高觀察波形的便捷性,前兩者示例如下圖。虛擬總線是將多個信號組合為一個總線顯示。

波形窗口中包含Name、Value和波形三部分。

- Name默認顯示為short形式,右鍵菜單中Rename指令可以創建custom名稱,Name指令選擇顯示方式為short、long(顯示對象所處層次路徑)或custom。

- Value根據格式和基數設置顯示方式不同,注意波形窗口中的radix和Objects窗口中的radix設置只作用于各自的窗口。

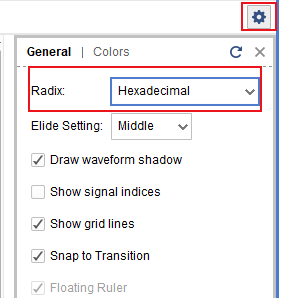

默認Value顯示的基數為16進制,想要改變默認設置,在波形窗口中點擊Settings,選擇一個Radix:

順便再介紹下其它設置選項實現的功能效果:

- Elide Setting:如果信號名字太長無法完整顯示,該選項設置從哪邊開始省略字符顯示,包括left、middle和right。

- Draw Waveform Shadow:選中,波形顯示會帶有陰影效果。

- Show signal indices:選中,波形對象的Name左側會顯示對應的行數,并且可以拖動行數之間的橫線來改變波形對象的高度。

- Show grid lines:選中,波形窗口中會顯示網格線。

- Snap to Transition/Floating Ruler:與測量有關,具體在下文介紹。

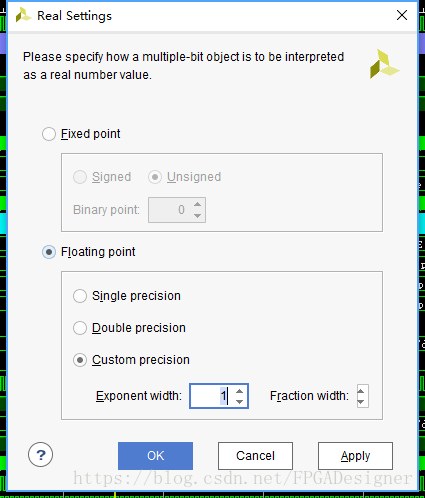

在選中對象的右鍵菜單->Radix中可以設置單個信號的基數(應與該信號的本質相符),常見的基數已經非常熟悉。Radix還可以選擇為Real,設計者可以在Real Setting中設置Value按指定的定點數或浮點數格式顯示,提供了極大的便利性。

該功能非常實用,比如CORDIC IP核在計算arctan函數時,輸出數據為帶符號、小數點從MSB三位后的格式,只需要在這里設置相應格式,就可以直接顯示為-pi~pi的范圍,而不需要人工計算。

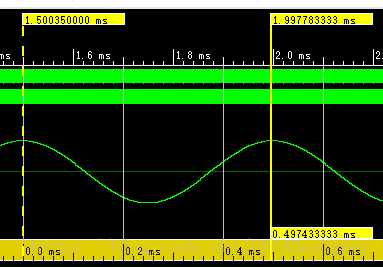

設置模擬波形顯示方式

有時總線數據用模擬波形的方式觀察更直觀,但注意信號的Radix設置必須符合其本質,才能顯示正確的波形。比如一個總線數據按帶符號二進制補碼編碼,Radix必須設置為一種帶符號格式;如果一個數據為浮點數格式,必須選擇real并做正確的設置。

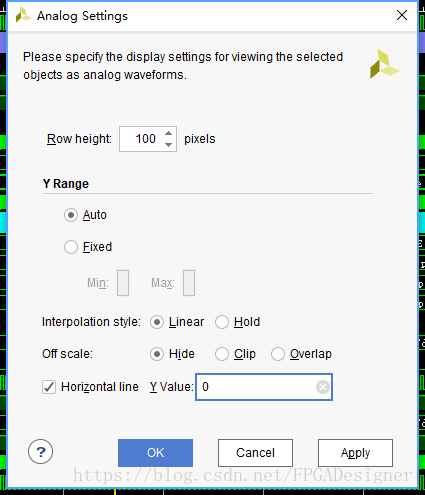

在對象右鍵->Waveform Style,可選擇模擬(Analog)或數字(Digital)顯示方式,Anolog Settings中可以設置模擬波形的顯示方式。注意:模擬顯示僅支持位寬不超過64Bits的總線。

下面介紹一下各選項的設置方法和效果:

- Row Height:規定選中對象的顯示高度,單位為像素點數目,相當于收縮或拉伸波形的高度(digital顯示方式高度為20,analog顯示高度默認為100)。

- Y Range:規定波形區域的數值顯示范圍。Auto模式下根據當前的仿真時間內的值自動選擇范圍,且會隨時間更新;Fixed設置固定的顯示范圍。

- Interpolation Style:設置將數據點連成線的插值方式,Liner表示線性插值,Hold表示保持插值,兩個點之間的數據會保持前一個點的數據值。

- Off Scale:設置超出顯示范圍的波形該如何處理,Hide會隱藏超出范圍的部分,Clip會超出范圍為的部分限制在最大值/最小值(即削頂),overlap在超出范圍時仍然會顯示波形,但是波形會疊在其它波形對象上。

- Horizontal Line:選中會在指定值處畫一條水平線。

此外,某些總線信號的有效順序可能與定義的Bit順序相反,可以在右鍵菜單中選擇“Reverse bit order”交換總線Bit順序,如bus[7:0]交換后為bit[0:7],信號的值和波形也會跟著改變。

在時間刻度上右鍵,可以設置顯示時間的方式,包括fs、ps、ns、us、ms、s,Auto會自動選擇最適合的單位,Default表示HDL設計中規定的仿真精度。此外還有Samples以離散采樣數值的方式顯示,User為用戶自定義的時間單位,但這兩個設置對HDL無效。

觀察波形輔助工具

上文提到窗口對象中還包括如下三類,來幫助設計觀察仿真結果:

- Group:一個Group相當于一個容器,將相關的波形對象組合在一個文件夾中。選中想要添加的對象,右鍵->New Group即可建立一個新組。注意選中group后delete會刪除掉該組和內部所有的對象,如果只是想解散組,使用右鍵菜單中的Ungroup。

- Divider:divider用來隔離不同的HDL對象,點擊信號的右鍵菜單中->New Divider,會在其下方創建一條隔離帶,delete即可刪除。

- Virtual Bus:可以將多個標量或向量組合在一起作為虛擬總線顯示,按順序選中要添加的對象,右鍵->New Virtual Bus。同樣delete會刪除掉虛擬總線所有對象,僅刪除虛擬總線應使用Ungroup。

除此之外,Vivado還提供了一些其它特性幫助設計者分析波形中的數據:

1.光標

在波形上單擊,會出現黃色的光標,稱之為主光標;按住Shift鍵,再在另一個地方點擊,會出現第二個光標,稱之為輔助光標(虛線,會替換原主光標所在位置)。頂部會顯示每個光標所處的時間點,底部有刻度尺且顯示兩者之間的時間差(顯示刻度尺需要在設置中選中Floating Ruler)。單擊波形窗口的任意地方,即可隱藏輔助光標。

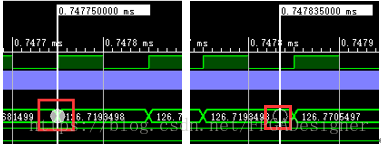

如果設置中選中了Snap to Transition,拖動光標過程中會有一個根據數據轉換狀態變換的圈(不選中該功能始終為空心圈,不會變化)。空心圈○表示光標處在信號的兩個過度點之間(過度點即為值發生改變的點);實心圈●表示光標位于過度點處或標記(marker)上。如下圖所示:

通過此功能,設計者即可準確地將光標置于信號的邊緣處。波形窗口工具欄中還有Previous Transition和Next Transition兩個功能,可以改變光標位置到選定對象的前一個或后一個過度點。可以同時選中多個對象。

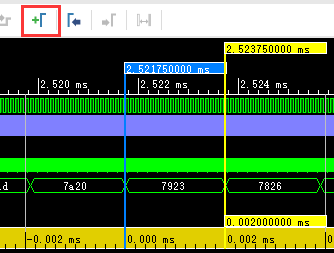

2.標記

標記(Marker)用來指示波形中設計者關心的重大事件,可以對與標記事件相關的時間進行測量。在窗口工具欄中點擊Add Marker(如下圖紅框)添加標記,自動測量并顯示標記與光標之間的時間差。

標記同樣支持Snap to Transition功能,讓設計者可以準確地標記信號邊緣。在標記上右鍵,選中Delete Marke**r或**Delete All Markers即可刪除標記。底部也會顯示時間刻度尺輔助時間測量,0時刻從輔助光標開始,如果沒有輔助光標會從選中的Marker處開始。

3.查找功能

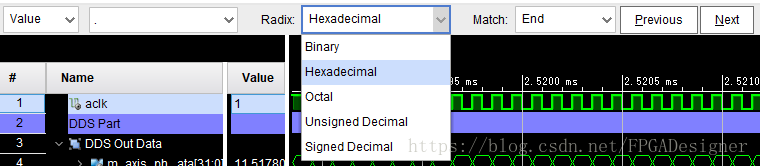

右鍵菜單中Find/Find Value可分別用于查找某一對象或者選中對象中的特定值。空白框中輸入帶查找字符串,必須與設置的Radix相符,否則編輯框會變為紅色提示錯誤(如十六進制就只能輸入0-F)。

句號的點‘.’相當于通配符,如查找“1.2”,便會找到102、112等等。Match用于設置匹配模式,Beginning、End(以查找內容為開頭或結尾)或Exact(精確值)。Previous和Next在結果之間切換,如果沒有找到工具條會顯示“Value not found”。

編輯:hfy

-

波形

+關注

關注

3文章

379瀏覽量

31595 -

Vivado

+關注

關注

19文章

813瀏覽量

66657 -

Waveform

+關注

關注

0文章

3瀏覽量

1930

發布評論請先 登錄

相關推薦

AMD Vivado Design Suite 2024.2全新推出

Xilinx_Vivado_SDK的安裝教程

每次Vivado編譯的結果都一樣嗎

使用Vivado通過AXI Quad SPI實現XIP功能

Vivado使用小技巧

Vivado編輯器亂碼問題

詳解工業網關在線探測功能及用途

Vivado 使用Simulink設計FIR濾波器

詳解Vivado非工程模式的精細設計過程

Vivado Waveform功能使用技巧詳解

Vivado Waveform功能使用技巧詳解

評論