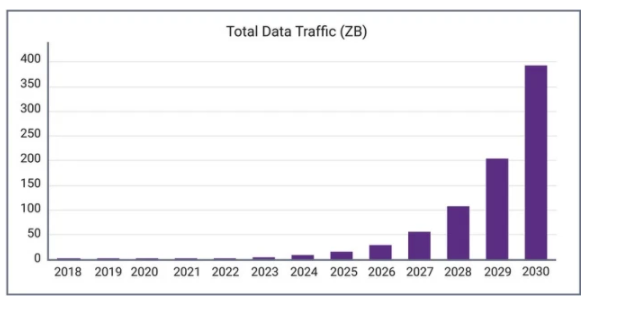

流媒體,監(jiān)視和監(jiān)視數(shù)據(jù),連接的傳感器,社交媒體,在線(xiàn)協(xié)作,遠(yuǎn)程學(xué)習(xí),增強(qiáng)和虛擬現(xiàn)實(shí),在線(xiàn)游戲……在線(xiàn)應(yīng)用的無(wú)休止清單導(dǎo)致在線(xiàn)數(shù)據(jù)激增。在接下來(lái)的10年中,預(yù)計(jì)年度數(shù)據(jù)流量將增長(zhǎng)400倍以上(圖1)。數(shù)據(jù)流量的這種快速增長(zhǎng)將需要顯著提高數(shù)據(jù)接口IP的速度和延遲,尤其是在云基礎(chǔ)架構(gòu)中。本文研究了有助于加快和管理數(shù)據(jù)中心之內(nèi)和之間,服務(wù)器內(nèi)以及片上系統(tǒng)(SoC)包內(nèi)的數(shù)據(jù)移動(dòng)的技術(shù)發(fā)展。

圖1:到2030年的總數(shù)據(jù)流量預(yù)測(cè)。資料來(lái)源:“人工智能對(duì)電子和半導(dǎo)體行業(yè)的影響”,IBS,2020年4月。

數(shù)據(jù)中心內(nèi)部和之間的遠(yuǎn)程數(shù)據(jù)移動(dòng)

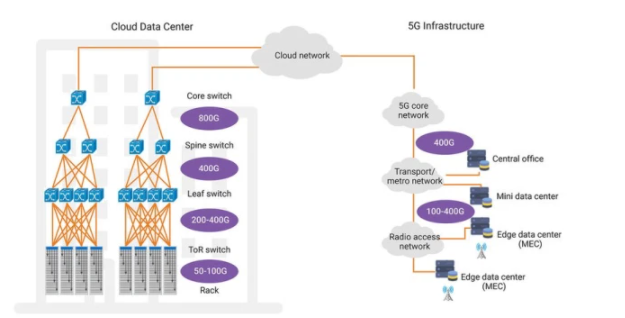

當(dāng)今大多數(shù)大型數(shù)據(jù)中心都使用100Gbps以太網(wǎng)基礎(chǔ)結(jié)構(gòu)來(lái)長(zhǎng)距離移動(dòng)數(shù)據(jù)(例如,在機(jī)架和數(shù)據(jù)中心之間)。遠(yuǎn)程基礎(chǔ)設(shè)施通常依賴(lài)于25個(gè)或28 Gbps NRZ SerDes電連接的4個(gè)通道。但是,隨著數(shù)據(jù)量的增長(zhǎng),需要更高速度的基礎(chǔ)架構(gòu)來(lái)維持?jǐn)?shù)據(jù)移動(dòng)。使用支持PAM-4編碼的56 Gbps和112 Gbps SerDes IP,可以在當(dāng)前部署的超大規(guī)模數(shù)據(jù)中心實(shí)現(xiàn)400Gbps以太網(wǎng)連接,并在將來(lái)達(dá)到800Gbps的速度(圖2)。領(lǐng)先的以太網(wǎng)交換機(jī)供應(yīng)商已經(jīng)在開(kāi)發(fā)基于112G SerDes IP的800Gbps交換機(jī),并計(jì)劃在未來(lái)幾年內(nèi)推出1.6Tbps以太網(wǎng)(使用更快的下一代SerDes),以滿(mǎn)足不斷增長(zhǎng)的數(shù)據(jù)量的需求。

機(jī)架內(nèi)服務(wù)器之間的數(shù)據(jù)通信由機(jī)架頂(ToR)交換機(jī)和每臺(tái)服務(wù)器內(nèi)的網(wǎng)絡(luò)接口卡(NIC)進(jìn)行管理。在過(guò)去的幾年中,此級(jí)別的云數(shù)據(jù)中心中最常見(jiàn)的接口速度為25Gbps。但是,隨著基礎(chǔ)架構(gòu)速度增加到400Gbps,機(jī)架內(nèi)的以太網(wǎng)速度也增加到100Gbps。

隨著數(shù)據(jù)速率的提高,接口功率(通常以皮焦耳/位為單位)和面積變得越來(lái)越重要。物理接口(PHY)IP可以最大限度地減少能源消耗,同時(shí)在所需的距離范圍內(nèi)可靠地傳輸數(shù)據(jù),具有明顯的優(yōu)勢(shì),可以最大程度地降低基礎(chǔ)架構(gòu)電源和冷卻能力的成本。硅面積高效的PHY解決方案將SoC成本降至最低,從而提高了SoC供應(yīng)商的盈利能力。

圖2:超大規(guī)模數(shù)據(jù)中心基礎(chǔ)架構(gòu)正在過(guò)渡到400 + GbE。

服務(wù)器內(nèi)的數(shù)據(jù)移動(dòng)

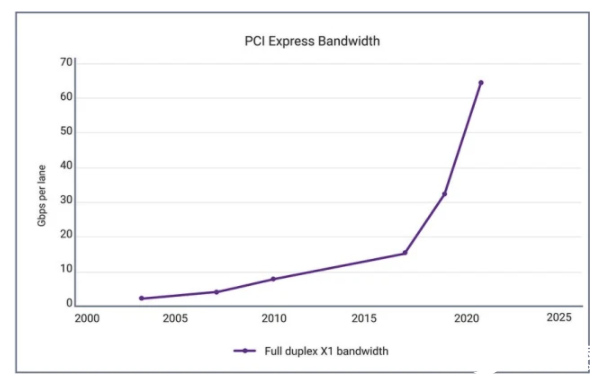

一旦所有這些數(shù)據(jù)到達(dá)服務(wù)器,就需要高速接口以將其有效地在服務(wù)器內(nèi)的設(shè)備之間移動(dòng)。例如,當(dāng)數(shù)據(jù)以100Gbps的速度到達(dá)NIC時(shí),必須迅速將其移至存儲(chǔ),系統(tǒng)內(nèi)存,或者也許移至圖形或AI加速器進(jìn)行處理。這是PCI Express(PCIe),Compute Express Link(CXL)和類(lèi)似協(xié)議的領(lǐng)域。為了應(yīng)對(duì)流量的快速增長(zhǎng),PCI-SIG在2019年發(fā)布了PCIe 5.0,與上一代產(chǎn)品相比帶寬增加了一倍,并計(jì)劃在2021年發(fā)布PCIe 6.0,這將使PCIe數(shù)據(jù)速率再次翻倍至64 GT / s (對(duì)于x16卡,最高可達(dá)128GB / s)(圖3)。

圖3:每個(gè)通道的PCI Express帶寬演進(jìn)。資料來(lái)源:PCWorld。

由計(jì)算系統(tǒng)生成和處理的數(shù)據(jù)(尤其是非結(jié)構(gòu)化數(shù)據(jù))的數(shù)量最近和持續(xù)增長(zhǎng),催生了新的體系結(jié)構(gòu),通常采用加速器來(lái)促進(jìn)數(shù)據(jù)處理。將數(shù)據(jù)從一個(gè)處理器域復(fù)制到另一個(gè)處理器域是一個(gè)資源密集型過(guò)程,可能會(huì)增加數(shù)據(jù)處理的延遲。高速緩存一致性解決方案允許處理器和加速器共享內(nèi)存,而無(wú)需將數(shù)據(jù)從一個(gè)存儲(chǔ)空間復(fù)制到另一個(gè)存儲(chǔ)空間,既節(jié)省了存儲(chǔ)資源,又節(jié)省了復(fù)制數(shù)據(jù)所需的時(shí)間。

CXL是一種緩存一致性協(xié)議,它利用PCIe的數(shù)據(jù)速率和物理層來(lái)使CPU和加速器能夠訪(fǎng)問(wèn)彼此的內(nèi)存。當(dāng)多個(gè)設(shè)備需要訪(fǎng)問(wèn)單個(gè)數(shù)據(jù)集時(shí),集成CXL協(xié)議有效地減少了非一致性協(xié)議必須出現(xiàn)的數(shù)據(jù)副本的數(shù)量,從而減少了系統(tǒng)內(nèi)所需的傳輸次數(shù)。減少數(shù)據(jù)副本的數(shù)量有助于減少系統(tǒng)中已經(jīng)大量訂閱的內(nèi)存和IO接口的負(fù)載。

與其他外圍互連相比,CXL面向高性能計(jì)算工作負(fù)載,可顯著減少延遲。由于cxl.cache和cxl.mem事務(wù)的延遲僅為50-80ns,因此CXL延遲僅是PCIe延遲的一小部分。此外,CXL通過(guò)使用資源共享來(lái)提高性能并降低復(fù)雜性,這也可以降低總體系統(tǒng)成本。

SOC中的USR / XSR數(shù)據(jù)移動(dòng)

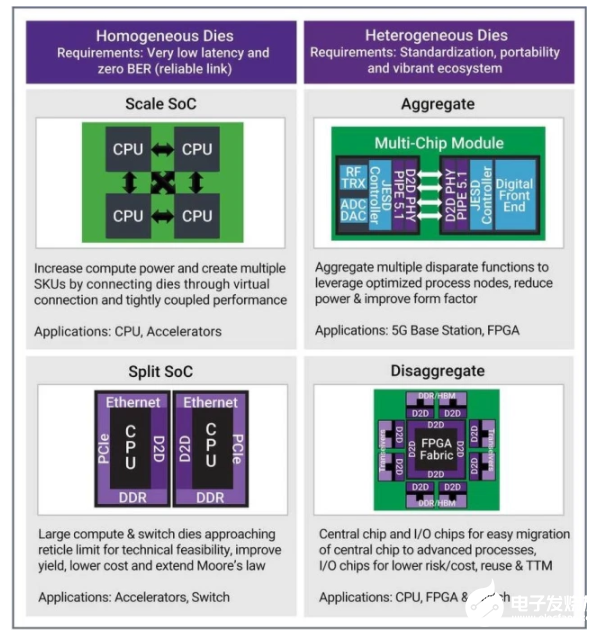

許多現(xiàn)代服務(wù)器SoC在單個(gè)封裝中利用多個(gè)管芯,以在設(shè)計(jì)和制造約束下提供所需的性能。結(jié)果,需要高速管芯到管芯(D2D)通信,以在芯片內(nèi)的管芯之間傳遞大型數(shù)據(jù)集。超短距離/超短距離(USR / XSR)SerDes使這一切成為可能,當(dāng)前使用112Gbps SerDes的設(shè)計(jì)以及未來(lái)幾年內(nèi)可能會(huì)出現(xiàn)更高的速度。

使用D2D接口技術(shù)的多芯片模塊可解決多種用例。所有D2D用例都減少了開(kāi)發(fā)時(shí)間以及開(kāi)發(fā)和制造成本。有些使用多個(gè)異類(lèi)芯片或“小芯片”,它們利用可重復(fù)使用的功能組件,每個(gè)組件均使用針對(duì)其特定功能最佳的制造技術(shù)來(lái)構(gòu)建。其他用例則通過(guò)創(chuàng)建大型高性能SoC來(lái)強(qiáng)調(diào)靈活性,該SoC使用較小的同類(lèi)構(gòu)建模塊來(lái)提高產(chǎn)量和可擴(kuò)展性。

圖4:管芯到管芯互連的用例示例。

概要

云數(shù)據(jù)的快速增長(zhǎng)推動(dòng)了對(duì)更快,更高效的接口的需求,這些接口要求將云基礎(chǔ)架構(gòu)中的數(shù)據(jù)從網(wǎng)絡(luò)和系統(tǒng)向下移動(dòng)到芯片級(jí)數(shù)據(jù)通信。新的和正在開(kāi)發(fā)的接口技術(shù),包括400Gbps和更快的以太網(wǎng),PCIe 6.0和CXL外圍互連技術(shù),以及用于管芯對(duì)管芯通信的新型高速SerDes,可實(shí)現(xiàn)支持不斷發(fā)展的云數(shù)據(jù)需求所需的基礎(chǔ)架構(gòu)增強(qiáng)功能。

Synopsys的DesignWare?高速SerDes和以太網(wǎng)IP支持下一代數(shù)據(jù)中心網(wǎng)絡(luò)解決方案。90%的領(lǐng)先半導(dǎo)體公司都使用DesignWare PCIe IP,它是DesignWare CXL IP的穩(wěn)定可靠的基礎(chǔ)。DesignWare 112G USR / XSR SerDes IP為多管芯SoC提供了一種低成本,高能效的管芯到管芯接口。Synopsys提供了經(jīng)過(guò)硅驗(yàn)證的DesignWare接口IP以及開(kāi)發(fā)用于滿(mǎn)足當(dāng)今和未來(lái)云基礎(chǔ)設(shè)施不斷發(fā)展的數(shù)據(jù)移動(dòng)需求的高速,低功耗,高度可靠的SoC所必需的設(shè)計(jì)和驗(yàn)證工具的完整產(chǎn)品組合。

編輯:hfy

-

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5449瀏覽量

172176 -

數(shù)據(jù)中心

+關(guān)注

關(guān)注

16文章

4830瀏覽量

72251

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

高效數(shù)據(jù)中心升級(jí):400G光模塊測(cè)試與采購(gòu)策略

當(dāng)今數(shù)據(jù)中心新技術(shù)趨勢(shì)

請(qǐng)問(wèn)AIC3104內(nèi)部采樣是否有偏置,有的話(huà)如何去掉偏置使數(shù)據(jù)中心在0附過(guò)?

怎樣保障數(shù)據(jù)中心不間斷電源不斷電 提供可靠安全的供配電#數(shù)據(jù)中心

需要合理規(guī)劃數(shù)據(jù)中心不能盲目建設(shè)

八大科技巨頭攜手推進(jìn)UALink,加速數(shù)據(jù)中心AI互聯(lián)

數(shù)據(jù)中心布線(xiàn)光纜設(shè)計(jì)方案

傳統(tǒng)數(shù)據(jù)中心架構(gòu)和葉脊架構(gòu)網(wǎng)絡(luò)解決方案

#MPO預(yù)端接 #數(shù)據(jù)中心機(jī)房 #機(jī)房布線(xiàn)

多業(yè)務(wù)光端機(jī)在數(shù)據(jù)中心的應(yīng)用:提升網(wǎng)絡(luò)效率的關(guān)鍵

數(shù)據(jù)中心內(nèi)部和之間的遠(yuǎn)程數(shù)據(jù)移動(dòng)如何避免HPC數(shù)據(jù)流量阻塞

數(shù)據(jù)中心內(nèi)部和之間的遠(yuǎn)程數(shù)據(jù)移動(dòng)如何避免HPC數(shù)據(jù)流量阻塞

評(píng)論