跡線阻抗控制是正確確定跡線大小的簡(jiǎn)單問題。當(dāng)單獨(dú)考慮一條走線時(shí),其阻抗將具有明確定義的值。但是,當(dāng)靠近另一個(gè)走線或?qū)w時(shí),由于意外耦合,走線的阻抗將不同于其設(shè)計(jì)值。這種令人討厭的事實(shí)會(huì)導(dǎo)致沿互連線的阻抗變化,并且傳輸線和接收器之間的極端阻抗不匹配將導(dǎo)致信號(hào)反射。

盡管您可能已經(jīng)按照最佳實(shí)踐對(duì)PCB布局進(jìn)行了布線,并且僅使用設(shè)計(jì)的走線寬度進(jìn)行布線,但仍可能會(huì)面臨互連中阻抗變化的風(fēng)險(xiǎn)。在這里,約束驅(qū)動(dòng)設(shè)計(jì)的好處是可以在布線時(shí)根據(jù)設(shè)計(jì)約束檢查電路板。如果您要使用舊板,并且需要分批檢查阻抗,則可以運(yùn)行批處理DRC并瀏覽阻抗違規(guī)情況。

阻抗控制就是要確保PCB中走線的幾何形狀在每個(gè)互連中均保持一致。這適用于單端和差分對(duì)。需要定義這些約束以符合您的高速信令標(biāo)準(zhǔn)。這些信令標(biāo)準(zhǔn)又取決于您選擇的組件或您正在設(shè)計(jì)的接口類型。

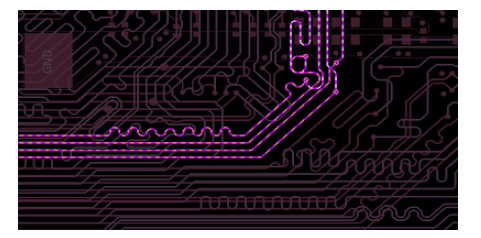

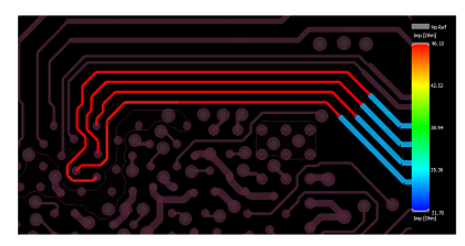

在即將到來的示例中,我們將研究如何為現(xiàn)有布局中的一組網(wǎng)絡(luò)定義和檢查阻抗約束。我們要檢查的四個(gè)網(wǎng)如下所示。這四個(gè)網(wǎng)絡(luò)是DDR3數(shù)據(jù)總線的一部分,并且需要具有34 Ohm的定義阻抗。在這里,我們將檢查這些走線的阻抗是否在JEDEC標(biāo)準(zhǔn)規(guī)定的限制之內(nèi),并且沿著這些走線不會(huì)發(fā)生過多的反射。

四個(gè)阻抗控制網(wǎng)絡(luò)進(jìn)行分析

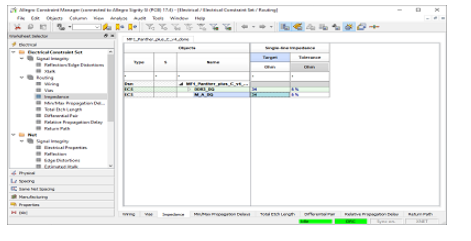

要為網(wǎng)絡(luò)組設(shè)置阻抗約束,請(qǐng)打開“電氣約束設(shè)置”選項(xiàng),然后導(dǎo)航至“路由”→“阻抗”。下圖顯示了此板上定義的兩個(gè)網(wǎng)絡(luò)組。由于兩個(gè)網(wǎng)絡(luò)組都是DDR3接口的一部分,因此該接口上走線的阻抗應(yīng)設(shè)置為34歐姆。阻抗容差已設(shè)置為5%。

網(wǎng)絡(luò)組的阻抗約束

我們要檢查的四個(gè)跡線不是這些網(wǎng)絡(luò)組的一部分,但是如果需要,我們可以將這些跡線分配給這些網(wǎng)絡(luò)組。另一個(gè)選擇是在電氣約束集中單獨(dú)定義這些走線的阻抗約束。要應(yīng)用該規(guī)則,只需在約束管理器中向下滾動(dòng)到電氣工作表中的“網(wǎng)絡(luò)”部分。當(dāng)打開“路由”→“阻抗”部分時(shí),您將能夠看到所有網(wǎng)絡(luò)以及它們所屬的組。

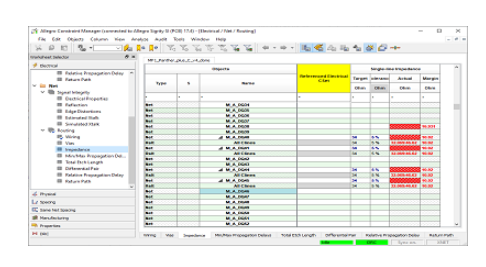

如果要將網(wǎng)絡(luò)分配給電氣間隙組,只需打開“參考電氣C組”列中的下拉菜單,然后選擇所需的電氣間隙組即可。現(xiàn)在,我們將目標(biāo)阻抗值分配給我們要檢查的各個(gè)網(wǎng)絡(luò)。下圖顯示目標(biāo)阻抗設(shè)置為34歐姆(阻抗為5%)。定義目標(biāo)阻抗值后,我們會(huì)看到網(wǎng)絡(luò)標(biāo)記為紅色。如果網(wǎng)絡(luò)沒有立即標(biāo)記,只需從工具欄運(yùn)行設(shè)計(jì)規(guī)則檢查(在“工具”菜單下選擇“更新DRC”)。

單個(gè)網(wǎng)絡(luò)的阻抗約束

在上圖中,這四個(gè)網(wǎng)絡(luò)標(biāo)記為紅色,因?yàn)樨灤┻@些網(wǎng)絡(luò)的最小值和/或阻抗值均超出34±5%范圍(32.3至35.7歐姆)。約束管理器顯示阻抗范圍為32.069歐姆至46.62歐姆;這些值可以出現(xiàn)在這些網(wǎng)上的任何地方。這可能是由于與其他導(dǎo)體的意外寄生耦合,走線寬度的變化或在參考平面上的間隙上布線引起的。

一旦確定了違反設(shè)計(jì)規(guī)則的網(wǎng),就可以更詳細(xì)地了解設(shè)計(jì)中哪些部分違反了設(shè)計(jì)約束。查看約束違規(guī)的另一種方法是使用“工具”菜單中的DRC瀏覽器。這將顯示您在板上違反設(shè)計(jì)約束的坐標(biāo),并將標(biāo)記不同類別中的特定約束違例。

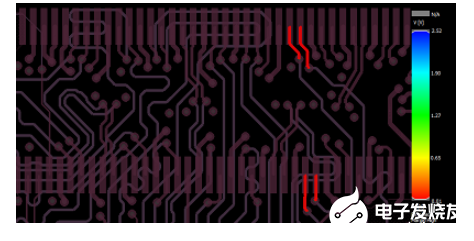

首先,選擇“反射工作流”和要檢查的網(wǎng)絡(luò)。選擇網(wǎng)絡(luò)后,單擊“開始分析”以開始仿真。模擬器完成后,您可以單擊“反射視覺”以查看熱圖,該熱圖標(biāo)記選定網(wǎng)絡(luò)中反射的位置。您也可以單擊反射表以查看特定的過沖/下沖值及其在面板中的坐標(biāo)。由于我們正在處理此板上的DDR線,因此可以將這些值與反射表中的JEDEC規(guī)范進(jìn)行比較。

下圖顯示了我們正在檢查的四組網(wǎng)的反射結(jié)果。從此圖像中,我們看到反射主要發(fā)生在元件焊盤上。這些值以紅色標(biāo)記,僅產(chǎn)生?10 mV的回鈴。30 mV的回鈴在互連上較早出現(xiàn),并且不能通過Reflection Vision工具輕松看到。您需要雙擊阻抗表中的相應(yīng)條目以查看這些結(jié)果。

反射工作流結(jié)果

沿著這些網(wǎng)絡(luò)的30 mV回鈴發(fā)生在較早圖像中所示的長(zhǎng)度匹配段附近的多個(gè)點(diǎn)。阻抗工作流分析可以幫助您解釋這些反射是由于沿互連線的阻抗變化而引起的,從視覺上看,這些變化將變得更加明顯。

要檢查阻抗變化,請(qǐng)?jiān)诜治龉ぞ邫谥羞x擇“阻抗工作流程”選項(xiàng)。選擇相同的網(wǎng)絡(luò)以分析并運(yùn)行仿真。可以通過選擇“阻抗視覺”選項(xiàng)來查看整個(gè)互連的阻抗,該選項(xiàng)將再次顯示帶有顏色編碼阻抗值的熱圖。

四網(wǎng)阻抗變化

從這里,我們可以立即看到阻抗從?46 Ohms突然轉(zhuǎn)變?yōu)?34 Ohms的位置,從紅色部分和藍(lán)色部分之間的長(zhǎng)度變化,這應(yīng)該顯而易見。這對(duì)應(yīng)于這些網(wǎng)絡(luò)中具有較高過沖的區(qū)域。在這里,下一步是將信號(hào)過沖和阻抗變化與信令標(biāo)準(zhǔn)進(jìn)行比較。這些網(wǎng)絡(luò)的紅色部分是FPGA上BGA扇出的一部分,因此,限制扇出部分的寬度會(huì)受到限制,以防止過多的反射和損耗。

上面顯示的相同模擬步驟可用于檢查電路板上的不同對(duì)網(wǎng)。您只需要選擇該對(duì)的兩端即可確保整個(gè)電路板上的差分阻抗保持一致。對(duì)于差分對(duì),您還需要檢查與長(zhǎng)度匹配公差的一致性,可以約束管理器中定義長(zhǎng)度匹配公差。然后,可以使用DRC瀏覽器來確定發(fā)生長(zhǎng)度匹配沖突的位置,并且路由工具將使您可以應(yīng)用標(biāo)準(zhǔn)長(zhǎng)度匹配段,以使差分對(duì)保持同步。

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1629文章

21746瀏覽量

603756 -

pcb

+關(guān)注

關(guān)注

4319文章

23108瀏覽量

398185 -

控制網(wǎng)絡(luò)

+關(guān)注

關(guān)注

0文章

27瀏覽量

9540 -

阻抗控制

+關(guān)注

關(guān)注

1文章

55瀏覽量

10652

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于工作流技術(shù)的廣州電信本地計(jì)費(fèi)系統(tǒng)改造

基于Notes的OA工作流引擎的設(shè)計(jì)和實(shí)現(xiàn)

基于角色的安全工作流模型

基于案例推理的工作流異常處理研究

企業(yè)工作流機(jī)模型的設(shè)計(jì)

OA系統(tǒng)中工作流引擎的設(shè)計(jì)

一個(gè)基于工作流的web服務(wù)組合系統(tǒng)

基于UML的工作流引擎的設(shè)計(jì)與研究

基于活動(dòng)網(wǎng)絡(luò)圖的工作流模型研究

基于工作流的生產(chǎn)管理系統(tǒng)研究與設(shè)計(jì)

基于工作流的遙感數(shù)據(jù)存檔系統(tǒng)

動(dòng)態(tài)工作流技術(shù)的應(yīng)用研究

基于行為特征的語義工作流修正算法

推薦兩個(gè)工作流的springboot項(xiàng)目

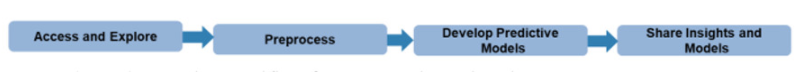

成功構(gòu)建文本分析工作流的四個(gè)步驟

四個(gè)阻抗控制網(wǎng)絡(luò)及反射工作流結(jié)果分析

四個(gè)阻抗控制網(wǎng)絡(luò)及反射工作流結(jié)果分析

評(píng)論