設備或組件可以保持在可接受的范圍內,則功能,性能和生命周期都會增加。如果設備或組件要保持在可接受的范圍內,則必須首先了解這些限制是什么。舉個例子,我的一位同事無法理解為什么他與電容器串聯的保險絲反復失效。

經進一步審查,罪魁禍首是建議保險絲的安培數(裕度)貼錯標簽。事實證明,該板顯示20安培,但建議的安培數為40安培。他通過研究原理圖發現了這一發現。利潤和對它們的遵守在功能,性能和耐用性中起著至關重要的作用。這包括CMOS反相器中的噪聲容限。

噪聲裕度和CMOS特性

在電氣工程領域,可以代數地將無噪聲的最壞情況下的輸入電平代數加到不引起輸出電壓偏離允許的邏輯電壓電平的外部信號的最大電壓幅度稱為噪聲裕度。在通信系統工程領域,我們通常以分貝(dB)為單位測量噪聲容限。

此外,我們將噪聲容限定義為信號超過最小可接受量的比率。關于數字電路,噪聲容限是信號超過產生“ 1”或“ 0”所需的閾值的量。

CMOS代表互補金屬氧化物半導體。其制造過程包括使用互補且對稱的p型和n型MOSFET對來實現邏輯功能。該技術正用于IC(集成電路)芯片,微控制器,CMOS BIOS,微處理器,存儲芯片和其他數字邏輯電路的構造中。

我們還可以發現CMOS技術在諸如數據轉換器,RF電路,高度集成的收發器(通信)和圖像傳感器等模擬電路中的使用。總體而言,CMOS器件的兩個基本特征是低靜態功耗和高抗噪性。

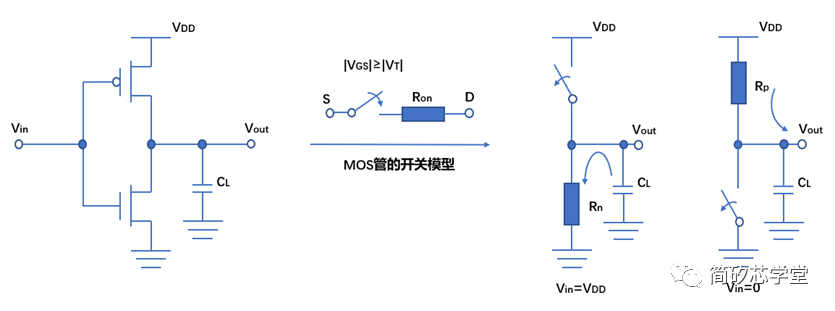

由于一對MOSFET始終處于關斷狀態,因此串聯組合僅在開關狀態(開和關)時瞬間消耗大量功率。結果,CMOS器件產生的熱量通常比其他形式的邏輯(例如TTL)產生的熱量少,即使它不改變狀態,該邏輯通常也具有恒定電流。

CMOS反相器的特性

CMOS技術輕松集成到芯片邏輯和VLSI芯片中。此外,它們以較高的速度運行,同時保持極少的功率損耗特性。此外,CMOS反相器提供了出色的邏輯緩沖功能,因為它的高和低噪聲容限同等重要。

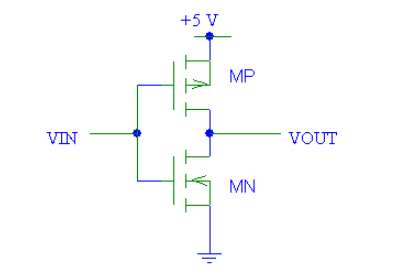

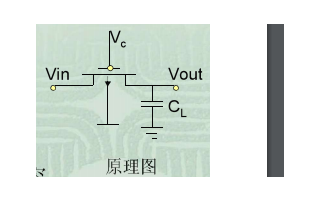

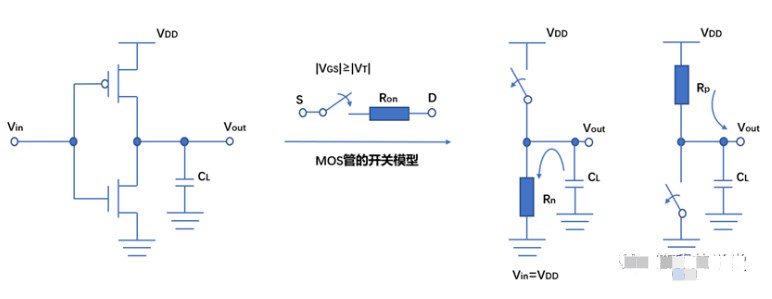

現在,讓我們仔細看一下CMOS反相器的工作原理及其特性。首先,CMOS反相器包含連接到漏極和柵極端子的PMOS(p型)和NMOS(n型)晶體管。而且,它在PMOS源極端子上包含電源電壓(VDD),并在NMOS源極端子上包含接地。最后,它具有到柵極端子的VIN連接和到漏極端子的VOUT連接。請記住,CMOS反相器在其設計中沒有使用電阻,因此與標準電阻MOSFET反相器相比,它具有更高的功率效率。

參考上面的CMOS反相器圖,由于CMOS器件輸入端的電壓在5伏和0伏之間變化,因此PMOS和NMOS的狀態將相應地不同。因此,如果將每個晶體管建模為一個由VIN激活的簡單開關,那么毫無疑問,我們可以看到CMOS反相器的功能。

CMOS反相器中的噪聲裕度

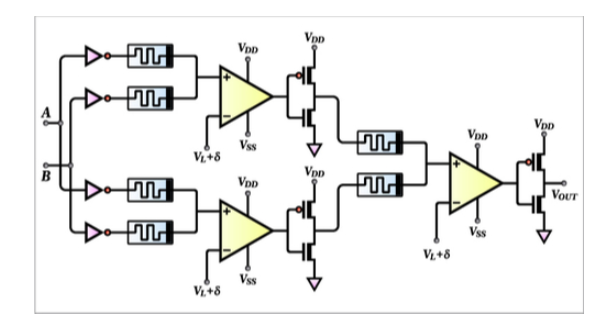

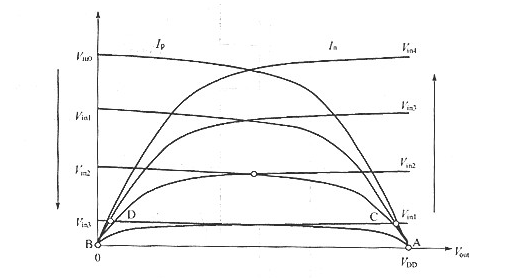

現在,對于純數字反相器,由于存在一定程度的電容,它們不會立即從“ 1”(邏輯高)切換到“ 0”(邏輯低)。當逆變器從邏輯高電平過渡到邏輯低電平時,會有一個不清楚的區域,在該區域中我們無法考慮電壓是低還是高。正是在這一時刻,我們認為這是我們的噪聲余量。

我們必須考慮兩個噪聲容限,它們分別是:高噪聲容限(NMH)和低噪聲容限(NML)。邏輯高電平的驅動設備的最小電壓輸出(VOH min)必須大于邏輯高電平的接收設備的最小電壓輸入(VIH min)。由于導線上存在噪聲,因此驅動設備輸出端的邏輯高信號可能會以較低電壓到達接收設備的輸入端。

因此,邏輯高電平的噪聲容限NMH =(VOH min – VIH min)是您仍然可以正確接收邏輯高電平信號的容差范圍。對于噪聲容限,我們可以說相同,對于邏輯低電平,NML =(VIL max – VOL max),這規定了線路上邏輯低電平信號的容限范圍。噪聲容限越小,表明電路對噪聲越敏感。

噪聲容限是設計容限的標準,可以在特定條件下建立適當的電路功能。噪聲源可以包括電源,運行環境,電場和磁場以及輻射波。片上晶體管的開關活動也會產生不希望的噪聲。因此,為了在特定的噪聲條件下提供適當的晶體管開關,電路的設計必須包括這些特定的噪聲容限。

編輯:hfy

-

CMOS

+關注

關注

58文章

5718瀏覽量

235514 -

MOSFET

+關注

關注

147文章

7164瀏覽量

213307 -

反相器

+關注

關注

6文章

311瀏覽量

43320 -

圖像傳感器

+關注

關注

68文章

1902瀏覽量

129554 -

VLSI

+關注

關注

0文章

73瀏覽量

42916

發布評論請先 登錄

相關推薦

LTC4313的典型應用具有高噪聲容限的2線總線緩沖器

抖頻要要有效降低開關電源EMI噪聲容限的技術

噪音容限,噪音容限是什么意思

MOS反相器和CMOS反相器的詳細資料說明

淺談CMOS反相器中的噪聲容限

淺談CMOS反相器中的噪聲容限

評論