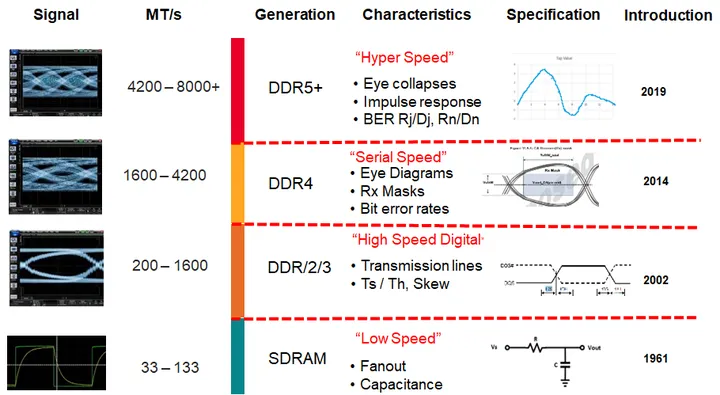

2020年7月,DDR 5新標準誕生,令人興奮的DDR5技術保證了更高的數據速率和更低的功耗。這是接口設計人員熟悉的承諾。但是,就像生活中的大多數事情一樣,沒有免費的午餐。降低功耗和提高速度的進步伴隨著設計復雜性的增加。 DDR5與前幾代產品之間最顯著的區別是判決反饋均衡的引入,這是串行鏈路系統中用于改善接收信號完整性的一項技術。

隨著新技術的發展,本文將研究DDR5上下文中的一些基本信號完整性概念。第一部分介紹了眼圖:確定信號完整性的指標。第二部分通過檢查單脈沖響應來描述信號完整性問題的根本原因。第三部分規定了信號完整性發生問題時的解決方案。

眼圖確定信號完整性

眼圖是評估通道信號完整性的主要指標。它是通過對通道接收的偽隨機二進制序列(PRBS)的適當處理而創建的。為了在存儲器操作的“寫”周期的上下文中創建眼圖,控制器(發送器)通過通道發送PRBS到達存儲器模塊(接收器)。在存儲模塊上接收到的PRBS模式被劃分為具有相同時間間隔的段。然后將具有相同時間間隔的這些片段彼此堆疊以創建眼圖。

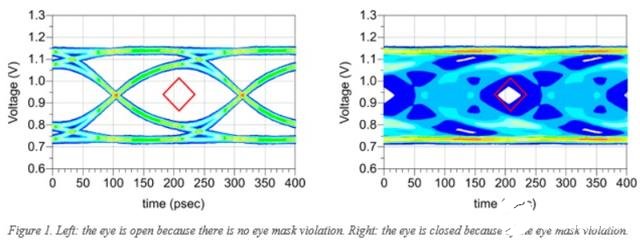

在圖1中,有兩個藍色的眼圖和紅色的眼圖模板。通過將通道輸出端的眼圖與模板進行比較,可以確定通道的信號完整性。模板是接收閾值的圖形表達。模板顯示對于給定的誤碼率(BER),接收信號的可接受時序和幅度。

如圖1左側所示,眼睛是張開的。當輸出眼圖和眼圖模板之間沒有重疊時,該通道具有良好的信號完整性。如果輸出眼圖與模板不重疊,則接收器可以根據接收到的模擬電壓電平和時序確定數字1或數字0。另一方面,如果存在違反模型的情況(如圖1右側所示),則眼睛會閉合,接收器無法區分數字1或數字0。

眼圖為工程師提供了給定通道性能的指標。當接收器的眼睛合上時,需要其他分析技術來確定閉眼的根本原因。

DDR5中的頻率相關損耗和反射

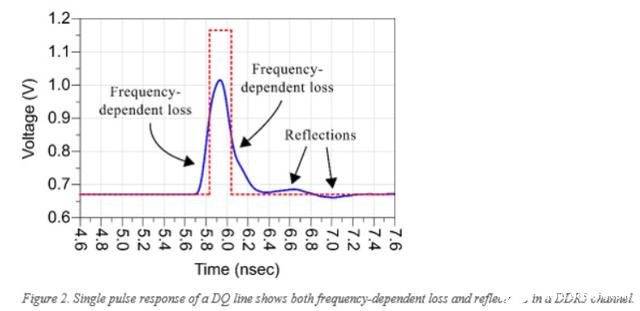

DDR5標準中指定的主要問題是反射和與頻率有關的損耗[1]。圖2顯示了從控制器到存儲模塊的DQ線的單脈沖響應。單脈沖響應是從控制器發送單脈沖(數字脈沖)時在存儲模塊上接收到的波形。

在圖2中,紅色虛線是通道中沒有反射或與頻率相關的損耗的理想情況。以藍色表示,隨著理想脈沖的擴展,觀察到通道的頻率相關損耗。通道中的反射會在稍后出現。由于單個脈沖的擴散和反射會干擾其他脈沖,因此人們常將其稱為符號間干擾(ISI)。

由頻率相關損耗引起的ISI在串行鏈路通道中很常見,而由阻抗不連續性引起的反射問題則是DDR特有的。

DDR5中的決策反饋均衡

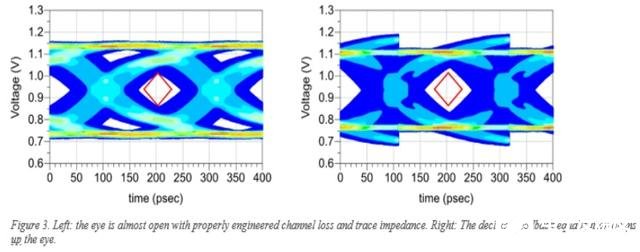

如果信號完整性問題的根本原因是與頻率有關的損耗,那么最直接的解決方案是減少通道的長度或在制造過程中使用低損耗的材料。為了使反射量最小,走線應設計為可控阻抗。如果通過適當的通道長度,制造材料和阻抗控制使眼圖保持閉合,則接收器處的均衡可以幫助進一步改善/張開接收器中的眼圖。

在DDR5中,指定了四抽頭決策反饋均衡(DFE)來減輕損耗和反射,而不放大噪聲。每個抽頭代表一個單位間隔,四抽頭DFE在當前接收的比特之后最多校正四個單位間隔。顧名思義,決策反饋均衡算法對每個接收到的比特做出決策,并將比特的修改反饋給接收器。

在DFE算法中,接收到的模擬波形首先到達符號檢測器。符號檢測器確定接收到的模擬波形代表數字1還是數字0。如果檢測到的符號是數字符號,則模擬波形的縮放版本將是加入原始數字以強調下一個數字0。如果檢測到的符號是數字0,則將模擬波形的縮放版本添加到原始波形中,以強調下一個數字1。

圖3的左側顯示了幾乎閉合的眼圖。通過應用DFE,幾乎可以閉眼。如圖3的右側所示,DFE算法成功地打開了幾乎閉合的眼睛圖。 DFE均衡眼圖的另一個獨特功能是睜眼前后的扭結。

隨著數據速率的提高,人們看到了串行鏈路和DDR之間的技術融合。在DDR5之前,無需進行均衡即可使接收器處的像樣張開。隨著對更高速度和更低功耗的推動,均衡已經成為適當睜眼的必要條件。

盡管在接收器處配備一個均衡器以改善眼圖是令人欣慰的,但仍然需要適當地設計信道損耗和走線阻抗,以便均衡可以對系統性能產生最積極的影響。

為了更好地理解不同通道設計和均衡功能之間的平衡,使用電子設計自動化(EDA)軟件作為虛擬原型環境驗證也已成為必需。通過將虛擬樣機的結果和實際設計的測量結果相結合,可以形成一個強大的設計工作流程,以應對新的令人興奮的技術。

編輯:hfy

-

DDR

+關注

關注

11文章

712瀏覽量

65431 -

信號完整性

+關注

關注

68文章

1413瀏覽量

95557 -

DDR5

+關注

關注

1文章

426瀏覽量

24187

發布評論請先 登錄

相關推薦

DDR3、DDR4、DDR5的性能對比

DDR5內存與DDR4內存性能差異

DDR5內存的工作原理詳解 DDR5和DDR4的主要區別

揭秘DDR5的讀寫分離技術奧秘

順絡電子推出DDR5電感新方案,助力高效普及

SK海力士DDR5芯片價格或將大幅上漲

Introspect DDR5/LPDDR5總線協議分析儀

DDR5 MRDIMM內存標準將發,存儲廠商方案先行

DDR5內存條上的時鐘走線

0706線下活動 I DDR4/DDR5內存技術高速信號專題設計技術交流活動

Rambus通過全新PMIC系列支持多代基于 DDR5 的高性能服務器

談談DDR5技術規格的那些事

DDR5測試技術更新漫談

DDR5內存接口芯片組如何利用DDR5 for DIMM的優勢?

DDR5的基本信號完整性 DDR5頻率相關損耗和反射

DDR5的基本信號完整性 DDR5頻率相關損耗和反射

評論