翻譯自——newelectronics

摩爾定律已經不能用了嗎?其實這取決于哪一方面。

斯坦福大學電氣工程教授Philip Wong與來自麻省理工學院、臺積電、加州大學伯克利分校的研究所的同事一起,寫了一篇關于硅尺度化進展的論文。文中指出,技術人員不應該僅僅關注晶體管間距的縮放面積,而應該關注每個連續節點的有效密度。

看看其他因素,芯片制造業正在回歸基本。在1975年國際電子設備會議(IEDM)上的演講中,英特爾的執行官Gordon Moore決定用兩年的時間將設備密度定期提高一倍。在那之前,這個行業一直在以更快的速度發展,每年翻一番。到1975年,摩爾已經看到進步的速度在下降。

Moore認為二維幾何縮放只是在同等成本下實現雙倍功能的一部分。他認為這是相當大的一部分,但肯定不是全部。他預測,芯片尺寸的顯著增加和電路設計的改進將滿足剩下的要求。然而,那時的晶圓廠才剛剛開始利用IBM研究員羅Robert Dennard注意到的比例因素: 更小、更緊湊的晶體管不僅可以實現成本改進,還可以實現能源改進。

上世紀80年代向CMOS的轉變加速了這一進程,直到本世紀頭十年中期,行業耗盡了Dennard規模化的大部分好處。在那之后,簡單的2D縮放將變得越來越麻煩。

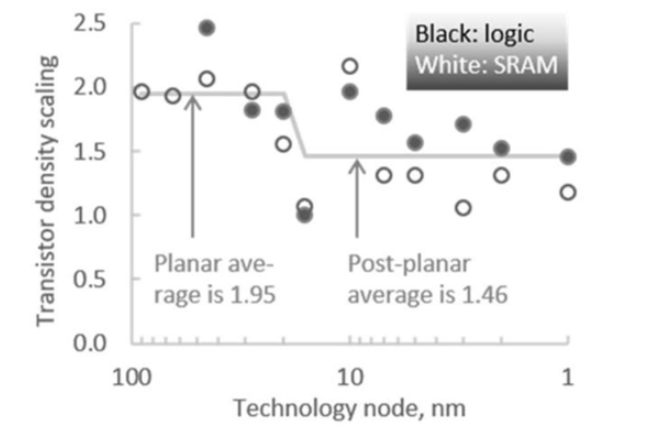

這在最近幾年SRAM的擴展趨勢中最為明顯,從歷史上看,SRAM擴展一直是密度改進的良好指南。雖然它在邏輯上一直保持了28nm的步伐,但隨后就開始落后了,因為在金屬間距和晶體管尺寸不一樣的情況下,它很難做出增量的改進。

電路的進化

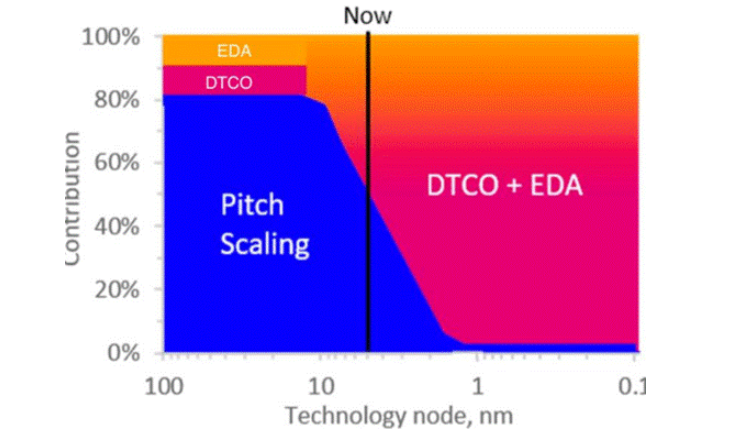

EDA工具供應商Synopsys將在IEDM上做一個演示。它將展示在過去的幾年里,對縮放的貢獻是如何改變的。

Moore所稱的“電路智慧(Circuit cleverness)”已經卷土重來,盡管與最初提出的形式有所不同。這一次,它的名字是設計-技術協同優化(DTCO)。通過讓設計人員就電路布局最合理的工藝變更提供建議,工藝工程師可以做出更好的權衡。這一點在SRAM的比例變化中顯而易見,由于晶圓布局的變化,密度出現了明顯的躍升。

Wong和Synopsys團隊認為,DTCO是未來10年實現1nm節點的關鍵因素。但是純維度縮放還沒有完全消失。雖然二維縮放的空間不大,但是三維縮放很有潛力,而不一定是像HBM這樣的內存標準那樣堆疊芯片。你可以潛移默化地把它當成3D。

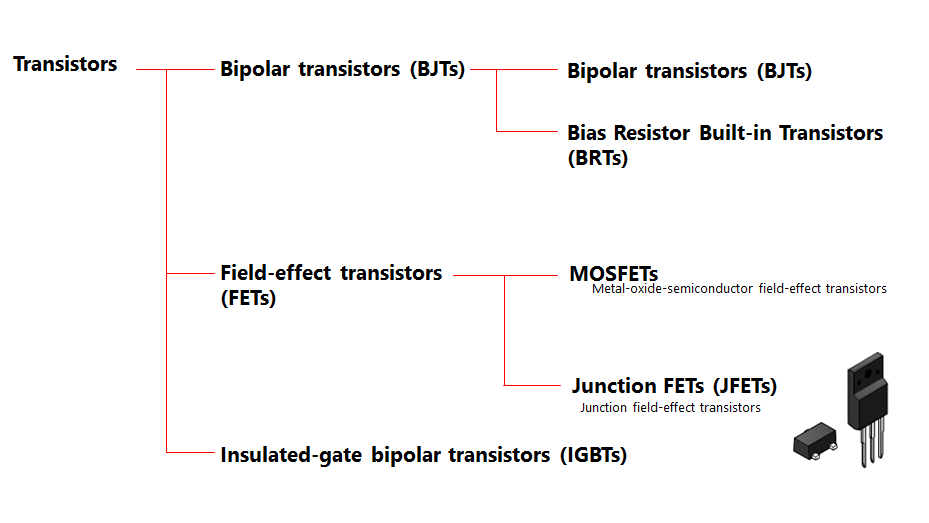

利用垂直尺寸的一種方法是將晶體管側轉。這將繼續場效應晶體管的發展,從一個純平面器件,通過FinFET的垂直與頂部柵極接觸。通過將柵極包裹在晶體管的三面,鰭片對晶體管通道提供了更強的靜電控制。但超過5納米,需要全環繞柵極結構(Gate-All-Around FET)。實際上,通過柵極的nanosheet可以滿足這一要求。更妙的是,盡管這增加了過程的復雜性和成本,但你可以通過堆疊nanosheet來獲得更多的驅動電流,就像FinFET通常使用兩個或更多的鰭片一樣。堆疊可能比multifin結構消耗更少的區域。

對于FinFET來說,它應該是較為先進的晶體管。在每一代新技術中,芯片制造商都能將晶體管規格縮小0.7倍,在器件層面上實現15%的性能提升、50%的面積增益、40%的功耗降低和35%的成本降低。幾年前,業界為了維持這種微縮路徑,從“老式”的平面MOSFET過渡到FinFET晶體管架構。在FinFET中,源極和漏極之間的溝道呈鰭狀。柵極環繞這個3D溝道,從溝道的3個側面進行控制。這種多柵極結構可以消除短溝道效應,短溝道效應會在柵極長度縮短時降低晶體管的性能。出色的短溝道控制至關重要,因為它為器件微縮奠定了基礎——允許更短的溝道長度和更低的工作電壓。

2012年,首批商用22nm FinFET問世。從那時起,FinFET架構得到了改進,以提高性能和減少面積。例如,FinFET的3D特性允許增加鰭片高度,從而在相同的封裝面積上獲得更高的器件驅動電流。如今,工業界正在加緊生產“內含”FinFET的10nm/7nm芯片。在最先進節點的單元層面,標準單元的Track高度為6T(這是單元面積的量度標準),每個器件的鰭片數量低至2個。

垂直堆疊的nanosheet:進化的一步

但隨著微縮至5nm以下,預計FinFET將失效。在減小柵極長度時,FinFET結構反過來不能提供足夠的靜電控制。除此之外,向更低Track高度標準單元的演進需要向單鰭片器件過渡,即使鰭片高度進一步增加,單鰭片器件也不能提供足夠的驅動電流。

然而,隨著技術節點的變化,半導體行業并不急于轉向其他晶體管架構。一些公司甚至決定在某些節點上停留更長時間。但仍有一些應用——如機器學習、大數據分析和數據中心服務器——需要最新的“通用”CMOS解決方案。利用這種通用的CMOS解決方案,在同一個技術節點中的同一個晶體管結構可以用于執行芯片上的所有功能。

此處,垂直堆疊的nanosheet晶體管可以救急。它們可以被認為是FinFET器件的自然進化。想象一下,將一個FinFET側放,然后將其分成獨立的水平薄片,這些薄片構成了溝道。現在,一個柵極完全環繞在溝道上。與多柵極FinFET相比,nanosheet的這種柵極全包的特性提供了更出色的通道控制能力。同時,溝道橫截面在3D體積中的更優化分布,優化了單位面積的有效驅動。

nanosheet縮放的障礙是需要在CMOS對的n道和p道器件之間進行分離。但Imec去年提出了forksheet。這是由一個共同的支柱組成的,n和p摻雜的薄片相互疊加。與此同時,你有一個完整的CMOS反相器內置在單晶體管結構,節省了大約30%的面積。

從邏輯單元中獲取能量會占用有價值的區域。Imec在2018年超大規模集成電路(VLSI)研討會上的提議是將電力軌道埋在硅表面。下一步是CFET(納米薄片場效應晶體管): nFET和pFET共用一個柵電極作為信號輸入端,共用一個漏極作為信號輸出端,源電極分別接地和供電電源。器件尺寸可靈活調節以滿足不同芯片性能要求。

在即將到來的IEDM上,英特爾的工程師將描述他們對基于nanosheet的CFET型結構的看法。組合晶體管使用外延來構建一個垂直堆疊的源極漏極結構,其閾值電壓為這兩種晶體管單獨調優。雖然這項工作中的柵極在30nm左右相對較長,英特爾團隊希望通過自對齊堆疊實現顯著的晶圓尺寸縮小。

根據Synopsys的計算,CFET在SRAM方面做了很多工作,盡管它需要一些DTCO。CFET的一個缺點是,疊加引入了另一種形式的可變性,但同樣,設計調整將有助于解決這一問題。例如,最緊湊的結構并不完全依賴于全環繞柵極結構晶體管。相反,它包含了一個帶有三面柵極的偽p溝道晶體管,以獲得足夠好的寫入行為。

主要問題

即使晶體管密度增加,芯片設計的主要問題是金屬互連中的寄生電阻和電容。這可能會迫使未來的生產工藝從以銅為主要原料轉向更奇特的金屬,如釕。

英特爾提出了一種基于設計的替代方案,即盡管將電阻和電容切割在一起似乎是可取的,但并不是所有的電路路徑都將以同樣的方式受益。

單個路徑可以從單獨調諧的電阻和電容中獲益。這就是指導英特爾在所謂交錯互連上的發現。

這種交錯的方法并不是讓每條平行線都一樣,而是將高、短的線交替排列,短的線排列在更高的絕緣子材料堆上。這降低了線路間的凈有效電容。實際上,高線會受到更多的干擾,而類似的影響會被間隔得更遠。

Synopsys表示,這些受DTCO啟發的設計更加復雜,它將推高晶圓成本:平均每個節點的成本會達到13%。但是有效的密度在1納米節點上仍然是可行的,并且仍然有可能使每個晶體管在每個節點上降低32%的成本。

這已經不是昨天的摩爾定律了,但這一趨勢應該會持續大約十年。有多少公司能夠擁有如此龐大的業務量來證明它是合理的,這仍然是另一個問題。

編輯:hfy

-

CMOS

+關注

關注

58文章

5718瀏覽量

235504 -

電路設計

+關注

關注

6674文章

2453瀏覽量

204361 -

eda

+關注

關注

71文章

2759瀏覽量

173268 -

晶體管

+關注

關注

77文章

9693瀏覽量

138189 -

FinFET

+關注

關注

12文章

248瀏覽量

90230

發布評論請先 登錄

相關推薦

晶體管電流放大器的原理 晶體管在功放電路中的應用實例

NMOS晶體管和PMOS晶體管的區別

什么是單極型晶體管?它有哪些優勢?

晶體管的主要類型有哪些

晶體管的主要材料有哪些

晶體管收音機和半導體收音機哪個好

晶體管,場效應管是什么控制器件

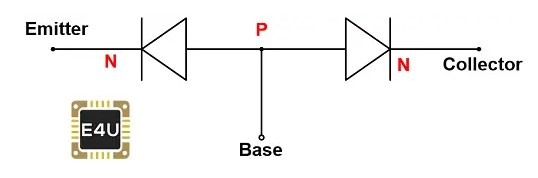

PNP晶體管的工作原理和結構特性

Si晶體管的類別介紹

淺談半導體晶體管間距的縮放面積及連續節點的有效密度

淺談半導體晶體管間距的縮放面積及連續節點的有效密度

評論