本期分享的研究成果是來自西安交大微電子學院在GAA晶體管自熱效應研究模型上的成果,通過提出和驗證聲子邊界反射等現象對自熱效應和熱導率的影響,研究團隊建立了更加精確的物理模型,以便能更好模擬GAA晶體管的實際工作狀態。接下來就請隨小編一起來看看具體的研究內容吧~

研究背景

在集成電路研究領域,從實驗到各種熱電特性模擬的廣泛研究都表明了自熱效應對集成電路器件性能與可靠性的負面影響,尤其是在諸如FinFET和GAA晶體管的多門場效應晶體管管中,由于材料熱導率、晶體管結構、界面熱阻以及10nm以下尺寸器件的高功耗密度等因素的存在,使得先進制程芯片設計變得越來越具挑戰性。

要對晶體管中自熱效應引起的溫度分布進行準確的描述,需要對器件的熱學特性建立精密準確的分析模型。因此,作為探究器件熱可靠性的基礎,針對納米尺度下的熱量產生與分布的理論研究與實驗廣泛開展,發展出了各種不同的分析模型。

近日,西安交通大學微電子學院研究團隊在全環柵(GAA)晶體管的自熱效應研究上取得了新進展,其研究成果以“Study on Degradation Mechanisms of Thermal Conductivity for Confined Nanochannel in Gate-All-Around Silicon Nanowire Field-Effect Transistors”發表于IEEE Transactions on Electron Devices,博士研究生賴俊華為本文的第一作者,西安交大張國和教授與中科院微電子所卜建輝研究員為本文的共同通訊作者。

基本特性

研究團隊提出了一種考慮納米通道截面和長度的熱導率分析模型,用于精確模擬GAA硅納米線晶體管中的自熱效應,并得到了實驗數據的驗證: 納米通道長度引起的熱導率下降通過橫向聲子的等效平均自由程來描述,其結果顯示,相比完全耗盡型SOI(以下簡稱:FD-SOI)晶體管中的超薄硅,GAA硅納米線晶體管的熱導率下降幅度大得多,隨著納米通道長度的減少,熱導率顯著降低,這個現象在建立自熱效應研究模型時需要著重考慮。

模型建立與解析

為了更準確的評估器件的自熱效應,團隊在建立FD-SOI場效應管模型上做了大量工作,在現有模型的基礎上,進一步引入自由態和束縛態電子的散射機制以及聲子邊界反射等影響因子,并揭示了3D晶體管器件的熱導率在縱向坐標的相關性。接下來是一些相關的結構原理圖和測試結果圖。

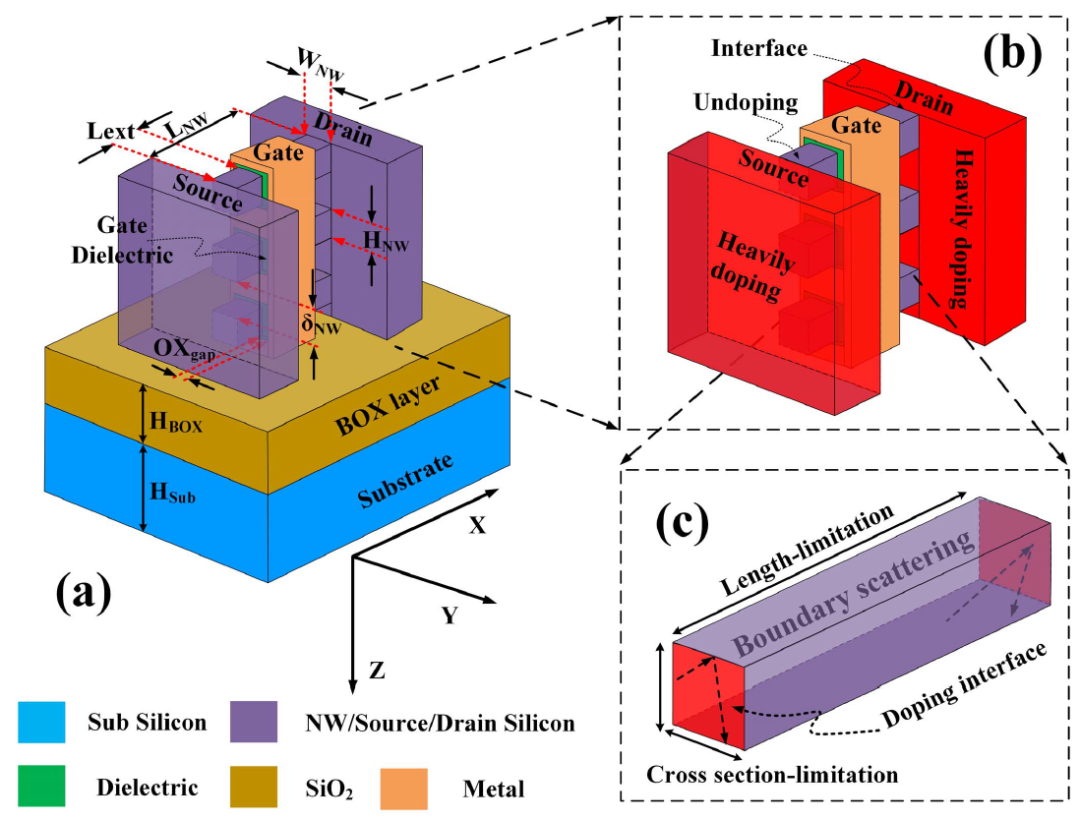

圖(a)GAA納米線晶體管原理圖及對應坐標系和物理參數;圖(b)摻雜剖面;圖(c)受溝道限制的聲子散射邊界

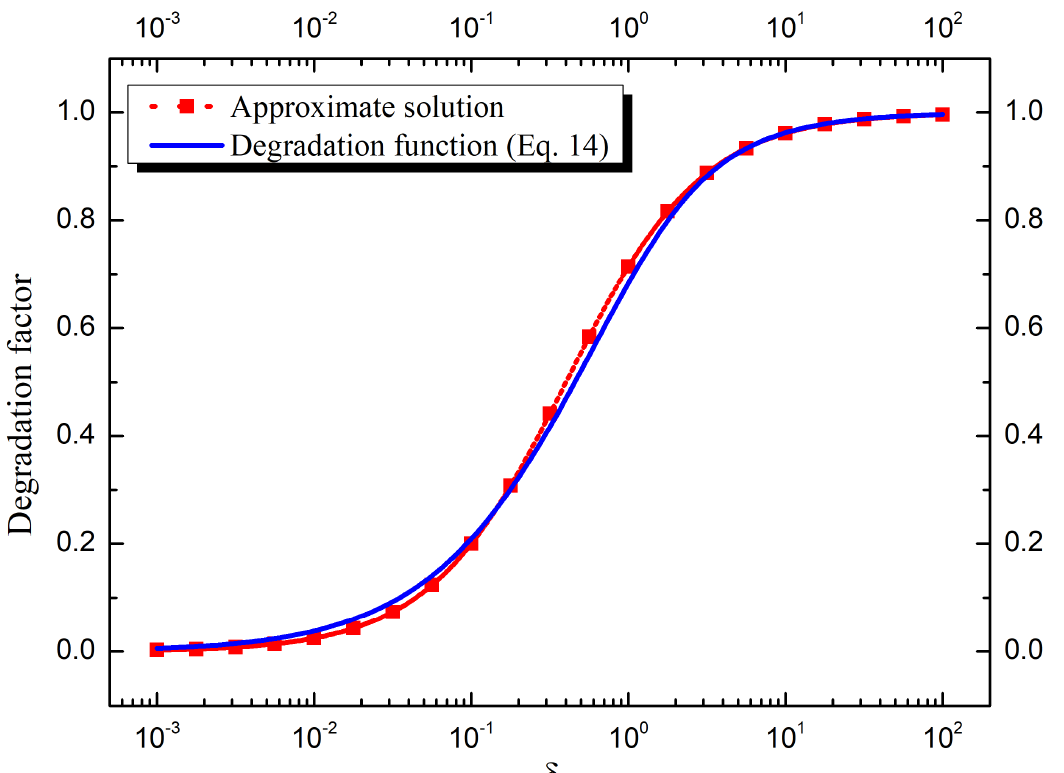

FD-SOI晶體管熱導率的變化函數及其近似解

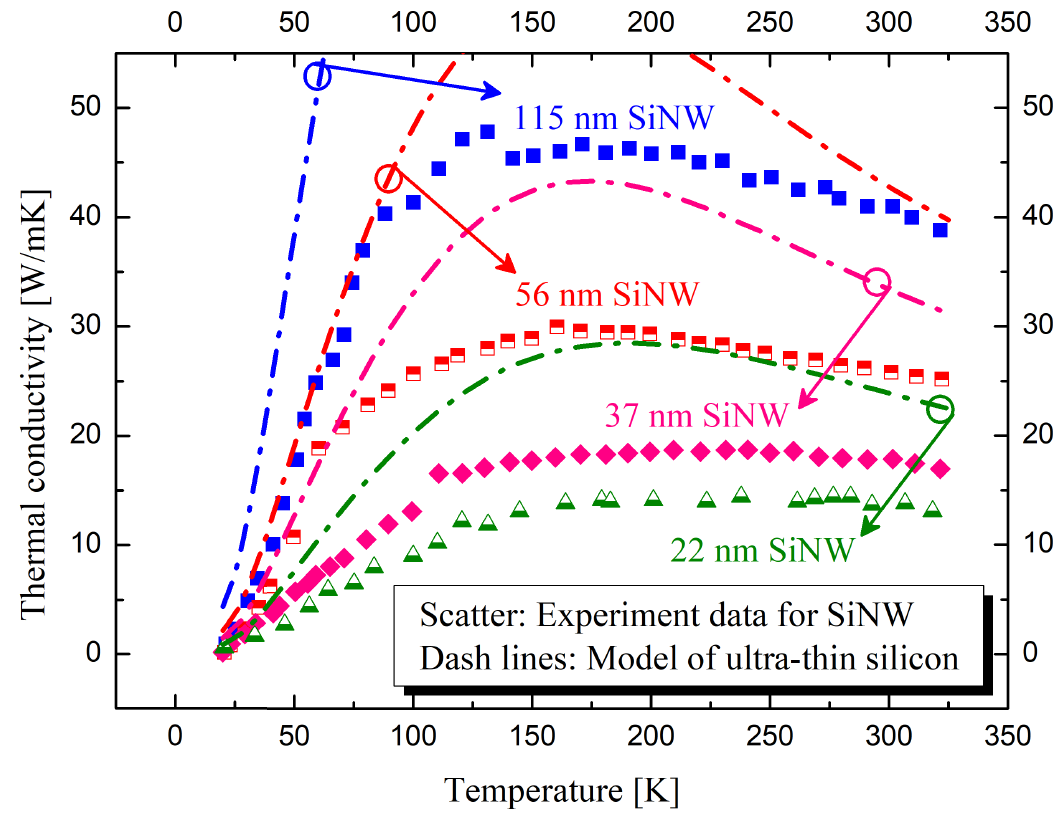

FD-SOI晶體管的超薄硅膜通道與硅納米線通道的熱導率變化曲線對比

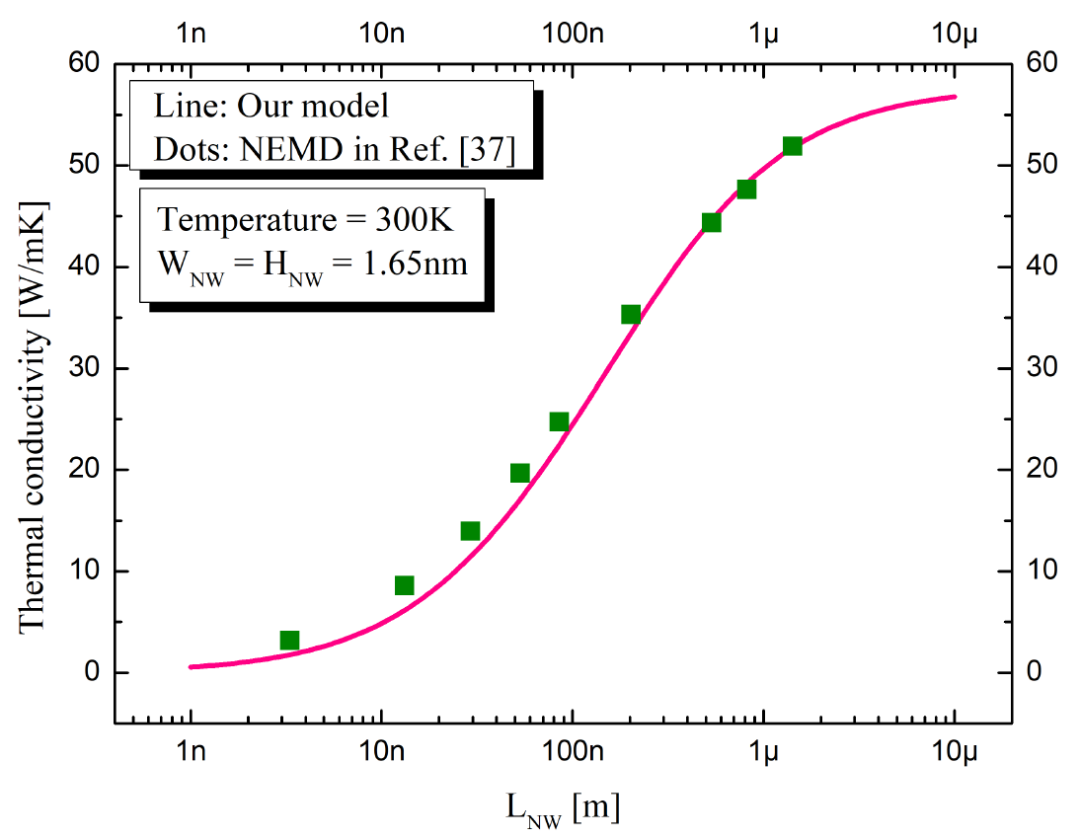

受納米通道長度引起的納米通道導熱率變化對比:GAA納米線測試結果與非平衡態分子動力學模擬結果對比

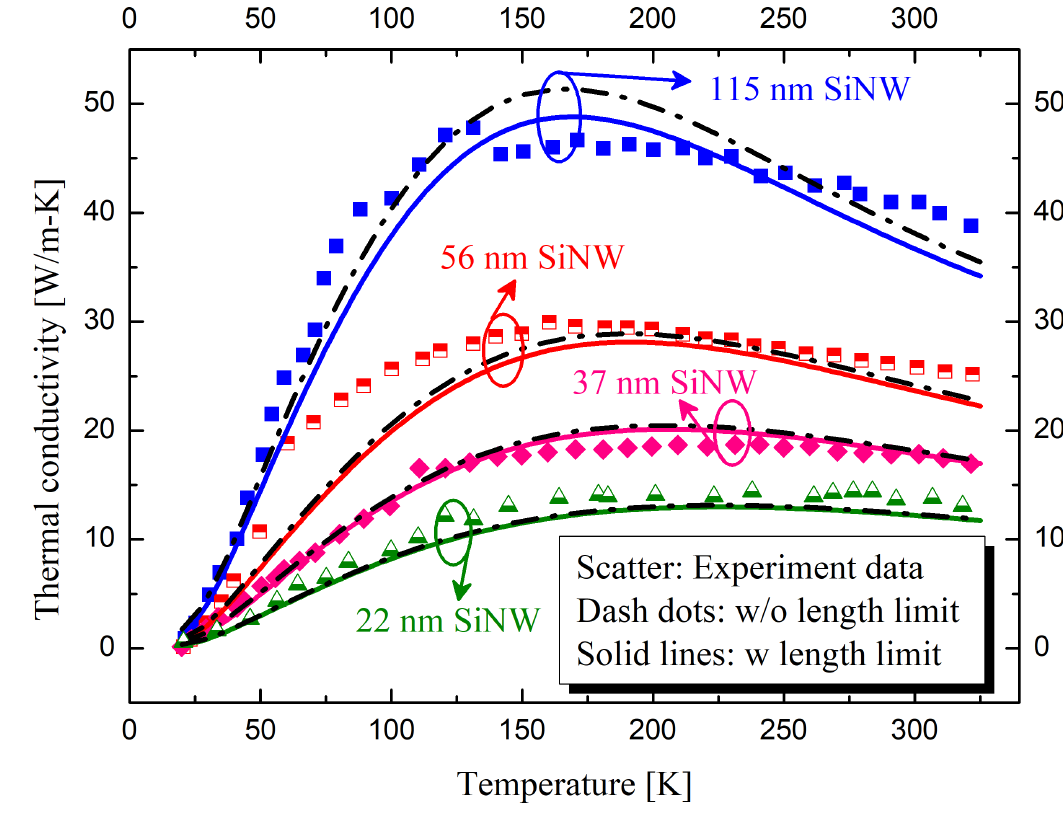

不同尺寸下的納米通道在有/無通道長度限制影響條件下的熱導率變化曲線

上圖結果表明,考慮納米通道長度限制后,導熱系數的預測值整體出現降低。隨著通道長度逐漸接近截面尺寸,通道長度的限制會導致熱導率的大幅減小。

應用前景

作為制約摩爾定律延續因素之一的自熱效應,其存在對于器件性能與壽命有著很大的影響,本成果針對GAA納米晶體管自熱效應特性模型的創新研究,完善了熱導率物理模型,有望為緩解GAA納米線晶體管工藝中的發熱問題以及由此帶來的熱載流子注入等問題,期待該成果能夠幫助芯片制造產業進一步提升工藝水準。

原文標題:科研前線 | 西安交大在GAA晶體管自熱效應分析上取得新進展

文章出處:【微信公眾號:芯片揭秘】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

晶體管

+關注

關注

77文章

9706瀏覽量

138483 -

微電子

+關注

關注

18文章

383瀏覽量

41223

原文標題:科研前線 | 西安交大在GAA晶體管自熱效應分析上取得新進展

文章出處:【微信號:ICxpjm,微信公眾號:芯片揭秘】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

西安交大在GAA晶體管自熱效應研究模型取得新成果

西安交大在GAA晶體管自熱效應研究模型取得新成果

評論