作者:GRL實驗室/曾威華 Wing Tseng

在開始介紹 DDR 之前,首先要了解內存的功用為何。大多數的 3C 產品在運作時,會將正在使用的程式存放到一個短期數據儲存區,該空間即為內存,所以有了內存的運用能使 3C 產品更快速的切換程序以方便使用。

內存的歷史

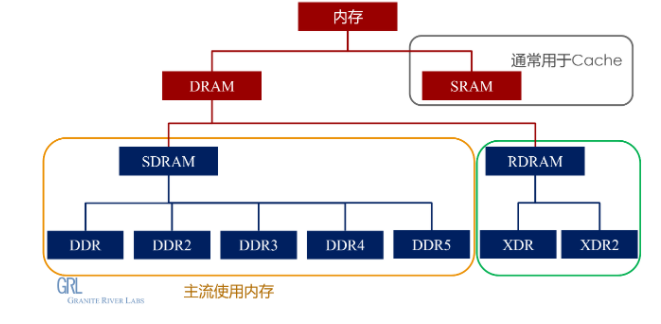

圖一為內存的種類及發展史:

圖一:內存的種類及發展史

內存(Memory)又可分為 DRAM(Dynamic Random Access Memory)動態隨機存取內存和 SRAM (Static Random Access Memory)靜態隨機存取內存兩種。兩種都是揮發性的內存,SRAM 的主要使用 flip-flop 正反器,通常用于快取 (Cache),而 DRAM 則是使用電容器及晶體管組成。RDRAM (Rambus DRAM)因較為少見也非本篇文章主角,其他還有早期的 FP RAM、EDO RAM 也就不多作介紹。

DRAM 中又以 SDRAM(Synchronous Dynamic Random Access Memory)同步動態隨機存取內存在近幾年來最廣為使用,SDRAM 最重要的就是能夠“同步”內存與處理器(CPU)的頻率,讓 SDRAM 頻率可超過 100MHz 使傳輸數據更能實時到位。SDRAM 亦可稱為 SDR SDRAM(Single Data Rate SDRAM)。

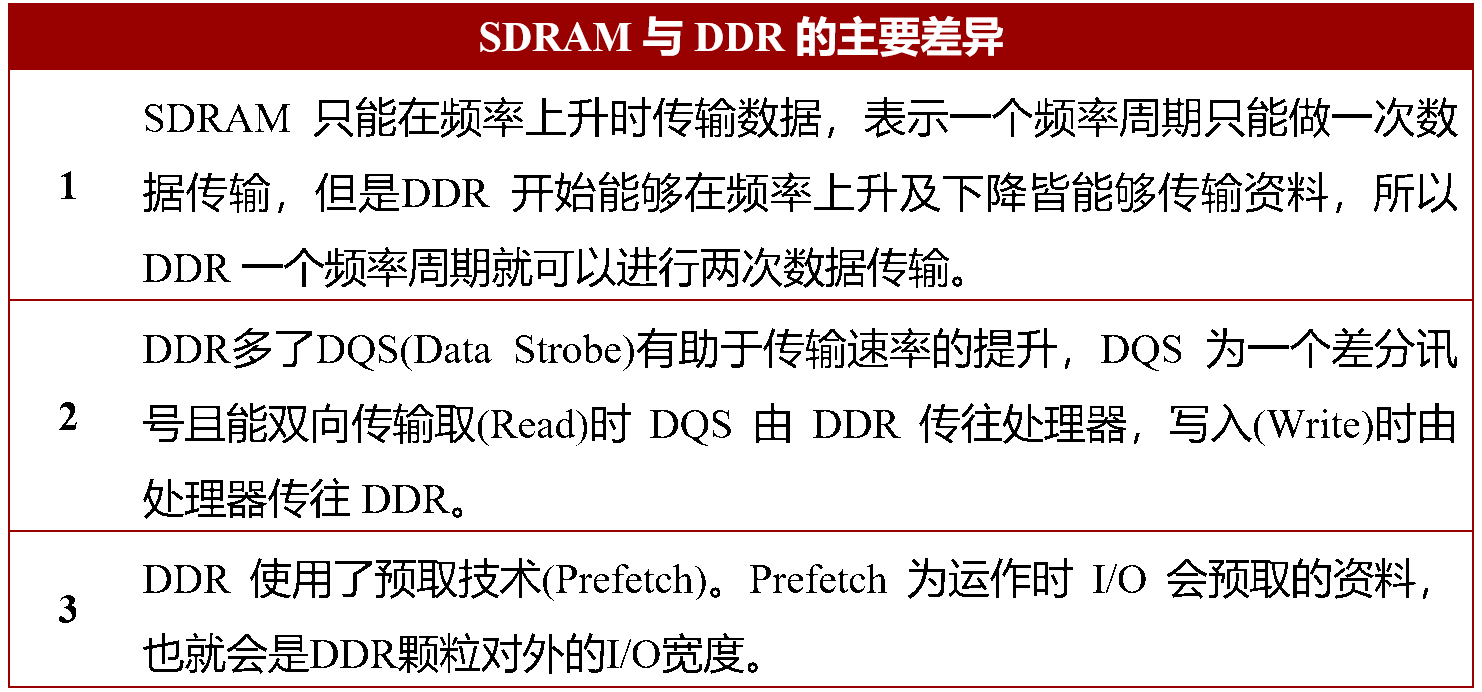

DDR(Double Data Rate)其實指的是 DDR SDRAM(Double Data Rate SDRAM),SDRAM 及 DDR 主要差異有三點整理如下:

目前負責訂定 DDR 規范的協會為 JEDEC(Joint Electron Device Engineering Council),但現在它的全名則是 JEDEC 固態技術協會(JEDEC Solid State Technology Association)。

DDR 歷代規格介紹

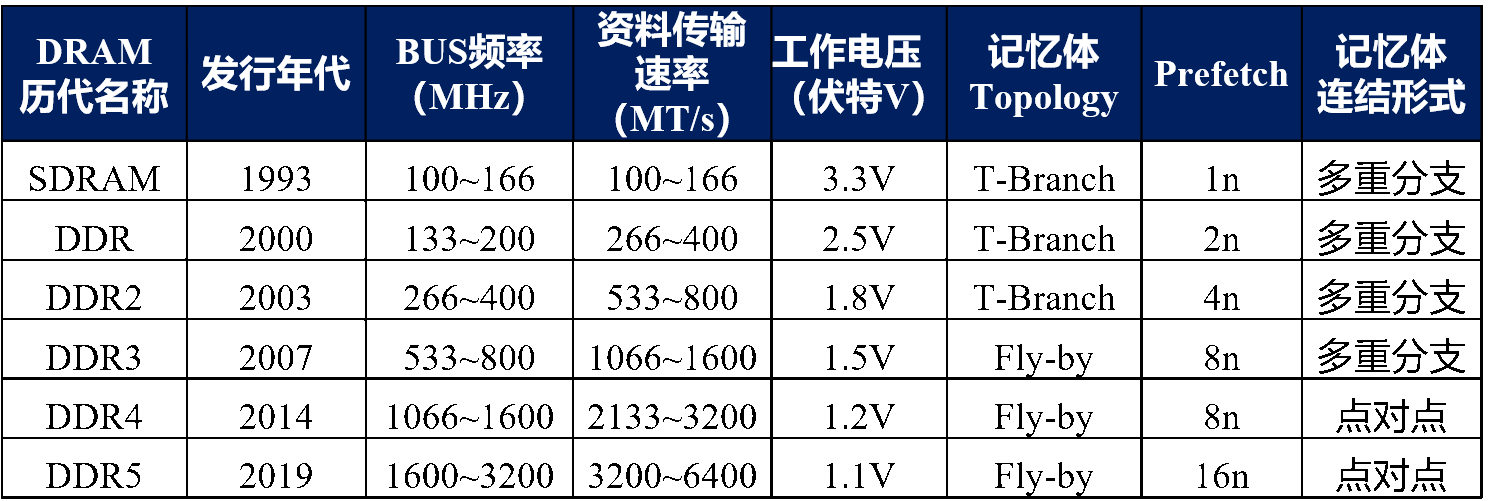

有了內存的認識之后,這邊將歷代 DRAM 的規格整理如下:

歷代演進除了傳輸速率越來越快還有工作電壓越來越低,內存Topology在DDR2之前Command/Address和Clock用T-Branch分支方式傳給每一個內存顆粒,但在DDR3之后 Command/Address和Clock則改用 Fly-by串列給每一個內存顆粒。

另外內存鏈接形式在 DDR3 之前采用處理器(CPU)同時與多個內存芯片控制器鏈接的“多重分支”,但在DDR4 之后每個內存芯片控制器有單獨與 CPU 鏈接的通道,即為“點對點”的連結形式。

DDR 主要訊號介紹

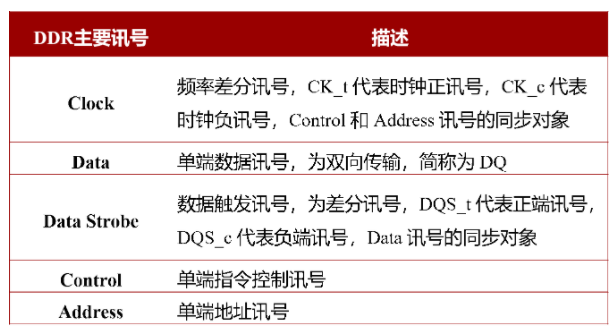

DDR 的訊號類型主要分為以下五種如下:

Note: 讀取(Read)時,DQ 和 DQS 為同相位。寫入(Write)時,DQ 和 DQS 會有 90 度的相位差。

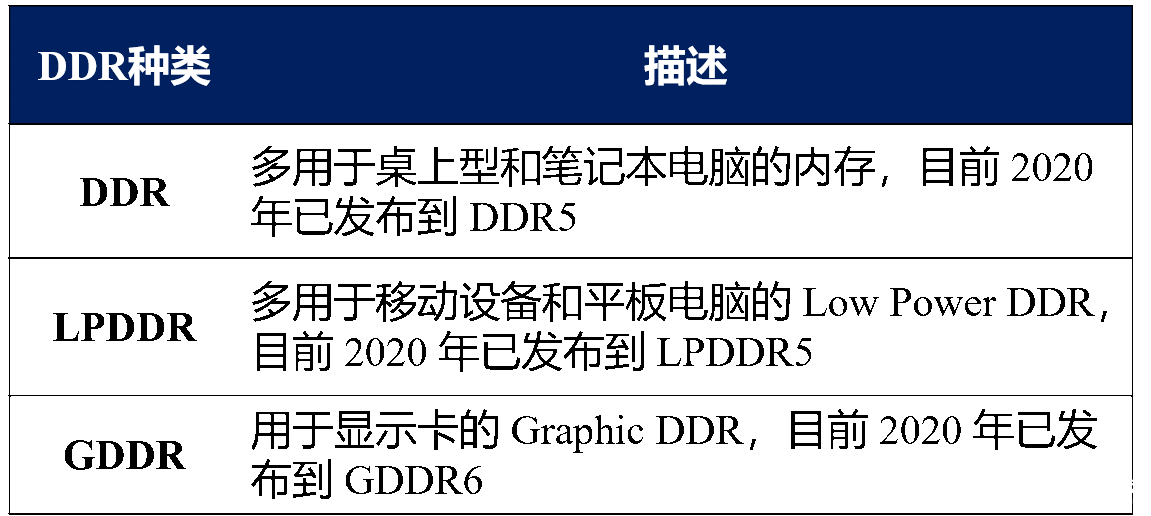

DDR 種類

目前 DDR 種類大致分為以下三種:

最后將 DDR 與 LPDDR 歷代工作電壓值整理:

參考文獻:

Low Power Double Data Rate SDRAM Standard(LPDDR), JESD209B, February 2009

Low Power Double Data Rate 2(LPDDR2), JESD209-2F, April 2011

DDR3 SDRAM Standard, JESD79-3F, July 2010

Low Power Double Data Rate 3(LPDDR3), JESD209-3C, August 2013

DDR4 SDRAM, JESD79-4, September 2012

Granite River Labs, https://graniteriverlabs.com.cn/ddr/

Low Power Double Data Rate 4(LPDDR4), JESD209-4B, November 2015

Low Power Double Data Rate 5(LPDDR5), JESD209-5, February 2019

編輯:hfy

-

處理器

+關注

關注

68文章

19314瀏覽量

230074 -

DDR3

+關注

關注

2文章

276瀏覽量

42299 -

cpu

+關注

關注

68文章

10873瀏覽量

212036 -

DDR

+關注

關注

11文章

712瀏覽量

65372

發布評論請先 登錄

相關推薦

內存的種類及發展史 DDR種類介紹

內存的種類及發展史 DDR種類介紹

評論