在嵌入式裝置中建置多核心(包含同質或異質)以及多執行緒技術,的確能帶來諸多效益,尤其是改進系統效能方面最為明顯。

盡管RISC嵌入式技術所面臨的挑戰越來越多,但是在維持以往嵌入式軟件資源兼容性的前提之下,能夠改善其未來適用性,并且有效提升新系統的效能表現,使其不失為良好的解決方案。

應用決定多核或多緒

多核心與多執行緒在效能表現上有其幫助,但是效能與這些技術的內建其實并沒有絕對關系,會造成這樣的原因主要是應用環境的需求。以手機為例,整合于手機內的SoC芯片雖然是屬于多核心架構的一環,但是手機采用的SoC芯片多為應用處理器,其整合的核心并非完全屬于同性質架構,同質多核心在嵌入式系統實際應用上的案例其實非常少。

而多執行緒處理器在汽車電子或者是嵌入式網絡環境中扮演著重要的角色,但是也有廠商利用數顆多執行緒芯片組成多核心與多執行緒兼備的運算架構,換句話說,兩者并不是單純選邊站而已,根據實際應用的需求,自行搭配或開發最終解決方案也成了許多廠商面對問題時的態度。這也代表著,在選擇嵌入式系統的基礎架構時,處理器本身只是應用的1個環節,如何能夠針對應用將所需的效能最大化,必須依照產品的不同而有各種考慮。

不只是意氣的技術之爭

真正的同質多核心架構-ARM11 MPCore

在嵌入式多核心應用處理器這方面的領域,目前以ARM為技術領導者,雖然該公司本身并無晶圓廠,而純粹以IP的形式出售處理器架構,由于定位正確,在短短的數年間取得了極大的市場地位,全世界絕大多數的手持式裝置都嵌入了ARM的處理器技術。

以其技術的發展歷程來看,早期的ARM7架構本身能夠滿足一些音效編譯碼應用。而在增加16位飽和運算指令和提高ARM9核心速度后,不僅能完成音效編譯碼工作,以及以大約80 MHz、15 畫格/秒速度下的MPEG-4 QCIF(4分之1 CIF分辨率)編碼。在ARM11 V6指令集架構上增加速度和SIMD指令后,就可以實現VGA分辨率的 H.264 編碼。再進一步到最新的Cortex A8與其基于64位SIMD架構的Neon加速器搭配工作之下,就可以完成 30 畫格/秒的 MPEG-4 VGA 編碼,所花周期只有 ARM11 的一半。在實際情況下,該工作需要大約 300 MHz。為了使這些選項對使用者更加可行,ARM 正在開發一個并行編譯器原型,它可以提取資料并行機制,并用 SIMD 硬件來使用它。

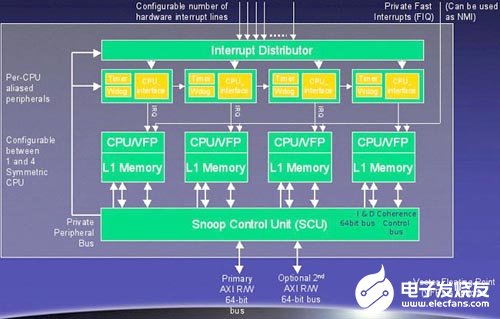

圖說:ARM11 MPCore的結構示意圖。

ARM11 MPCore乃是在ARM11核心的基礎組成,架構上屬于V6指令體系。根據不同應用的需要,MPCore可以被配置為1~4個處理器的組合方式,根據官方表示,其最高性能約可達到2600 Dhrystone MIPS的程度。MPCore是標準的同質多核心處理器,,組成MPCore的是4個基于ARM11架構的處理器核心,由于多核心設計的優點是在頻率不變的情況下讓處理器的性能獲得明顯提升,因此可望在多任務應用中擁有良好的表現,這一點很適合未來家庭消費電子的需要。例如,機上盒在錄制多個頻道電視節目的同時,還可通過因特網收看數字視訊點播節目、車內導航系統在提供導航功能的同時,仍然有余力可以向后座乘客播放各類視訊娛樂串流等。

在這類應用環境下,多核心結構的嵌入式處理器能夠表現出極強的性能優勢。根據原廠數據,MPCore多處理器可支持高達4路共享快取結構的對稱多處理器 (four-way cache coherent symmetric multiprocessing,SMP)、或者是4路不對稱多處理器(four-way asymmetric multiprocessing,AMP)以及4路兼有對稱/不對稱的混合式多處理器系統。其設計的高靈活設計在理論上可以滿足各種跨領域應用對運算性能的彈性需求,確保系統可獲得一流的響應能力或數據吞吐量。

不過ARM11 MPCore早在2004年就已經發布,2005年正式加入授權業務,截至目前為止,采用該處理器的產品集中于家電與汽車電子方面,但是數量并不算多,是業界對于處理器運算能量的需求尚未顯現?據了解,在汽車電子方面,汽車應用的微處理器要求越來越高,但是過去的單核心基本上還能滿足一般汽車的使用,而隨著越來越多的電子輔助裝置整合進汽車中,其間所需處理的工作也越來越繁雜,已經遠超過傳統汽車用微控制器所能負擔的程度,因此可預期的是,未來數年應該會有越來越多汽車廠商采用類似的多核心架構來取得合理的系統反應速度。

至于在家電應用方面,其實需要用到如此復雜核心的產品不多,在應用最多的影音產品方面,其實大部分的廠商都采用專用的硬件譯碼電路或者是DSP來進行編譯碼的動作,直接采用多核心處理器來進行編譯碼動作其實效益不明顯。而在行動應用方面,其實功耗依然是行動產品廠商所最注重的,即便ARM11 MPCore能夠達到極低的多核心同時工作功耗,但是依然無法與單核心版本相比,因此在行動應用上能見度不高。但是隨著Intel推行MID(Mobile Internet Device),類似的產品可望成為ARM11 MPCore架構的極大機會,因為即便是Stealey的下一代45nm產品Silverthorne,其功耗依然比MPCore高了5倍以上(加上芯片組的總功耗),且僅為單核心架構,在應用靈活度上明顯不如MPCore架構,不過有1點值得注意的是,Silverthorne挾帶了龐大的X86軟件資源,ARM等基于RISC體系處理器在這方面要明顯屈居于下風。

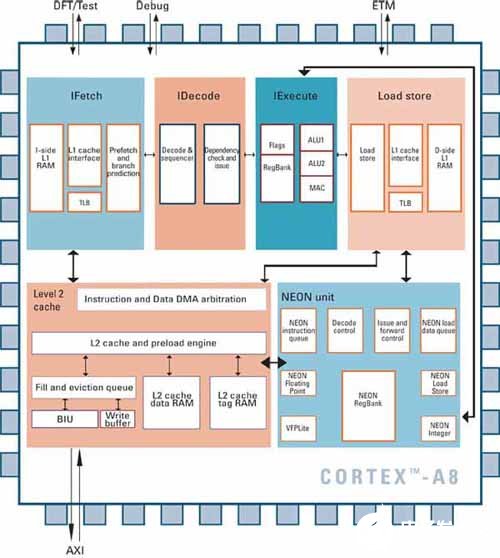

在RISC架構的類MID產品上,也可以考慮ARM最新的處理器架構,也就是Cortex-A8,該處理器基于最新的ARM v7體系,并且整合了1個64位DSP處理單元,對串流應用具備有極佳的加速能力,因此非常適用于類MID掌上型裝置的多媒體、甚至是游戲應用。嚴格上來,Cortex-A8也能算是多核心體系之一,但是其架構與MPCore之類的同質核心不同,而是采用1個通用處理器核心,并搭配個DSP核心而成的異質多核心處理器,相信這方面ARM向德州儀器公司借鑒了不少應用處理器的開發經驗。

圖說:Cortex-A8的結構示意圖。

事實上,NOKIA的N770/N800便已經具備了MID的所有功能,而且更為輕薄短小,但遺憾的是,搭配原廠的1500mAh充電電池,其持續使用時間僅能達到3.5個小時,與一般市面上的UMPC產品相去不遠,稍遜于Intel的MID產品,采用ARM體系處理器(N800采用基于ARM1136J(F)-S核心的i.MX31應用處理器)的省電優勢在此并沒有被凸顯出來,不過待機時間比之MID要略長。

堅持多執行緒路線的MIPS

或許可以視為意氣之爭,MIPS堅持與ARM實行不同的技術發展策略,ARM發展Multi Processor(MP,多處理器核心),而MIPS則往Multi Thread(MT,多執行緒)發展,就應用概念上來看,MP與MT技術兩者均致力于提高處理器的整體性能,兩者都可以減少任何應用當前軟件執行緒的處理時間。但這兩種技術采用了不同的硬件結構來減少處理時間,因此對于任意的特定軟件程序代碼來說,MP與MT對處理器性能的提升著程度上的不同。

但是會造成這樣的結果,其實2家IP廠商的研發概念上有很大的關連。由于MT技術著重于處理單元、內存控制器的有效利用,在最大程度上節省晶體管的使用,并且在此前提之下往上提升效能表現,這與MP架構中,系統效能需求有多少,就復制多少個核心塞進芯片中的浪費作法完全不同,MP可以取得較為全面的應用廣度,但是稍嫌鋪張浪費,相較之下,MT在成本與效能方面的平衡性表現要來得高明些。

許多人將MP與MT相提并論,而在某種程度上,這樣的比較其實并沒有太大意義,因為基本設計概念已經天差地遠,架構上的采用自然無法一概而論。在技術上,為了實現硬件多重處理,兩者對于軟件最佳化的復雜度方面其實都同樣比單核心架構要來得復雜許多,而為了要盡量避免處理單元與內存控制器在資源分配上的沖突,MT架構或許會來得更為復雜一些,但MP架構其實在某些程度上也會面臨同樣的問題(特別是共享高速緩存與內存控制器的多核心架構)。不論是在指令層級,或是執行緒層級的多任務,都與傳統單核心單執行緒的程序寫作方式與最佳化方法大異其趣。

一般的MT架構設計方面,單一處理器核心在運算的過程中,常會有內存存取速度跟不上處理器頻率增加的問題,進而導致高速緩存錯失(miss)時,形成執行管線長時間閑置的狀況,我們都了解,1個系統中的儲存單元,最快速的要屬處理器中的緩存器,其次是L1高速緩存、L2快取記體,最后則是主存儲器,其速度的差別可達數千倍以上,處理器要取得指令或數據時,必先從高速緩存中提取,儲存于緩存器中進行運算,最終結果再回存到高速緩存,并在空閑時填回主存儲器,當處理器向高速緩存發出存取需求,卻發現所需要的數據不在高速緩存中,這是就必須花費大筆的時間前往主存儲器尋找并讀取,這其間所浪費的時間可能會高達數十個頻率周期,處理管線在等待數據填補的時間,就形成了閑置狀態。

如果利用多執行緒處理概念,適時的將其它執行緒拉過來填補已經造成的閑置狀態,其速度的增長甚至可以達到非常明顯的地步,雖不至于倍增,但是由20%到40%都有可能。而要達成這樣的目的,在晶體管數目方面只需增加約15%的程度即可,若以一般同樣架構的單核心處理器在變更為雙核心的效能增長程度約為40%到70%左右的程度,而晶體管數目幾乎要倍增的情況,就可看出MIPS的MT技術的效率有多高了。但是MT技術有個嚴重的缺陷,那就是多執行緒工作處理過程中,過于頻繁的上下文切換(context switch)將有可能會造成極大的效能耗損。

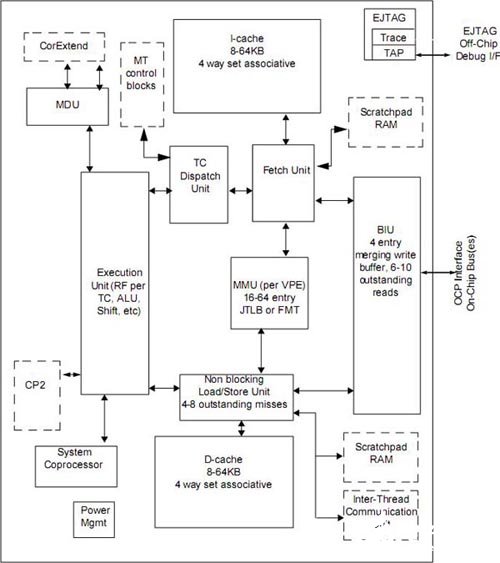

圖說:MIPS 74K處理器結構示意圖。

MIPS公司有大產品線,分別是單執行緒的24K與74K系列,以及多執行緒的34K系列。74K甫于今年六月發表,在65nm制程下,其運作頻率已經超越1GHz,采用通用處理器搭配DSP核心的設計,不過總體效能與功耗表現略遜于類似架構的ARM Cortex-A8。多執行緒處理器的主角—34K系列,該處理器核心能設定1或2個虛擬處理組件(VPE)以及最多5個執行緒內容(TC),提供充分的可配置彈性。但是講白了,其實兩個VPE的作法就是將單顆核心模擬為2個核心,使34K核心能同時執行兩個獨立的操作系統,或是一個雙路的對稱式多重處理器操作系統。

MIPS32 34Kc核心采用90nm制程,最差操作狀態下頻率為500MHz。核心尺寸為2.1mm2,而核心部分耗電量為0.56mW/MHz@1.0V。目前該 系列核心共包含34Kc、34Kf、34Kc Pro以及34Kf Pro。這些核心具備完全兼容于IEEE 754規格的硬件浮點運算處理器。其中34Kc Pro與34Kf Pro核心具備CorExtend功能,能讓SoC研發業者自行擴增指令。

圖說:MIPS 34K處理器結構示意圖。

根據MIPS自家的估算,與同家族的24K系列產品相較起來,34K在2個VPE以及2個TC的組態設定之下,可以將效能提升到超越24K處理器60%的程度,芯片面積大略增加14%,而因為多執行緒作業所導致的高速緩存失誤比率則是由4.41%增加到5.16%,算是在可接受的范圍之內。不過與單核心74K相較起來,34K反而更不適用于網絡或多媒體串流的密集計算環境,而VPE和TC單元的增加,同樣也會加大芯片的面積。雖說MT技術的局限性,使其不適合用于多媒體編譯碼應用上,但是在汽車電子方面,已經有廠商成功利用2顆34K處理器組成雙核多執行緒處理器,并提供的相當優秀的執行效能,有此成功的前例可循,我們也可以預測,未來MIPS將會有更多結合多核與多執行緒的解決方案出現,不過這么一來,在成本調配方面的優勢還能剩下多少,就由方案提供廠商去傷腦筋吧。

責任編輯:gt

-

處理器

+關注

關注

68文章

19404瀏覽量

231034 -

嵌入式

+關注

關注

5092文章

19176瀏覽量

307407 -

汽車電子

+關注

關注

3028文章

8021瀏覽量

167708

發布評論請先 登錄

相關推薦

嵌入式多核處理器硬件結構分析與對排序算法進行并行化優化

“網絡物理系統(CPS) - 面向安全關鍵應用的未來異構多核E / E架構”

熟知ARM如何構架,了解嵌入式系統基本核心

多核嵌入式系統存在的局限性?怎么解決這些問題?

對嵌入式系統中的架構設計的理解

嵌入式實時系統多核負載均衡調度架構的相關資料推薦

LabVIEW 禁止其他可多核心處理的應用程序在所有核心上執行

嵌入式軟件行業針對異構多核芯片開發出首個全面解決方案及產品附加信息

基于嵌入式環境的WiFi通信設計方案詳解

多核心架構和多執行緒在嵌入式網絡環境中的應用方案分析

多核心架構和多執行緒在嵌入式網絡環境中的應用方案分析

評論