雖然芯片制造商正在推進(jìn)技術(shù)的發(fā)展,但是在前道工序(front-end-of-line :FEOL)中微縮晶體管,以及在中間工序(Middle-of-line:MOL)和后道工序(back-end-of-line:BEOL)中改進(jìn)觸點(diǎn)和連線(xiàn)則變得越來(lái)越困難。

在本文中,imec的 CMOS器件技術(shù)總監(jiān)Naoto Horiuchi和納米互連項(xiàng)目總監(jiān)Zsolt Tokei匯集了他們的專(zhuān)業(yè)知識(shí),提出了一份技術(shù)路線(xiàn)圖。沿著微縮路線(xiàn),他們?cè)贔EOL中引入了新的器件結(jié)構(gòu),在MOL和BEOL中引入了新的材料和集成方案。他們討論了各種方案背后的現(xiàn)狀、挑戰(zhàn)和原理——這些方案為芯片行業(yè)提供了一條通往1nm技術(shù)代際的可能之路。

FEOL、BEOL和MOL——邏輯芯片的關(guān)鍵部分

前沿邏輯芯片的制造可以細(xì)分為三個(gè)獨(dú)立的部分:前道工序(FEOL)、中間工序(MOL)和后道工序(BEOL)。

FEOL涵蓋了芯片有源部分的加工,即位于芯片底部的晶體管。晶體管作為電氣開(kāi)關(guān),使用三個(gè)電極進(jìn)行操作:柵極、源極和漏極。源極和漏極之間的導(dǎo)電通道中的電流可以被“開(kāi)”和“關(guān)”,這一操作由柵極電壓控制。

BEOL是加工的最后階段,指的是位于芯片頂部的互連。互連是復(fù)雜的布線(xiàn)方案,它分配時(shí)鐘和其他信號(hào),提供電源和地,并將電信號(hào)從一個(gè)晶體管傳輸?shù)搅硪粋€(gè)晶體管。BEOL由不同的金屬層、局部(Mx)、中間線(xiàn)、半全局線(xiàn)和全局線(xiàn)組成。總層數(shù)可以多達(dá)15層,而Mx層的典型數(shù)量在3~6層之間。這些層中的每層都包含(單向)金屬線(xiàn)(組織在規(guī)則的軌道中)和介電材料。它們通過(guò)填充有金屬的通孔結(jié)構(gòu)垂直互連。

FEOL和BEOL由MOL聯(lián)系在一起。MOL通常由微小的金屬結(jié)構(gòu)組成,作為晶體管的源極、漏極和柵極的觸點(diǎn)。這些結(jié)構(gòu)連接到BEOL的局部互連層。雖然單元尺寸在微縮,但要連接到的引腳數(shù)量大致不變,意味著接觸它們的難度更大。

隨著器件規(guī)模不斷縮小到3nm及以下,這些模塊的加工都伴隨著許多挑戰(zhàn),這迫使芯片制造商在FEOL中采用新的器件架構(gòu),以及在BEOL和MOL中采用新的材料和集成方案。

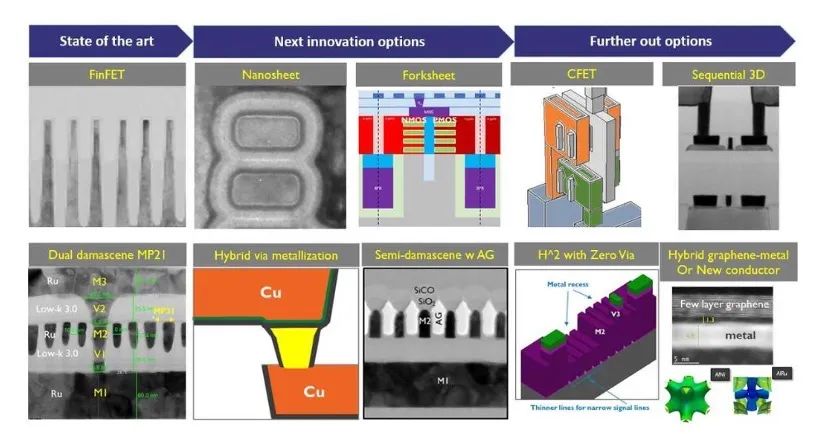

在本文中,我們介紹了imec對(duì)擴(kuò)展路線(xiàn)圖的看法,并深入探討了各種方案。從最先進(jìn)的主流FEOL、BEOL和MOL技術(shù)開(kāi)始,我們逐步引入新的FEOL器件架構(gòu)(例如,環(huán)繞閘極(GAA) nanosheet、 forksheet,以及互補(bǔ)場(chǎng)效應(yīng)晶體管 (CFET) 器件)。這些架構(gòu)將立即影響局部互連層,要求采用新型BEOL材料(如釕(Ru)、鉬(Mo)和金屬合金)和新的集成方案(即混合金屬化(hybrid metallization)、半鑲嵌(semi-damascene)和具有零通孔結(jié)構(gòu)的混合高度)。

在這一激動(dòng)人心的旅程中,我們還引入了有助于提高M(jìn)OL連通性的結(jié)構(gòu)微縮助推器(如自對(duì)準(zhǔn)柵極觸點(diǎn)(SAGC)和埋入式電源線(xiàn)(BPR))。這些助推器還將有助于減少標(biāo)準(zhǔn)單元級(jí)的面積,允許減少局部互連級(jí)的金屬track數(shù)量,這稱(chēng)為軌道高度微縮。

imec對(duì)CMOS技術(shù)微縮路線(xiàn)圖的觀(guān)點(diǎn)

最先進(jìn)的主流技術(shù)及其微縮瓶頸

(1)FEOL中的FinFET

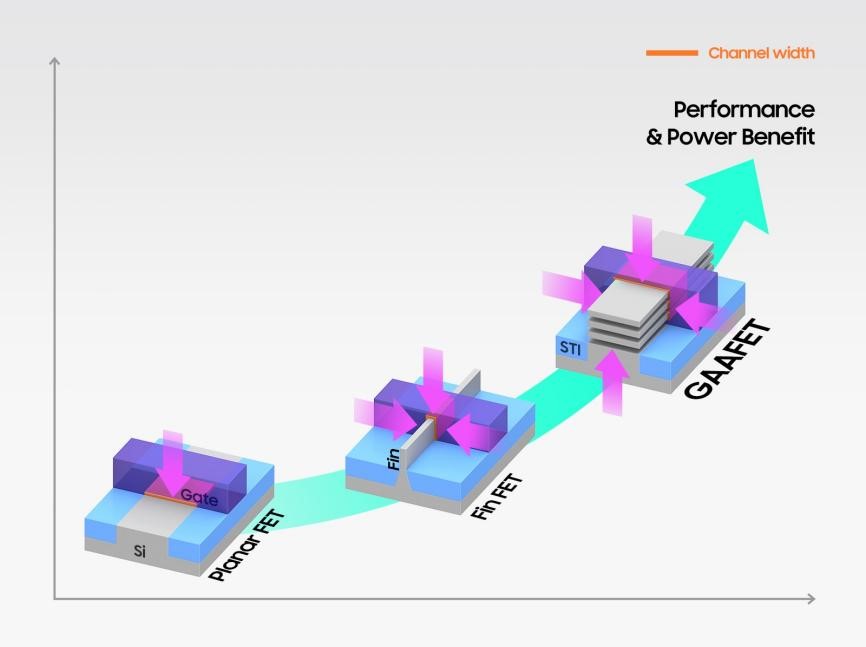

根據(jù)摩爾定律,晶體管尺寸每?jī)赡昕s小0.7倍。為了保持這種微縮路徑,業(yè)界在幾年前就從 “老式”的平面MOSFET轉(zhuǎn)向了FinFET晶體管架構(gòu)。在FinFET中,源極和漏極之間的溝道呈鰭片狀,柵極環(huán)繞這個(gè)3D通道,從溝道的3個(gè)側(cè)面提供控制。這種多柵極結(jié)構(gòu)可以消除短溝道效應(yīng),短溝道效應(yīng)在柵極長(zhǎng)度減小時(shí)開(kāi)始降低晶體管的性能。

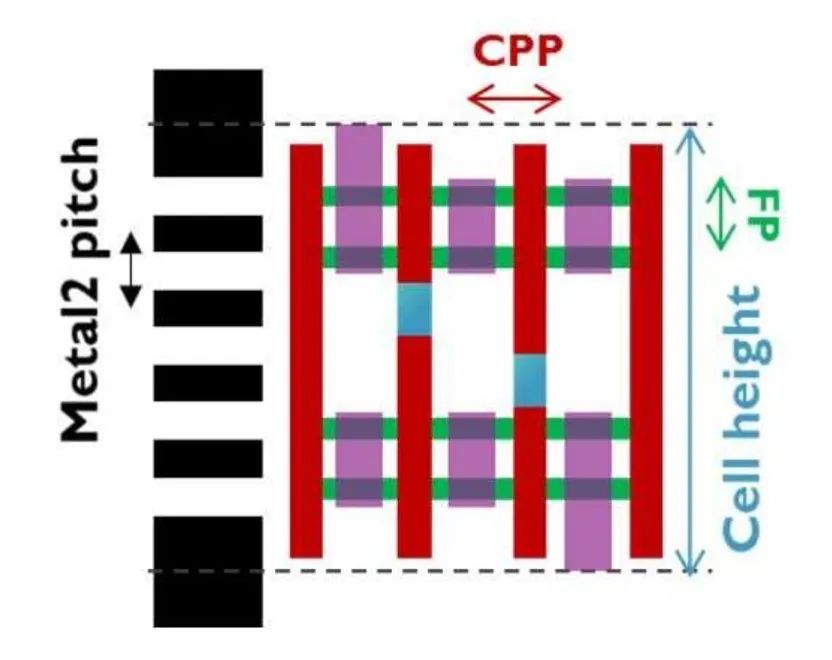

2012年,第一款商用22nm FinFET問(wèn)世。從那時(shí)起,為了提高性能和減小面積,人們對(duì)架構(gòu)進(jìn)行了改進(jìn)。例如,鰭片高度增加,以在相同的面積上獲得更高的器件驅(qū)動(dòng)電流。如今,工業(yè)界已經(jīng)有7nm芯片投入生產(chǎn),其“內(nèi)部”有FinFET。在最先進(jìn)節(jié)點(diǎn)的單元層面,track高度為6T的標(biāo)準(zhǔn)單元每個(gè)器件具有2個(gè)鰭片,接觸間距小至57nm。6T的意思是在單元高度范圍內(nèi)可以容納6條金屬線(xiàn)。

具有2個(gè)鰭片的6T標(biāo)準(zhǔn)單元設(shè)計(jì)(CPP=觸點(diǎn)多晶硅間距;FP=鰭片間距;黑色=金屬-2布線(xiàn)track;紅色=柵極;藍(lán)色=柵極觸點(diǎn);綠色=有源部件(即鰭片);紫色=有源觸點(diǎn))。

(2)BEOL中的銅基和鈷基雙鑲嵌(dual-damascene)

為了跟上前道工序的面積微縮,BEOL尺寸以更快的速度減小,導(dǎo)致金屬間距越來(lái)越小,導(dǎo)線(xiàn)的橫截面積也越來(lái)越小。如今,大多數(shù)關(guān)鍵的本地互連(如M1和M2)的金屬間距都只有40nm。銅基雙鑲嵌(dual damascene)是制造互連的主要工藝流程。

雙鑲嵌始于在結(jié)構(gòu)上沉積低k介電材料。這些低k薄膜旨在降低芯片的電容和延遲。在接下來(lái)的步驟中,會(huì)形成孔隙和溝槽。最近,所有領(lǐng)先的邏輯制造商都宣布在他們的技術(shù)中使用EUV光刻技術(shù),以便在狹窄的間距下保持成本效益。

在圖案化后,人們添加金屬阻擋層,以防止銅原子遷移到低k材料中。通過(guò)內(nèi)襯和銅種子對(duì)阻擋層進(jìn)行涂層后,對(duì)結(jié)構(gòu)進(jìn)行銅電鍍,然后采用化學(xué)機(jī)械拋光(CMP)步驟來(lái)完成雙鑲嵌模塊。

布線(xiàn)擁塞和顯著的RC延遲(由于增加的電阻電容(RC)產(chǎn)品)已成為進(jìn)一步擴(kuò)大互連規(guī)模的重要瓶頸,推動(dòng)了在BEOL中引入新材料和集成方案的需求。最近,業(yè)界已將Co用作局部的替代金屬,并且一些公司在中間層使用氣隙作為替代的低k介電材料。

(3)減小接觸電阻,提高M(jìn)OL的連接性

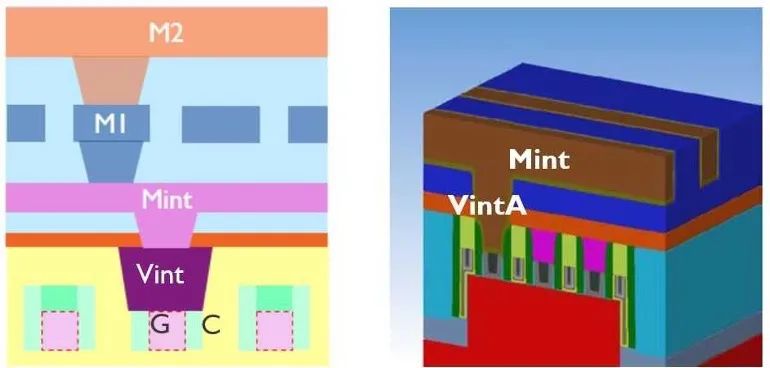

FEOL和BEOL之間的連接由MOL提供。在很長(zhǎng)一段時(shí)間內(nèi),MOL被組織成單層接觸,但現(xiàn)在它擴(kuò)展到幾個(gè)層,包括例如Mint和Vint層。這些層將電信號(hào)從晶體管的源極、漏極和柵極傳送到本地互連,反之亦然。

在晶體管方面,源極/漏極接觸電阻已成為芯片行業(yè)的重要問(wèn)題。隨著晶體管尺寸的縮小,可用于制造觸點(diǎn)的面積相應(yīng)地減小了。由于源極/漏極接觸電阻與接觸面積成正比,這就導(dǎo)致了源極/漏極接觸電阻的急劇增加。多年來(lái),imec開(kāi)發(fā)了改進(jìn)的源/漏接觸方案,以減小寄生電阻,這主要是通過(guò)提高半導(dǎo)體側(cè)的摻雜水平,以及優(yōu)化金屬(通常是過(guò)渡金屬硅化物)和半導(dǎo)體之間的界面質(zhì)量來(lái)實(shí)現(xiàn)。

為了進(jìn)一步提高M(jìn)OL的連通性,我們引入了結(jié)構(gòu)微縮助推器(structural scaling boosters)。其中一個(gè)例子是自對(duì)準(zhǔn)柵極觸點(diǎn)(self-aligned gate contact),它允許將柵極觸點(diǎn)直接放置在有源器件的頂部。這使得柵極接入更加靈活,并減少了整體接觸面積。業(yè)界在當(dāng)今的芯片設(shè)計(jì)中采用了這種技術(shù),以進(jìn)一步提高布線(xiàn)能力。

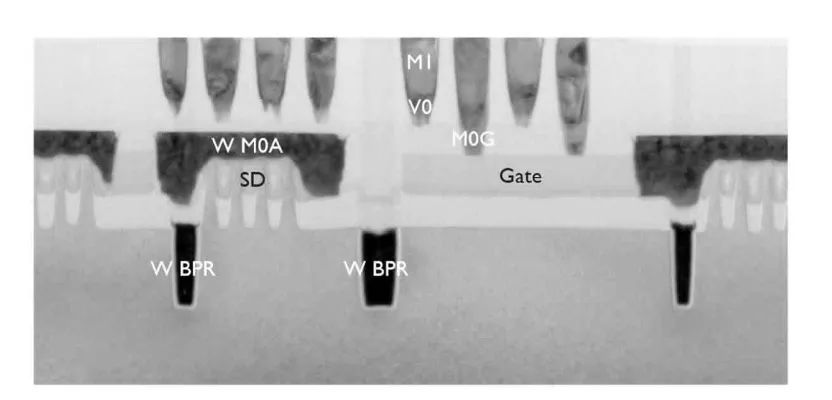

(左)MOL堆棧;(右)自對(duì)準(zhǔn)柵極觸點(diǎn)。

FEOL、BEOL和MOL的下一個(gè)創(chuàng)新選擇

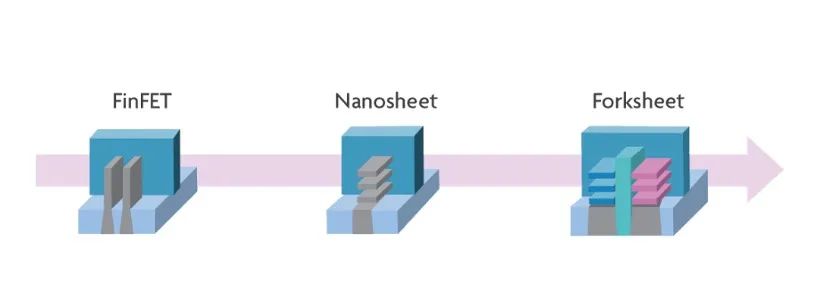

(1)FEOL:垂直堆疊的nanosheet器件,以及后續(xù)的forksheet

隨著微縮到5 nm以下,預(yù)計(jì)FinFET將走到盡頭。在減小柵極長(zhǎng)度的情況下,該器件不能提供足夠的溝道靜電控制。除此之外,向更低(5T)track高度標(biāo)準(zhǔn)單元的演進(jìn)需要向單鰭片器件過(guò)渡,即使鰭片高度進(jìn)一步增加,單鰭片器件也不能提供足夠的驅(qū)動(dòng)電流。

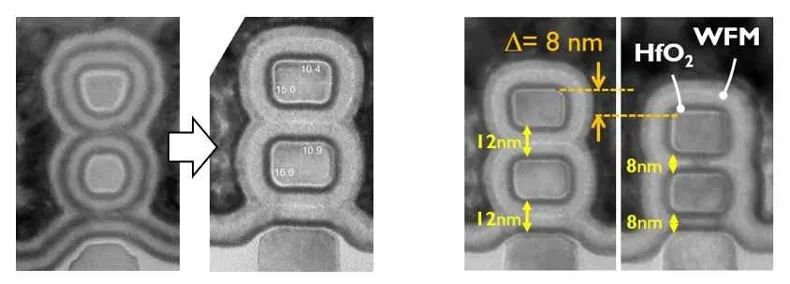

在這里,垂直堆疊的環(huán)繞閘極(GAA) nanosheet 晶體管進(jìn)入了人們的視野。它們可以被認(rèn)為是FinFET器件的自然演變。想象一下,將一個(gè)FinFET側(cè)放,并將其分成獨(dú)立的水平sheet,這些sheet構(gòu)成了溝道。由于現(xiàn)在柵極完全包裹在溝道周?chē)蜏系乐g,因此與FinFET相比,可以獲得更優(yōu)的通道控制。同時(shí),溝道截面在3D體積中的更優(yōu)化分布,優(yōu)化了單位面積的有效驅(qū)動(dòng)力。

Imec自2015年以來(lái)一直致力于這種架構(gòu)的研究,從而優(yōu)化了最關(guān)鍵的工藝步驟。制造垂直堆疊的GAA nanosheet晶體管的工藝流程首先是外延沉積多個(gè)Si/SiGe層,并形成和填充淺溝隔離(STI)模塊。在后面的步驟中,SiGe層被選擇性地去除,釋放出Si nanosheet 結(jié)構(gòu)。在這些Si nanosheet 層的周?chē)椭虚g,以雙重功能置換金屬柵極(RMG)流形成柵極疊層。

除了實(shí)現(xiàn)優(yōu)化的工藝步驟,imec團(tuán)隊(duì)還開(kāi)發(fā)了將垂直nanosheet間距降至10nm以下的工藝。這樣一來(lái),寄生電容就可以大幅降低。如今,一些芯片制造商正準(zhǔn)備向這些器件發(fā)展,以生產(chǎn)其下一代芯片。

垂直堆疊的GAA nanosheet晶體管的優(yōu)化:(左)nanosheet形狀控制;(右)nanosheet垂直空間還原分離。

為了將nanosheet器件的可微縮性延伸到2nm節(jié)點(diǎn)及以下,imec最近提出了一種替代架構(gòu),稱(chēng)為forksheet器件。在這種架構(gòu)中,sheet由叉形柵極結(jié)構(gòu)控制,在柵極圖案化之前,通過(guò)在pMOS和nMOS器件之間引入介電層來(lái)實(shí)現(xiàn)。這個(gè)介電層從物理上隔離了p柵溝槽和n柵溝槽,使得n-to-p間距比FinFET或nanosheet器件更緊密。根據(jù)仿真結(jié)果,imec預(yù)計(jì)這種forksheet具有卓越的面積和性能微縮性(允許trace高度從5T縮減到4.3T),以及更低的寄生電容。在SRAM設(shè)計(jì)中實(shí)現(xiàn)時(shí),有望減少單元面積。

從FinFET到nanosheet,再到forksheet。

(2)BEOL:混合金屬化(hybrid metallization)和半鑲嵌(semi-damascene)

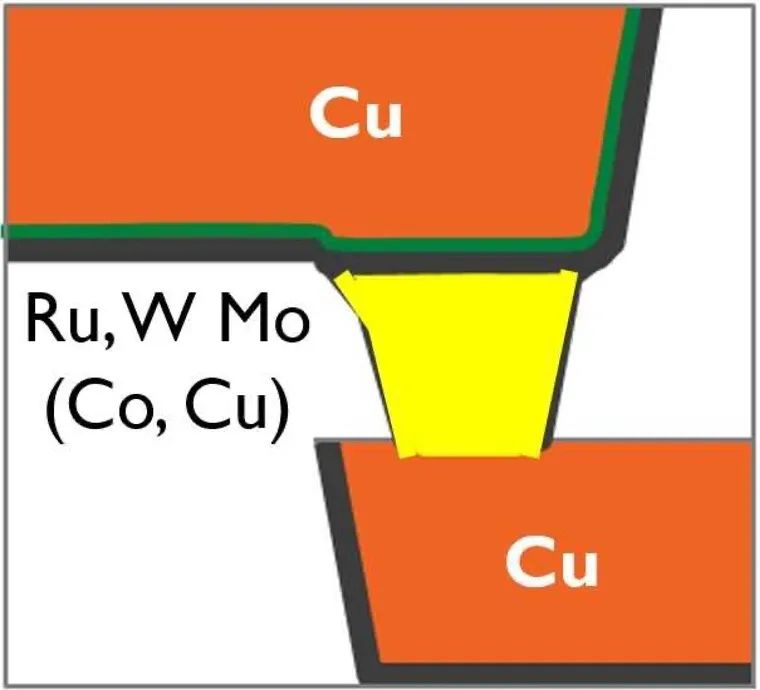

為了與FEOL中實(shí)現(xiàn)的面積減小保持同步,最關(guān)鍵的局部互連層(M1和M2)的金屬間距最終將變得緊湊至21nm。現(xiàn)在,這些層之間的通孔的臨界尺寸小至12~14nm。在傳統(tǒng)的銅雙鑲嵌集成方案中,在實(shí)際的銅金屬化之前,在溝槽和通孔結(jié)構(gòu)內(nèi)沉積了阻擋層和襯墊層。但在這些狹小的尺寸下,襯墊/阻擋層占據(jù)了太多的空間,留給銅填充的空間很小。這會(huì)對(duì)通孔電阻和可變性產(chǎn)生負(fù)面影響,現(xiàn)在通孔電阻和可變性已經(jīng)成為一種限制因素。此外,由于高電流密度的要求,電遷移可靠性受到挑戰(zhàn)。

克服這一挑戰(zhàn)的一種選擇是混合金屬化,其中替代的通孔金屬(如釕、鎢或鉬)以無(wú)障礙的方式連接到銅線(xiàn)的底部。這種結(jié)構(gòu)允許更薄(2納米)的銅線(xiàn)阻擋層,同時(shí)保持電遷移可靠性,同時(shí)降低通孔的電阻。雖然從電阻的角度來(lái)看,這樣的方案很有吸引力,但關(guān)鍵是它也是可靠的,這是人們?yōu)閷で蠼鉀Q方案而積極研究的領(lǐng)域。

混合金屬化結(jié)構(gòu)的示意圖

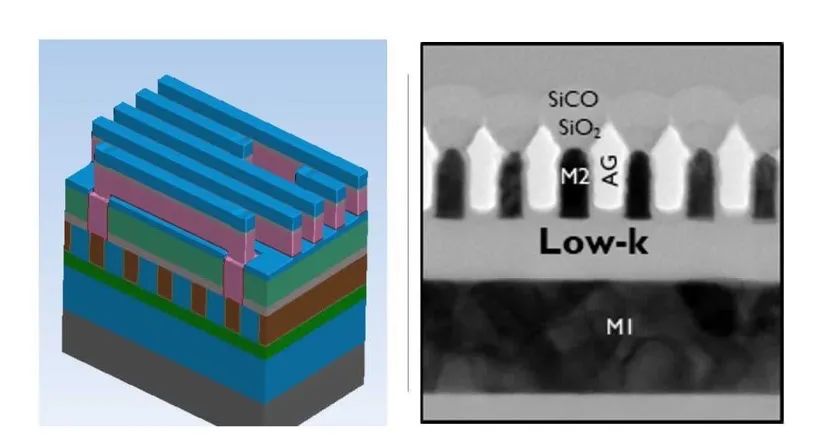

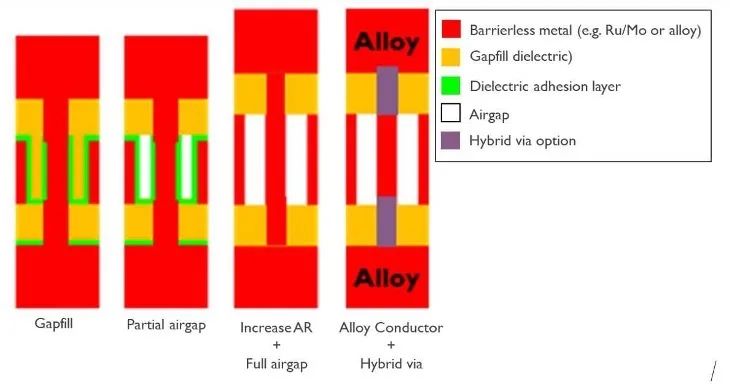

對(duì)于低于21nm的金屬間距,imec提出半鑲嵌作為一個(gè)有趣的選擇。半鑲嵌的關(guān)鍵是它允許互連高度增加,同時(shí)保持電容的可控性,因此總體上有望獲得RC效益。

半鑲嵌模塊:示意圖和SEM圖片

從工藝技術(shù)的角度來(lái)看,它使用可圖案化的替代金屬,最終形成氣隙。雙鑲嵌和半鑲嵌的本質(zhì)區(qū)別是省略了金屬的化學(xué)機(jī)械拋光(CMP)步驟,這是雙鑲嵌工藝流程的最后一步。在半鑲嵌工藝中,通孔以單鑲嵌方式形成圖案,然后用金屬填充和過(guò)填充,這意味著金屬沉積繼續(xù)進(jìn)行,直到在電介質(zhì)上形成一層金屬(即,無(wú)勢(shì)壘金屬,如釕或鉬)。然后對(duì)金屬進(jìn)行掩蔽和蝕刻,以形成金屬線(xiàn)。通過(guò)這種方式,與雙鑲嵌工藝相反,可以形成具有較高縱橫比的線(xiàn)路——因此,電阻較小。在金屬圖案化之后,線(xiàn)條之間的空隙可以由電介質(zhì)填充,也可以用來(lái)在局部層形成部分氣隙。

對(duì)于第二代產(chǎn)品,可以預(yù)見(jiàn)到完全的氣隙,在更晚的階段,可采用有序金屬合金作為導(dǎo)體。這種順序?qū)е乱淮右淮闹鸩礁纳啤庀兜氖褂孟拗屏穗娙莸脑黾樱娙莸脑黾邮怯蓪?shí)現(xiàn)更高縱橫比的線(xiàn)引起的。這種針對(duì)最關(guān)鍵的金屬層M1和M2所設(shè)想的半鑲嵌集成方案,可以與上述較不關(guān)鍵的互連層的傳統(tǒng)雙鑲嵌或混合金屬化方案相結(jié)合。

半鑲嵌的技術(shù)選擇

(3)MOL:連接性革命,有微縮助推器的支持

在MOL中,我們已經(jīng)看到了結(jié)構(gòu)微縮助推器的引入,以提高可布線(xiàn)性。這種連通性的發(fā)展將繼續(xù)下去,允許MOL層的其他實(shí)現(xiàn),這取決于器件和互連之間的連接需求。例如,forksheet器件架構(gòu)允許更靈活的柵極連接和柵極切割,從而提高布線(xiàn)靈活性。

另一個(gè)新興的助推器是埋入式電源線(xiàn)(buried power rail:BPR)。電源線(xiàn)是供電網(wǎng)絡(luò)的一部分,傳統(tǒng)上在芯片的BEOL層(即Mint層和M1層)實(shí)現(xiàn)。相反,BPR被埋在芯片的FEOL中,以幫助釋放互連的布線(xiàn)資源。這一具有挑戰(zhàn)性的構(gòu)造直接影響了FEOL和BEOL的制造。

在VLSI 2020上,imec在FinFET CMOS測(cè)試工具中提出了鎢(W)埋地電源線(xiàn)(BPR)集成方案,該方案對(duì)CMOS特性沒(méi)有產(chǎn)生不利影響。補(bǔ)充評(píng)估研究也顯示了在邏輯和SRAM設(shè)計(jì)中實(shí)現(xiàn)BPR作為微縮助推器在系統(tǒng)級(jí)的優(yōu)勢(shì)。

這種集成方案可以擴(kuò)展到所謂的VBPR,在VBPR中,到BPR的通孔現(xiàn)在與MOL層(M0A線(xiàn))相連。在VLSI 2020上,imec團(tuán)隊(duì)展示了一種鎢基BPR,該BPR與Ru過(guò)孔(VBPR)相連,以與Ru M0A線(xiàn)接觸。這種結(jié)構(gòu)獲得了優(yōu)異的電阻和電遷移效果。

透射電子顯微鏡(TEM)顯示了集成有Si FinFET的W-BPR線(xiàn)。

此外,我們還需要?jiǎng)?chuàng)新來(lái)進(jìn)一步降低源極/漏極的接觸電阻。Imec已經(jīng)提出了改進(jìn)的接觸方案,包括環(huán)繞接觸(通過(guò)金屬的原子層沉積實(shí)現(xiàn))作為金剛石外延接觸的替代物。這再次擴(kuò)大了接觸面積,因此降低了接觸電阻。

進(jìn)一步的選擇:繼續(xù)向1nm節(jié)點(diǎn)邁進(jìn)

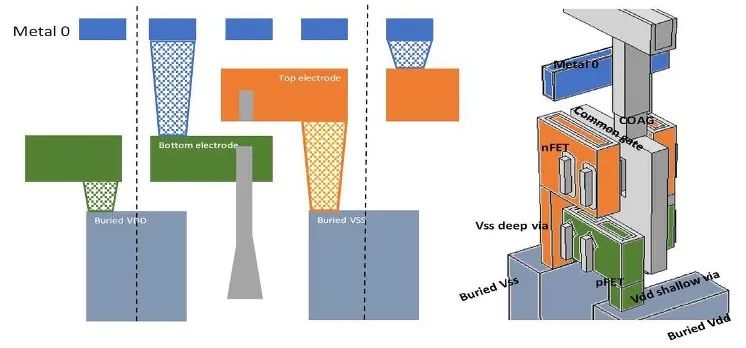

(1)FEOL中的CFET:走向3T邏輯標(biāo)準(zhǔn)單元之路

超過(guò)5T后,單元高度的進(jìn)一步降低現(xiàn)在主要受到可布線(xiàn)性問(wèn)題的限制,這應(yīng)該在邏輯塊層面進(jìn)行評(píng)估。優(yōu)化可布線(xiàn)性將我們帶到了CFET,它將摩爾定律的視界推得更遠(yuǎn)。CFET的概念在于將nFET“折疊”在pFET之上(fin-on-fin或sheet-on-sheet),從而充分利用了器件3D微縮的可能性。這種架構(gòu)最強(qiáng)的優(yōu)勢(shì)是面積擴(kuò)展,最終可以實(shí)現(xiàn)3T邏輯標(biāo)準(zhǔn)單元和SRAM單元,而布局面積卻大大縮小。

CFET架構(gòu)

在VLSI 2020上,imec展示了CFET器件的第一個(gè)實(shí)驗(yàn)概念證明,它是在單片工藝流程中制造的。該團(tuán)隊(duì)設(shè)法克服了這一復(fù)雜工藝方案的關(guān)鍵工藝挑戰(zhàn),即從大塊襯底開(kāi)始,從下到上地加工CFET。如今,人們正在探索采用順序CFET作為一種替代的、不太復(fù)雜的集成流程。在順序式CFET中,對(duì)底層器件(如pFET)進(jìn)行加工后,再進(jìn)行晶圓鍵合,形成頂層器件(如nFET)溝道,然后對(duì)頂層器件進(jìn)行進(jìn)一步加工。順序CFET為頂層器件中使用的溝道材料提供了更靈活的選擇。

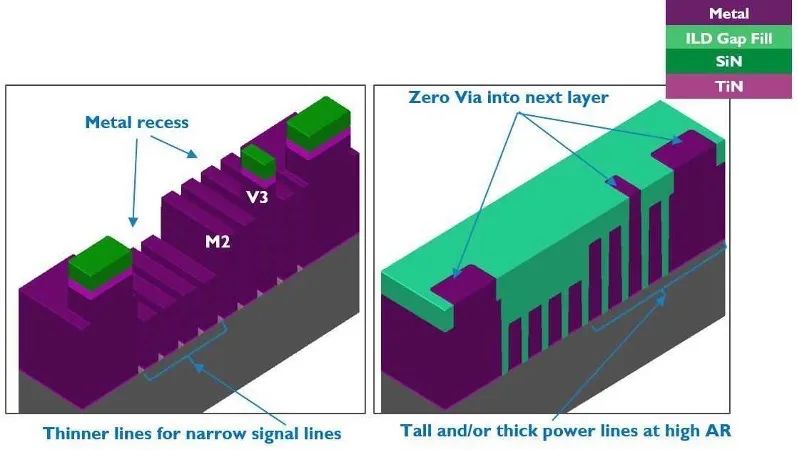

(2)BEOL:“零通孔的混合高度”,以及尋找替代導(dǎo)體

金屬線(xiàn)和通孔的電阻和電容仍然是BEOL最關(guān)鍵的參數(shù)。解決這個(gè)問(wèn)題的一種方法是另一種金屬化結(jié)構(gòu),稱(chēng)為“零通孔混合高度”。這種方案可以根據(jù)金屬線(xiàn)的應(yīng)用需求,靈活地將電阻換成電容。

這個(gè)想法是將每個(gè)金屬層分成三個(gè)獨(dú)立的子層:一條中心線(xiàn),以及可能在其上方或下方的延伸。對(duì)于每個(gè)金屬層,我們現(xiàn)在得出四種可能的情況(僅中心線(xiàn);中心線(xiàn)+向下延伸;中心線(xiàn)+向上延伸;中心線(xiàn)+向上和向下延伸)。這允許我們?cè)谙嗤母采w區(qū)內(nèi)調(diào)整金屬線(xiàn)的高度和縱橫比。

例如,如果該線(xiàn)需要用作對(duì)電阻非常敏感的電源線(xiàn),則可以形成具有高縱橫比(因此電阻小)的線(xiàn)。如果線(xiàn)路需要傳送信號(hào),則僅使用中心線(xiàn)來(lái)保持較小的電容。這種結(jié)構(gòu)不僅可以靈活地將電阻換成電容,而且有望提高整體能量和速度。

從制程角度看,不同的高度是通過(guò)金屬凹槽刻蝕步驟來(lái)實(shí)現(xiàn)的。通過(guò)一直凹到末端,該線(xiàn)可以用作垂直通孔連接,從而省略了對(duì)經(jīng)典通孔結(jié)構(gòu)的需要。Imec正在解決處理這種“零通孔混合高度”結(jié)構(gòu)帶來(lái)的各種挑戰(zhàn)。

概念圖:零通孔混合高度,應(yīng)用于金屬2層

此外,將標(biāo)準(zhǔn)單元面積減小至3至4 track將要求導(dǎo)體具有極小的電阻。Imec探索了多種新型導(dǎo)體材料,這些材料有望獲得比釕和鉬更好的品質(zhì)因數(shù)。該品質(zhì)因數(shù)定義為體積電阻率乘以金屬中載流子的平均自由程的乘積。令人感興趣的是非常小的尺寸下具有低電阻率的有序二元金屬間化合物。

例如Ru和Al基化合物,例如AlNi或RuV 3,雖然這不是唯一的候選物。自始至終的計(jì)算已經(jīng)顯示出各種金屬在未來(lái)互連應(yīng)用中的良好特性。尋找下一種新的導(dǎo)體并不容易,但令人鼓舞的是,世界各地的一些研發(fā)小組已經(jīng)接受了這一想法,并正在尋找候選物。

從長(zhǎng)遠(yuǎn)來(lái)看,石墨烯/金屬混合導(dǎo)體也是一個(gè)有趣的選擇。眾所周知,石墨烯非常薄,具有很高的導(dǎo)電性和導(dǎo)熱性。然而,這種材料沒(méi)有足夠的電荷載流子來(lái)用作局部互連。但是,有辦法調(diào)節(jié)電導(dǎo)率。一種方法是使用混合金屬/石墨烯方案,其中金屬(例如,銅、釕、鉬等。)被石墨烯包裹。Imec早些時(shí)候展示了這種混合金屬/石墨烯方案的低電阻率和高熱穩(wěn)定性。

(3)MOL

為了進(jìn)一步緩解布線(xiàn)擁擠并滿(mǎn)足新提出的晶體管結(jié)構(gòu)的要求,MOL層需要進(jìn)一步創(chuàng)新。例如,在CFET中,需要為接觸柵極提供新的解決方案,現(xiàn)在,這對(duì)于nFET和pFET器件來(lái)說(shuō)是通用的。此外,高縱橫比的通孔將把各種構(gòu)件互連起來(lái),這些構(gòu)件現(xiàn)在已經(jīng)擴(kuò)展到三維。但是,這些深通孔的主要寄生電阻需要降低。這可以通過(guò)引入先進(jìn)的MOL觸點(diǎn)來(lái)實(shí)現(xiàn),例如使用釕。

總結(jié)

隨著微縮到5nm以下,芯片制造商可能會(huì)逐漸遠(yuǎn)離主流技術(shù),例如FinFET(在FEOL中),Cu雙金屬鑲嵌(在BEOL中)和傳統(tǒng)的觸點(diǎn)方案(在MOL中)。我們介紹了FEOL、BEOL和MOL的下一步創(chuàng)新方案,提供了通往1nm技術(shù)節(jié)點(diǎn)的可能途徑。

責(zé)任編輯:YYX

-

芯片

+關(guān)注

關(guān)注

456文章

51024瀏覽量

425427 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1740瀏覽量

131633 -

1nm

+關(guān)注

關(guān)注

0文章

15瀏覽量

3916

原文標(biāo)題:關(guān)注 | 1nm將如何實(shí)現(xiàn)?

文章出處:【微信號(hào):wc_ysj,微信公眾號(hào):旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

臺(tái)積電1nm進(jìn)展曝光!預(yù)計(jì)投資超萬(wàn)億新臺(tái)幣,真有必要嗎?

2024 Arm Tech Symposia圓滿(mǎn)落幕,思爾芯創(chuàng)新方案備受矚目

面向未來(lái)的智能視覺(jué)參考設(shè)計(jì)與汽車(chē)架構(gòu),思爾芯提供基于A(yíng)rm技術(shù)的創(chuàng)新方案

面向汽車(chē)T-BOX與域控制器的HIL測(cè)試新方案

智芯公司雙模分鐘級(jí)數(shù)據(jù)采集創(chuàng)新方案取得顯著成果

中興通訊展示創(chuàng)新方案與實(shí)踐成果

河南移動(dòng)與中興通訊聯(lián)合發(fā)布5G-A×AI六大創(chuàng)新方案

中國(guó)移動(dòng)智能水表創(chuàng)新方案正式發(fā)布

鼎陽(yáng)科技展示嵌入式測(cè)量技術(shù)創(chuàng)新方案

兆易創(chuàng)新80余款創(chuàng)新方案亮相2024慕尼黑上海電子展

兆易創(chuàng)新閃耀2024慕尼黑上海電子展,以80余款創(chuàng)新方案引領(lǐng)智能未來(lái)

MWCS 2024 | 廣和通榮獲邊緣AI計(jì)算最佳創(chuàng)新方案

MWCS 2024 廣和通榮獲邊緣AI計(jì)算最佳創(chuàng)新方案

關(guān)于FEOL、BEOL和MOL的創(chuàng)新方案及通往1nm技術(shù)節(jié)點(diǎn)的可能途徑

關(guān)于FEOL、BEOL和MOL的創(chuàng)新方案及通往1nm技術(shù)節(jié)點(diǎn)的可能途徑

評(píng)論