Vivado有兩種工作模式:project模式和non-project模式。這兩種模式都可以借助VivadoIDE或Tcl命令來運(yùn)行。相比之下,VivadoIDE給project模式提供了更多的好處,而Tcl命令使得non-project模式運(yùn)行起來更簡(jiǎn)單。

在project模式下,Vivado會(huì)自動(dòng)管理整個(gè)設(shè)計(jì)流程和文件數(shù)據(jù)。最直接的體現(xiàn)是在Vivado左側(cè)導(dǎo)航Flow Navigator下會(huì)顯示所有流程,從設(shè)計(jì)輸入到最終生成bit文件。同時(shí),Vivado會(huì)自動(dòng)創(chuàng)建相應(yīng)的文件目錄,生成相應(yīng)的文件例如dcp以及相應(yīng)的報(bào)告。

Non-project模式是一種內(nèi)存編譯流程。用戶可以從指定位置讀取文件到內(nèi)存中,然后進(jìn)行編譯。可以逐步執(zhí)行每個(gè)步驟如綜合、布局、布線等,可以根據(jù)需求設(shè)定編譯參數(shù)。這一切都可以通過Tcl命令完成。顯然,non-project模式下,用戶可以通過Tcl命令管理設(shè)計(jì)文件和設(shè)計(jì)流程,體現(xiàn)了該模式的主要優(yōu)勢(shì)即用戶對(duì)設(shè)計(jì)流程有完全的掌控力。

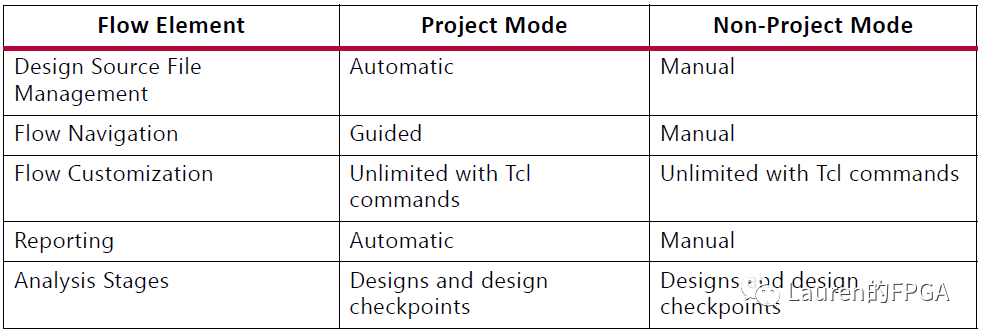

Project模式和non-project模式的主要區(qū)別如下圖所示。不難看出,project模式下更多的管理、操作都是“自動(dòng)”完成的;而non-project模式下,則是“手工”完成的。

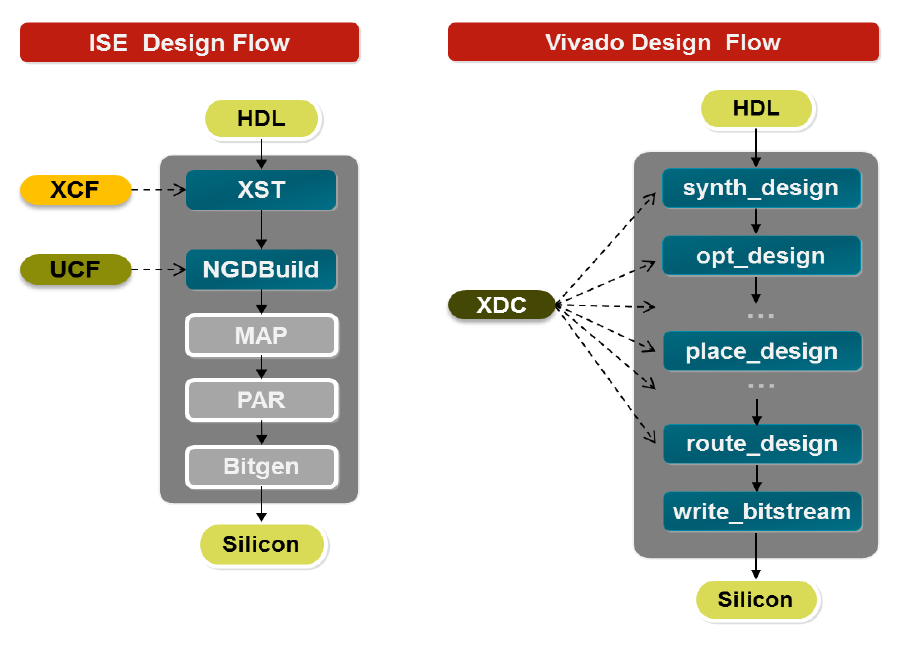

從Tcl命令的角度而言,project和non-project模式也是不同的,如下圖所示。Project模式下用到的Tcl命令是一種打包的命令,例如添加設(shè)計(jì)文件需用add_files,文件可以是HDL(包括VHDL,Verilog或SystemVerilog),可以是約束文件(包括.xdc或.tcl),可以是網(wǎng)表文件(可以是dcp,ngc或edif)等。Implementation時(shí),命令launch_runs就可以按照指定的策略完成所有的步驟,包括生成相應(yīng)的DCP。Non-project模式下用到的Tcl命令是分立的,例如,讀入設(shè)計(jì)文件,如果是VHDL,需要用到read_vhdl;如果是Verilog,需要用到read_verilog,如果是.xdc,需要用到read_xdc;如果是DCP,需要用到read_checkpoint;如果是EDIF,需要用到read_edif。而在implementation時(shí),需要分別用到opt_design、place_design、phys_opt_design和route_design等。

因?yàn)門cl命令使得non-project模式更能簡(jiǎn)單地運(yùn)行,這里我們將介紹如何通過Tcl命令在non-project模式下完成所有步驟。

責(zé)任編輯人:CC

-

TCL

+關(guān)注

關(guān)注

10文章

1725瀏覽量

88610 -

Vivado

+關(guān)注

關(guān)注

19文章

812瀏覽量

66539

原文標(biāo)題:用Tcl實(shí)現(xiàn)Vivado設(shè)計(jì)全流程(1)

文章出處:【微信號(hào):Lauren_FPGA,微信公眾號(hào):FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

在Vivado圖形化界面IDE中運(yùn)行和調(diào)試Tcl命令

用 TCL 定制 Vivado 設(shè)計(jì)實(shí)現(xiàn)流程

Vivado設(shè)計(jì)之Tcl定制化的實(shí)現(xiàn)流程

Tcl在Vivado中的基礎(chǔ)應(yīng)用

Vivado使用誤區(qū)與進(jìn)階——在Vivado中實(shí)現(xiàn)ECO功能

Vivado之TCL腳本語言基本語法介紹

如何使用Tcl命令語言讓Vivado HLS運(yùn)作

用Tcl定制Vivado設(shè)計(jì)流程詳解

FPGA設(shè)計(jì)中Tcl在Vivado中的基礎(chǔ)應(yīng)用

Vivado中常用TCL命令匯總

用TCL定制Vivado設(shè)計(jì)實(shí)現(xiàn)流程

在Vivado中實(shí)現(xiàn)ECO功能

Vivado設(shè)計(jì)套件Tcl命令參考指南

Vivado之實(shí)現(xiàn)布局布線流程介紹

如何用Tcl實(shí)現(xiàn)Vivado設(shè)計(jì)流程介紹

如何用Tcl實(shí)現(xiàn)Vivado設(shè)計(jì)流程介紹

評(píng)論