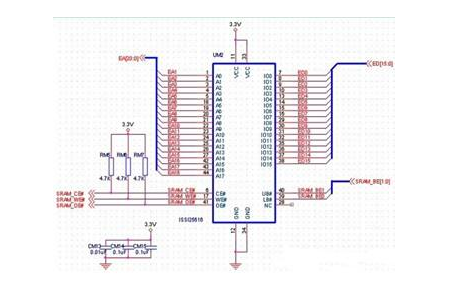

本應用筆記介紹了如何在不使用 AMBA 的情況下圍繞 ARM7TDM 構建典型的 SRAM 存儲器系統。有許多可能的方法來做到這一點。應該使用不同的方法,這取決于內存系統的大小(寬度)、要使用的內存類型以及是在片上還是片外。在決定要使用的內存系統時,必須平衡成本和系統性能。*簡介*

本應用筆記描述了如何在不使用 AMBA 的情況下圍繞 ARM7TDM 構建典型的 SRAM 存儲器系統。

有許多可能的方法來做到這一點。應該使用不同的方法,這取決于內存系統的大小(寬度)、要使用的內存類型以及是片上還是片外。在決定要使用的內存系統時,必須平衡成本和系統性能。

本應用筆記分為兩個主要部分。

* ARM7TDM 總線接口的描述。描述了總線接口的所有主要方面,從時鐘策略、總線配置和時序到內存訪問控制。

* 一個詳細的例子,展示了如何設計一個典型的內存系統。該示例假設一個小端系統,僅使用 SRAM 和 ROM。

ARM 開發了一種稱為 AMBA 的總線架構,使用該架構將提高可擴展性,極大地簡化系統設計,并有助于測試——尤其是在需要多個總線主控的應用中。

ARM 建議使用 AMBA 來設計基于 ARM 的系統。然而,本應用筆記解釋了如何在不使用 AMBA 方法的情況下將 ARM7TDM 連接到存儲器系統。

*ARM7TDM 總線基礎知識*

*_Bus Clocking_*

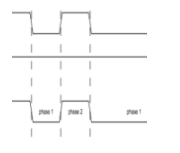

有兩個相關信號,MCLK 和 nWAIT。MCLK 對正常操作模式下的所有處理器活動進行計時。ARM 的靜態特性允許外部電路為慢速外設訪問延長時鐘的任一相位。一個典型的方案是使用一個帶有 40 MHz 時鐘的外部 PAL,該時鐘生成一個 20 MHz 時鐘,并根據需要進行擴展。這種技術在某些設計中可能難以使用。這種相位拉伸如圖 1 所示。

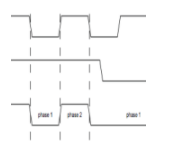

在系統中使用高頻時鐘的一種更簡單、更常見的替代方法是將 nWAIT 與 MCLK 結合使用。nWAIT 在內部與 MCLK 進行 AND 運算,因此為避免截斷階段 2(高)周期,nWAIT 只能在時鐘低周期(階段 1)期間安全更改。因此,nWAIT 技術只能用于延長時鐘低電平周期。這種技術如圖 2 所示。

編輯:hfy

-

ARM

+關注

關注

134文章

9137瀏覽量

368259 -

存儲器

+關注

關注

38文章

7521瀏覽量

164090 -

sram

+關注

關注

6文章

768瀏覽量

114761

發布評論請先 登錄

相關推薦

SRAM存儲器如何在網絡設計系統的應用

如何構建一個使用大量SRAM存儲器的應用?

SRAM存儲器主板基本設計的步驟

淺談異步SRAM存儲器接口電路圖

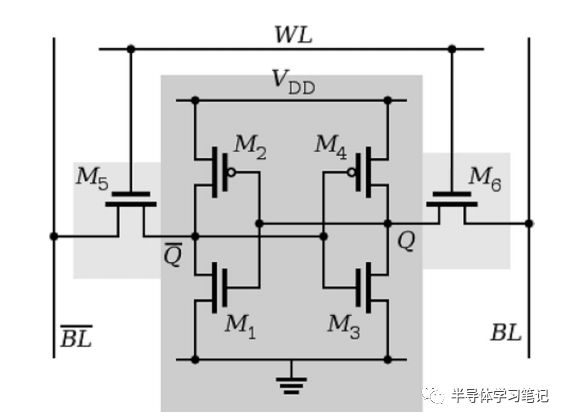

SRAM隨機存儲器的特點及結構

半導體SRAM存儲器綜述

SRAM隨機存儲器的特點及結構

SRAM存儲器的工作原理

如何不使用AMBA的構建典型的 SRAM 存儲器系統

如何不使用AMBA的構建典型的 SRAM 存儲器系統

評論