現代數字接收器中定位模數轉換器 (ADC) 是一個重要問題,它會嚴重影響設計選擇和實現成本。

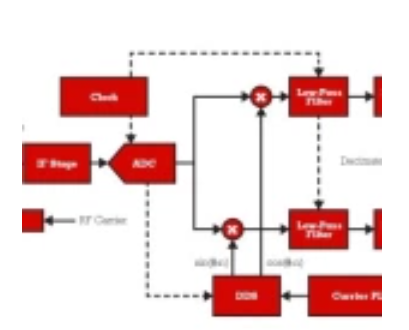

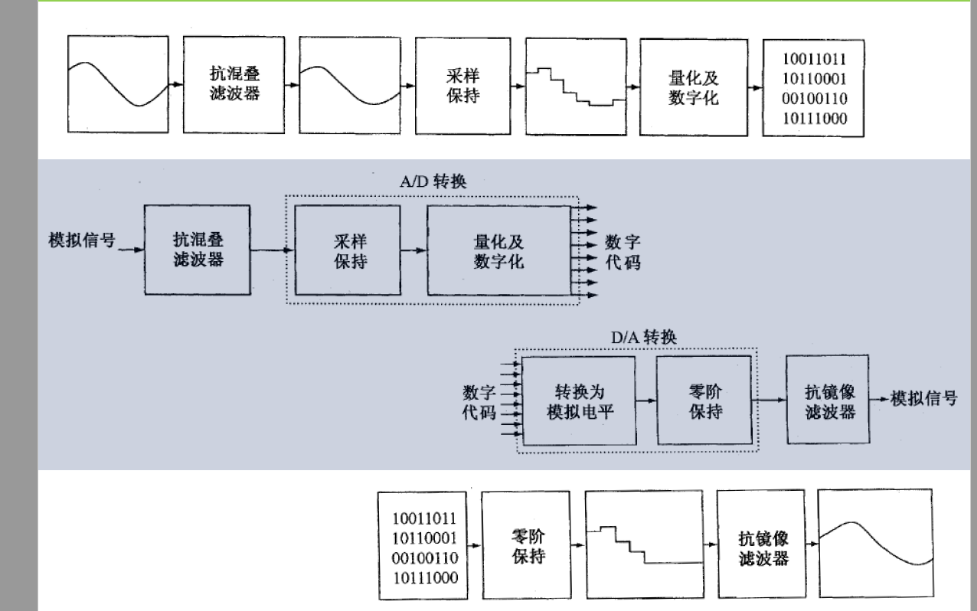

在現代數字接收器中定位模數轉換器 (ADC) 是一個重要問題,它會嚴重影響設計選擇和實現成本。通過信道傳輸的信號是通過稱為調制的過程應用所需信息內容(消息)的時間的模擬函數。無線信道給信號增加了噪聲。它還會產生多路徑并導致延遲和信號衰減。接收器必須與它的影響作斗爭。信道均衡通常在接收信號轉換為基帶后在數字域中執行。基帶下變頻任務通常需要不止一個步驟。模擬信號首先是 下變頻為中頻 (IF),然后拆分為同相和正交 (I/Q) 分量,然后進行基帶移位。在某些電信應用中,IF 采樣是通過避免中頻轉換直接將 I/Q 分量轉移到基帶的不錯選擇。然而,在大多數應用中不能應用中頻采樣,必須使用復雜的外差(模擬或數字,取決于應用)來實現頻率轉換。必須執行模數轉換的位置是接收機設計中的一個關鍵問題,插入數字信號處理 (DSP) 的最佳點取決于所需的系統性能要求和成本與帶寬和信號的匹配噪聲比(即 速度和精度)信號處理器和轉換器的限制。目前有兩種選擇:

將 ADC 立即放置在 IF 移位模塊之后,其中 I/Q 組件的基帶下變頻完全在數字域中執行。

在 I/Q 分量轉換為基帶之后放置 ADC(I/Q 下變頻仍然在模擬域中執行,而解碼、一些時間恢復任務和信道均衡在數字域中執行)。

第一種方法需要高性能 ADC,這意味著高功耗和增加的設計成本。但它的優點是可以在接收器鏈中較早地應用數字信號處理,這在一些新應用(即軟件定義無線電)中是強烈推薦的。另一方面,第二種方法放寬了對 ADC 的要求,但增加了 I/Q 組件的不平衡(當使用兩個 ADC 時)以及時序不匹配(當在乒乓配置中僅使用一個 ADC 時) 。

在本文中,我們描述了在通過模擬外差將復數 I/Q 分量移至基帶后對復數 I/Q 分量執行模數轉換的方法。特別地,我們描述了數字 I/Q 不平衡校正所需的數字電路——在這種情況下這是必要的——以及 I/Q 組件的時間恢復,當在乒乓配置中使用單個 ADC 時尤其需要。

IF 信號的模數轉換

當用于轉換中頻信號時,如圖 1 的數字接收器所示,對 ADC 的要求變得更加嚴格。實際上,真實 IF 信號比其復雜的 I/Q 基帶分量具有更寬(大約兩倍)的帶寬。根據奈奎斯特定理,采樣頻率必須至少選擇為單邊信號帶寬 BW 的兩倍,才能完全捕獲其信息內容。請注意,對于低通信號,信號的單邊帶寬與其最高頻率分量一致。實際上,奈奎斯特定理所描述的最低采樣率(fs=2*BW)只是一個理想的極限。對于新手系統設計者來說,這是一個下界和夢想。眾所周知,必須選擇采樣頻率以確保頻域中有一些自由空間 ΔΔf,用于分配抗混疊濾波器的過渡帶寬 (fs=2*BW+Δf)。高采樣率和高精度采樣時鐘是ADC難以獲得的特性;它們極大地影響了設計成本。高分辨率、高靜態線性度和動態線性度是轉換器處理寬帶信號需要考慮的其他基本要求。

流水線和 Σ-Δ ADC 是通信系統中最常用的架構。雖然流水線架構具有通過增加轉換級數來提高分辨率的優勢,但本質上是窄帶 ADC 的 sigma-delta 轉換器可以完成單通道應用中所需的一些任務(當以極高的速度起訴時)時鐘頻率)。通常,為了使噪聲整形有效,轉換器過采樣率必須為 16 或更高。盡管需要高采樣率,但 delta-sigma 轉換器具有一些適用于通信應用的有用功能。例如,可以設計具有非對稱信號傳遞函數的復雜帶通 delta-sigma,為低中頻信號提供額外的鏡像抑制。

為了使用較低的采樣頻率,對于接收信號具有稀疏或帶通性質的某些特定電信應用(例如,蜂窩基站),通常的做法是以較小的速率對中頻信號進行采樣其最大頻率的兩倍(IF 采樣或低速率采樣)。當應用于 IF 信號時,以低速率采樣方式,單個 ADC 將實際信號數字化,然后使用數字信號處理方法將其轉換為數字域中的復雜分量。這種技術的優點包括降低硬件復雜性、工作量、功耗和成本。這些優勢是可能的,因為 IF 采樣方法會自動執行部分下變頻任務。

盡管 IF 采樣技術提供了許多好處,但一個重要的缺點是噪聲混疊。如果輸入信號的頻帶限制不夠,這種混疊會降低等效 ADC SNR 性能,從而允許混疊頻帶中的噪聲與所需信號一起被數字化并轉換為基帶。此外,在應用中頻采樣時,系統需要配備過渡帶相對較窄的帶通抗混疊濾波器。窄過渡帶意味著高品質因數 Q 以及高濾波器階數。因此,IF 采樣只能用于某些特定應用。例如,當接收頻譜中存在相鄰干擾信號時(即輸入信號不具有稀疏性),中頻采樣就不是一個可行的選擇;相當,

與其討論需要高性能 ADC 的中頻信號采樣的可能性,或探索使用低速率采樣的可能性,我們將重點關注執行低通采樣 (fs=2*BW+?f) 的選擇通過一對模擬混頻器將復雜的 I/Q 信號分量移至基帶。在接下來的部分中,我們提出了兩種執行 I/Q 采樣的方法,討論了它們各自隱含的缺點,并提供了數字補償電路來糾正它們對采樣數據信號的負面影響。

I/Q 組件的模數轉換

在將 I/Q 分量轉移到基帶之后對其進行數字化是當今通信接收器中最常用的解決方案。這種方法的優點是放寬了 ADC 要求,因為基帶組件的帶寬大約是相應真實 IF 信號帶寬的一半。

I/Q 分量的采樣可以通過兩種方式實現:

一對匹配的(幾乎)ADC。

具有乒乓配置的單個 ADC。

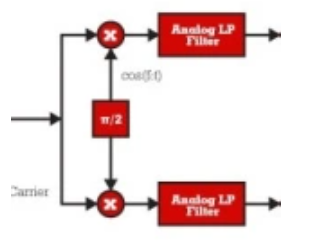

具有兩個轉換器的解決方案(其框圖如圖 2 所示)放寬了 ADC 要求,但有助于增加 I/Q 不平衡,這主要是由將信號移至基帶的一對模擬匹配混頻器引入的。

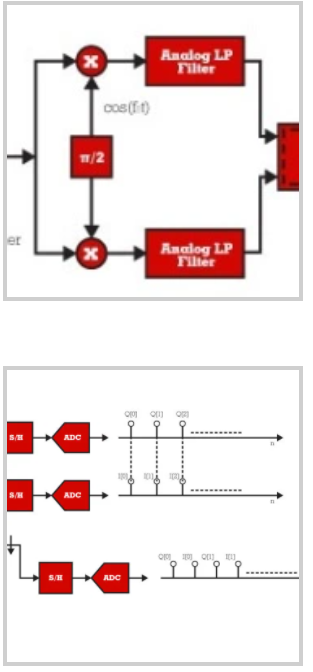

如圖 3 所示,采用乒乓配置的一個轉換器的解決方案不會增加 I/Q 不平衡。然而,它需要一個數字時間恢復電路來補償由 I 和 Q 分量之間的乒乓引起的定時偏移。在此配置中,“乒乓”S/H 級與通用 ADC 輸入相鄰。乒乓級作為兩個 S/H 模塊運行,每個模塊對同相和正交輸入通道進行采樣。然后將來自兩個通道的采樣數據多路復用為單個模擬數據流,并由工作在 fs‘=2*fs 的單個 ADC 進行量化,其中 fs 是 I 和 Q 輸入采樣的頻率。然后,解復用器獲取 ADC 輸出樣本,并使它們在 I 和 Q 數字輸出總線上可用。乒乓 S/H 級可以設置為單通道操作,在這種情況下,同一 ADC 可用于以全 fs 采樣率對 IF 信號進行數字化,或用于以 ADC 采樣率 fs 操作的多通道=M*fs 其中 M 是通道數。由于使用了單個 ADC,因此該解決方案非常緊湊。

請注意,在標準配置中,兩個 ADC 用于同時采樣同相和正交分量。并且由于采樣同時發生在 I/Q 路徑上,因此從兩個組件導出的樣本之間沒有時間偏移(有關更多詳細信息,請參見圖 4)。但是,當在乒乓配置中使用單個 ADC 時,I/Q 組件的采樣不會同時發生。事實上,I/Q 分量是按順序采樣的。因此,代表兩個分量之一的樣本導致半個采樣周期偏移,這使得在系統中包含同步電路是必要的。由于影響 I/Q 分量的不平衡是影響信號重建的麻煩來源,

在本文的最新部分,我們還提供了在乒乓配置中使用單個轉換器時用于數字時間補償的帶通、1 對 2 內插器的架構方案。

數字 I/Q 平衡

調制解調器中模擬正交混頻器的增益和相位失配會導致上變頻或下變頻信號的正負頻率分量發生不希望有的耦合。眾所周知,這種耦合是一種干擾,會影響通信路徑的性能。造成不平衡的最大因素是一對(幾乎)匹配的平衡混頻器。但是,兩條路徑中的所有模擬組件(例如濾波器和模數轉換器)都會導致失配。在模擬單邊帶電話系統的時代,與不平衡相關的干擾被視為用戶語音通道中令人討厭的第二音頻信號。在當今的調制方案中,干擾限制了通信系統的星座密度。

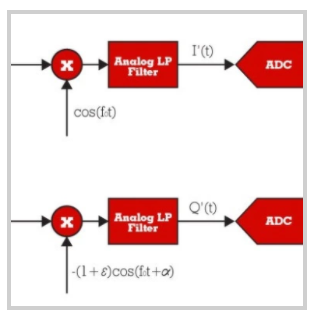

在處理寬帶信號的接收器中,控制失配變得更加重要。圖 5 顯示了 I/Q 下變頻器的增益和相位不平衡模型。雖然在兩條路徑之間分割增益和相位誤差項是常見的做法,但我們發現這對增強對問題的理解幾乎沒有作用。所以我們選擇僅將誤差分配給兩個臂之一。

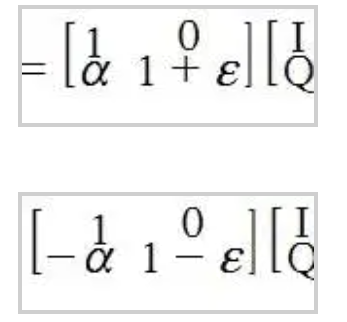

圖 6 顯示了信號模型,說明了失配對觀察到的時域信號的影響。觀察到的正交項 I’ 和 Q‘ 通過等式 (1) 中所示的關系與所需的正交項 I 和 Q 相關。此外,等式 (2) 中顯示的是這種關系的近似倒數,它根據觀察項計算所需項。

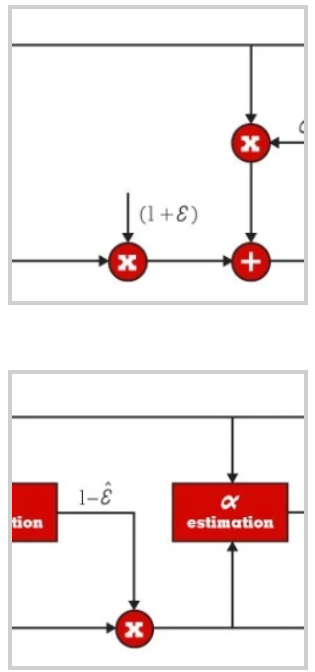

等式 (2) 中的近似倒數反映了由圖 7 所示的 I/Q 數字平衡系統執行的信號處理任務。和 ?可以用 1-tap 梯度濾波器遞歸實現。

數字時間恢復

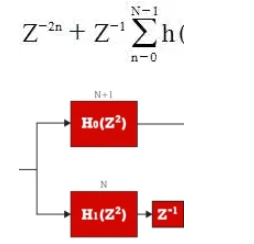

在乒乓配置中使用時,模數轉換階段需要跟隨一個必須應用于采樣數據流的數字定時恢復階段,從而導致半個采樣周期的偏移。這種情況下的時序恢復電路很容易通過使用基于數字半帶濾波器的低成本 1 比 2 多速率插值架構來實現。圖 8 顯示了基于零插入以提高輸入采樣率的 1 對 2 上采樣過程的初始形式。

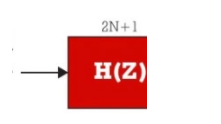

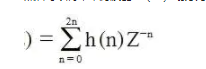

然后可以將半帶濾波器 H(Z) 劃分為一對多相濾波器,如等式 (3) 和 (4) 以及圖 9 所示。

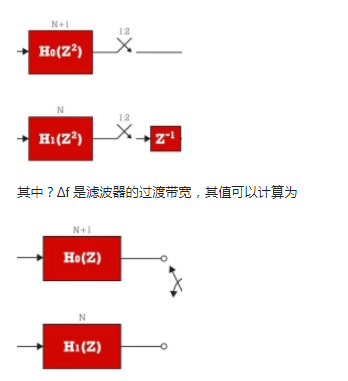

重采樣和濾波的順序可以顛倒,形成圖 10 所示的形式。 最后,如圖 11 所示,一對 l-to-2 上采樣開關和采樣延遲可以用兩個-tap 換向器執行等效的路徑輸出調度到輸出樣本流。

圖 11 表示為所需的時間恢復任務選擇的 1 比 2 帶通內插器的架構。請注意,原型濾波器設計有 2N+1 個抽頭,然后分成兩條路徑,其中一條路徑包含零值抽頭,并作為僅延遲路徑實現,另一條路徑包含剩余的 N 個非零抽頭。濾波器需要 N 個算術運算 (ops) 來生成兩個輸出樣本以響應每個輸入樣本。當我們在兩個輸出上分配每個輸入的 N 個操作時,我們發現過濾器工作負載是每個輸出 N/2 個操作。通過利用較低路徑濾波器中系數集的偶對稱性,可以將每個輸出的乘法次數減少 2 倍。為了完整起見,我們在此報告圖 11 中所示濾波器的長度可以估計為

哪里α?是濾波器的過渡帶寬。請注意,從等式 (5) 和 (6) 可知,隨著濾波器的分數帶寬增加,導致過渡帶寬減小,濾波器長度增加。

在 1-to-2 內插階段之后,完成時間恢復的唯一剩余任務是對信號進行下采樣,2-to-1,以丟棄位于錯誤時間位置的樣本。請注意,我們將要丟棄的樣本是圖 11 中 1 到 2 內插器的上路徑輸出的樣本。 因為計算樣本沒有意義,稍后將在 2:1 下采樣中丟棄這些樣本在此過程中,信號內插和信號抽取可以通過僅通過由原型半帶濾波器的非零抽頭組成的下內插器路徑處理輸入信號來合并。

參考

fj harris,“通信系統的多速率信號處理”,Prentice Hall,Upper Saddle River,新澤西州 07458,2004 年。

F。harris 和 W. Lowdermilk,“軟件定義無線電:教程”,IEEE 儀器和測量雜志,2010 年 2 月。

C. Dick, B. Eggs 和 f. harris,“窄帶波形的 FPGA 實現時序同步電路的架構和仿真”,SDR 論壇,2006 年,第 1-6 頁。

Fredric J. Harris 和 Michael Rice,“用于軟件定義無線電中符號定時同步的多速率數字濾波器”,IEEE 通信選定領域雜志,卷。19,沒有。12,第 2346-2357 頁,2001 年 12 月。

Rice, M., Dick, C., & Harris, F. (2001)。“基于 FPGA 的軟件定義無線電中的最大似然載波相位同步”。doi:10.1109/ICASSP.2001.941058。

FM Gardner,“數字調制解調器中的插值,第一部分:基礎”,IEEE 通信交易,第 41 卷,第 3 期,第 501-507 頁,1993 年 3 月。

編輯:hfy

-

模數轉換器

+關注

關注

26文章

3218瀏覽量

126972

發布評論請先 登錄

相關推薦

數字信號處理教程之模數轉換和數模轉換

淺談IF 信號的模數轉換和I/Q 組件的模數轉換

淺談IF 信號的模數轉換和I/Q 組件的模數轉換

評論