撰稿人:Ed Kohler 和 Jason Messier 與 Intersil

在越來越廣泛的高性能應用要求的推動下,模數轉換器 (ADC) 正成為越來越普遍的設計元素,性能、成本和復雜性之間的眾多權衡是產品設計整體成功的關鍵因素。

盡管 ADC 永遠不會有簡單的一刀切解決方案,但現在 ADC 設計中的許多持續技術趨勢使設計人員能夠密切定制 ADC 選擇,以優化成本和性能以滿足其特定應用要求。本文旨在提供這些技術趨勢的概述,以及一些設計示例,以便為理解不同方法之間的實際權衡提供背景。

ADC 趨勢:在 SNR、分辨率、采樣率和功率之間取得平衡

ADC 設計必須在給定的性能標準(例如信噪比 (SNR)、分辨率和采樣率)之間實現適當的平衡,同時還要符合通常非常嚴格的功率預算。

ADC 功能的一個主要趨勢是在給定的采樣率下持續推動更高的分辨率和 SNR 性能。例如,對于每秒 500 兆次采樣 (MSPS),當今最新的高性能 ADC 可以在 14 位時提供 72.5dB,而之前的 ADC 功能在 12 位時只能提供 66-67dB。這一進步得益于最先進的設計技術和半導體處理能力的進步,在大約五年的時間里,可實現的信噪比基本上實現了 100% 的改進。

改進的另一個趨勢軸是增加給定分辨率和 SNR 的可用最大采樣率。就在一年前,只有兩家主要 ADC 供應商提供 14 位 ADC,其采樣率高于 155 MSPS。現在,大多數 ADC 制造商正在將采樣率提高到 250 MSPS,其 14 位設備可以提供 70dB 或更好的 SNR 性能,有些制造商正在提供可以提供超過 73dB 的第二代產品。同樣,16 位轉換器的最大采樣率已從 2008 年的 200 MSPS 提高到 2010 年末的 250 MSPS,同時將 SNR 保持在 75dB 以上。寬帶通信測試設備和高級醫學成像等應用對分辨率和速度的要求不斷提高,推動了高分辨率 ADC 采樣率的不斷提高。

對于許多 ADC 應用來說,低功耗操作也是一個越來越重要的因素。對于必須在嚴格的功率預算內工作的手持設備以及需要許多 ADC 的設計尤其如此,其中組合功耗成為一個重要問題。正如本文后續部分將討論的那樣,在給定的 SNR、分辨率和采樣率性能水平下將功耗降至最低的能力可能是整個產品設計成功的關鍵關鍵問題,并且至少有一個低功耗ADC 架構的出現就是為了滿足這種需求。

ADC 設計趨勢變化的另一個領域是用于獲取芯片內外數據的各種接口技術。最初,CMOS I/O 足以支持大多數應用程序。然而,不斷提高的性能要求導致了更快的 I/O 方法的發展,包括 DDR、LVDS、串行 LVDS 和潛在的 SERDES 接口(雖然本文主要關注關鍵性能和功耗的權衡,但我們將在以后的文章中探討正在進行更深入的 ADC 接口演進)。

場景 #1 關鍵目標:實現高 SNR 和動態范圍

對于許多更高性能的應用,最重要的要求是在不考慮功耗問題的情況下實現 SNR 和動態范圍參數。

這些性能優先應用的主要例子是關鍵任務軍事設計,如雷達信號處理。推動此類設計的關鍵特性之一是需要同時處理大信號和小信號,并且能夠區分兩者,這需要出色的動態范圍和 SNR 性能。例如,在雷達系統中,必須以一致的精度和速度同時處理來自近處和遠處物體的強弱返回信號。如果ADC沒有足夠的動態范圍,那么較大的信號將完全支配轉換器的整個范圍,系統將看不到較弱的信號。

另一類通常屬于這一類的應用是高性能測量儀器,例如信號分析儀。系統設計人員通常必須創建一組強大的功能和一個跨越廣泛信號靈敏度的性能窗口,而不是為一組固定參數預先定制盒子。同樣,在高采樣率下圍繞具有最大動態范圍和穩健 SNR 特性的 ADC 從頭開始??構建,是使儀器平臺能夠提供最寬性能窗口的方法。

類似的挑戰存在于許多通信應用中,例如必須區分強弱信號以確定正確路由和切換過程的無線基站。在所有這些應用中,唯一的選擇是使用在所需采樣率下提供盡可能高的動態范圍和 SNR 特性的 ADC 進行設計。

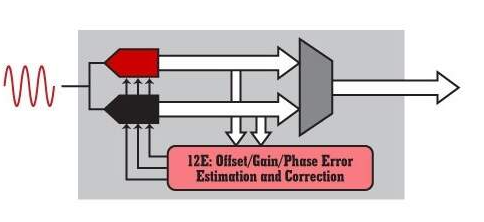

在這些應用中證明非常有用的一種先進設計方法是緊密集成多個 ADC 內核,這些內核使用先進的片上硬件(例如專有的 Intersil 交錯引擎 (I2E))進行交錯。在這種方法中,混合數字/模擬背景校準技術連續調整多個交錯 ADC 內核的增益、偏移和采樣相位,消除固有的制造不匹配,并實時調整由溫度和電壓引起的任何不匹配變化(見圖 1)。

Intersil 交錯引擎 (I2E)

在系統級(例如 6 位、8 位甚至 10 位器件)交錯較低分辨率的 ADC 已成為一種相當標準的做法,特別是對于無雜散動態范圍 (SFDR)主要關注。然而,對于需要 12 位及以上轉換器分辨率的高性能應用,交錯 ADC 可能變得非常復雜,最好在芯片級實現。ADC 內核的芯片級交錯克服了性能的動態變化,當嘗試以更高分辨率交錯分離 ADC 時,這些變化會成為障礙。控制良好的工藝匹配以及共同的電壓和溫度特性在本質上提供了內核之間更好的均勻性,這是單獨設備無法實現的。

為了實現近乎完美的匹配,片上 I2E 校準透明地動態微調性能以確保一致性并消除差異。I2E 的實時調整利用任意應用樣本數據來估計和校正增益、偏移和采樣時間偏差的交錯失配。這使得多個內核能夠作為單個高性能 ADC 一起運行,可以有效地將采樣率乘以內核數量,而無需對動態范圍、SNR 或穩健性做出任何妥協

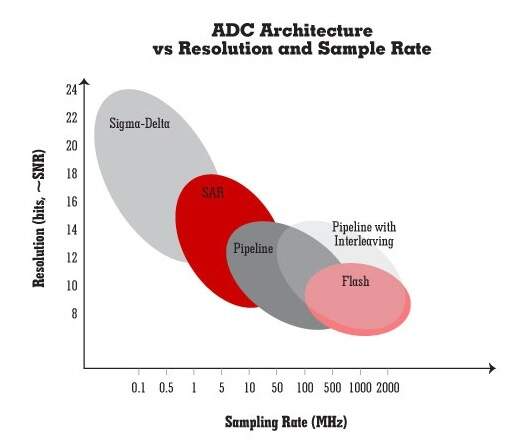

如圖 2 所示,與沒有高級交錯的 Sigma-Delta、SAR 或流水線架構相比,具有高級交錯的 ADC 架構可以在高采樣率下提供最??高水平的分辨率。例如,Intersil 的 ISLA214P50 集成了兩個時間交錯的 14 位 250MSPS ADC,以實現 500MSPS 的采樣率和 72.7dBFS 的 SNR 性能。

ADC 架構與分辨率和采樣率的比較

場景 #2 – 需要靈活性以在性能、功耗和設計復雜性之間進行權衡

在這些情況下,設計人員通常可以靈活地以不同方式處理應用,從而在 ADC 選擇中實現性能、功耗和其他設計考慮因素之間的權衡。例如,該類別包括信號電平可能變化但變化是可預測或可管理的應用,這樣系統可以設計為調整和適應變化。

例如,兩個站之間的點對點微波通信鏈路通常涉及較少的信號變化,因為它使用聚焦天線,在發送點和接收點之間的阻塞最小。然而,信號電平偶爾會受到天氣條件(例如下雨、雨夾雪)的影響。這允許系統設計的多種方法。一種設計選擇是使用具有足夠寬動態范圍的高端 ADC,如前一場景中所述,以簡單地即時捕獲和處理減弱的信號。或者,設計人員可以通過選擇動態范圍較低的 ADC 并使用增益控制電路根據天氣條件調整信號路徑來進行權衡,以便始終以一致的電平向 ADC 提供信號。當然,

此類別中另一個有趣的應用可能是激光測距儀,其中向多個方向發送固定強度的信號,然后使用返回信號的強度和時間特征進行距離測量,以創建復雜空間的 3D 映射。信號測量需要同時考慮表面反射率和到被測物體的距離。從信號處理的角度來看,許多設計權衡對此類應用產生影響。

例如,當使用分辨率較低的 ADC 時,通過消除平均的需要,可以使用更高分辨率的 ADC 來更快地解析信號,從而允許以更少的脈沖進行更快的測量。繪制某些位置可能需要數百萬次測量,因此每次測量的時間量可能是一個重要因素。另一方面,激光測繪應用的性質可能需要一定程度的系統便攜性,甚至需要電池供電平臺用于某些戶外應用,例如測繪橋架。根據特定的應用要求,設計人員可能會選擇低功耗、低分辨率的 ADC 與外部電路相結合來平均結果,

對于需要在 ADC 功能方面進行各種權衡的這些應用領域,利用引腳兼容的器件系列可能是有利的,這為設計人員提供了比單點產品更廣泛的選擇。例如,需要在分辨率和采樣率之間進行權衡的設計人員可以首先使用 14 位 500 MSPS 部件進行原型設計,如果需要,可以轉移到同一系列中的 16 位 250 MSPS 引腳兼容器件,而無需對設計進行任何更改。

同樣,如果設計人員需要針對給定的分辨率和采樣率在 SNR 與功耗之間進行權衡,那么使用提供多種選擇的引腳兼容系列會很有幫助。例如,一些系列提供多個性能等級,可以提供兩個或更多級別的 SNR,更高的 SNR 以增加功耗為代價。無需對底層硬件進行任何更改,即可再次提供用于延長電池壽命或提高性能的產品設計。

這種靈活性允許設計人員定制和微調 ADC 功能以滿足特定應用要求,而無需更改整體產品設計和支持電路。利用引腳兼容系列的能力還為營銷具有不同性能水平的相同基本產品設計的多個版本提供了選擇,以滿足更廣泛的市場需求。

場景 #3 – 最大限度地減少用電量是關鍵因素

在這最后一組應用中,提供超低功耗操作是設計成功的首要因素。該類別中的典型產品是需要更高帶寬和便攜性的手持設備,例如軍用和執法無線電、超聲波無損掃描儀和便攜式有線電視信號分析儀。有時,此類應用中還包括部署的 ADC 的剪切數量具有需要最小化的累積功率使用影響的應用,例如具有數千個 ADC 的某些有線通信系統,其中整體基礎設施的功率預算變得很重要因素。

在所有這些情況下,設計人員都需要具有給定的動態范圍,但必須以盡可能低的功率水平實現該性能。因此,ADC 制造商必須通過超低功耗芯片級架構來滿足性能要求。此外,ADC 架構應為設計人員提供靈活性,以最大限度地降低支持電路和整體設計中的功率要求。

Intersil 的 FemtoCharge? 技術代表了在創建超低功耗 ADC 實施方面向前邁出的重要一步,該技術從根本上改變了流水線信號處理設計的方法。對于任何流水線 ADC 信號處理鏈,級之間都需要增益。在傳統架構中,每個增益級中的信號傳統上由電壓表示。相比之下,FemtoCharge 架構改變了方法并使用電荷表示信號。這似乎是一個微妙的差異,但實際上,它對降低功耗具有重大意義。

在大多數流水線 ADC 設計中,信號必須逐級放大以獲得必要的轉換分辨率。基于電壓的設計有兩個限制。首先,信號增益需要運算放大器 (Op-Amp),并且由于高速和高精度的雙重要求,這些運算放大器具有高功耗并限制了整體 ADC 性能。其次,基于電壓的設計需要在每個階段重新創建信號。相比之下,基于電荷的 ADC 使用電容縮放來實現級間增益。在電容器中,電壓 = 電荷/電容。因此,每個連續級所需的電壓增益可以簡單地通過降低其相對于前級的電容來創建。而且,不必為每個階段從頭開始重新創建基于電壓的信號,

基于電壓和基于電荷的管道架構比較

FemtoCharge 方法可以創建具有超低功耗特性的高性能 ADC。例如,ISLA216P25IRZ 是一款 16 位 250 MSPS ADC,它是第一款也是唯一一款采樣率超過 175 MSPS 且功耗低于 1 瓦(250 MSPS 時為 786 mW)的 16 位轉換器。此外,像 ISLA214P50IRZ 這樣的基于電荷的 ADC 不僅是第一個 14 位 500MSPS 轉換器,而且還提供 73dB 的 SNR,并且僅消耗 835-900 mW,提供大約 3dB 的 SNR,而其功率僅為其唯一的三分之一250 MSPS 以上的競爭對手。因此,基于電荷的設計為系統設計人員提供了一套全新的選項,可以在不影響性能的情況下最大限度地降低功耗。

底線:更多選項可實現更好的設計權衡

盡管新一代產品的需求不斷升級,并且要求以越來越低的功率預算進行更苛刻的信號處理,但對設計人員來說,好消息是新一代 ADC 架構一直處于領先地位。

具有透明片上校準功能的共享芯片、多核交錯架構等新的進步現在可以創建非常高分辨率、高采樣率的 ADC,這些 ADC 不會影響 SNR 性能,同時最大限度地降低設計復雜性和功耗。此外,FemtoCharge 等突破性技術從根本上改變了流水線 ADC 設計方法,從而實現了更大的節能。

設計人員的底線是有更廣泛的選項可供選擇,這會導致更好的權衡和更有效的 ADC 功能定制,以滿足總體設計目標。

編輯:hfy

-

轉換器

+關注

關注

27文章

8741瀏覽量

147690 -

adc

+關注

關注

99文章

6531瀏覽量

545394 -

模數轉換器

+關注

關注

26文章

3217瀏覽量

126938 -

SNR

+關注

關注

3文章

196瀏覽量

24478

發布評論請先 登錄

相關推薦

了解模數轉換器(ADC):解密分辨率和采樣率

高分辨率模數轉換器的噪聲有什么影響?

如何選擇示波器的帶寬、采樣率、存儲深度、垂直分辨率

用于實現12.8GSPS采樣率的交錯射頻采樣模數轉換器的實用示例

為什么我們需要模數轉換器?哪個ADC轉換器更好?

深度剖析模數轉換器(ADC)的解密分辨率和采樣率

ADS5485 采樣率200MSPS 16位單通道模數轉換器

基于高分辨率模數轉換器的振動信號采集系統設計

用于實現12.8GSPS采樣率的交錯射頻采樣模數轉換器示例

解密模數轉換器的分辨率和采樣率

模數轉換器 (ADC) 設計 SNR、分辨率、采樣率和功率的平衡

模數轉換器 (ADC) 設計 SNR、分辨率、采樣率和功率的平衡

評論