本應用筆記介紹了 RL78 系列的注意事項和噪聲對策。它描述了 PCB 上 RESET 引腳和時鐘 IO 引腳的最短布線長度、跨 VSS 線和 VDD 線的旁路電容器連接、模擬輸入引腳的布線以及振蕩器問題,例如大電流信號線和避免電位電平頻繁變化的信號線。

最短接線長度

印刷電路板上的布線可以用作天線,將噪聲吸引到 MCU 中。總布線長度越短(以 mm 為單位),噪聲被吸入 MCU 的可能性就越小。

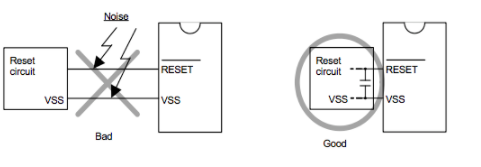

(RESET)‘ 引腳

的接線 使連接到 (RESET)’ 引腳的接線長度盡可能短。在(RESET)‘引腳和VSS引腳之間連接電容時,以及將reset IC與其對應引腳連接時,線長應特別短(20mm以內)。

原因:

輸入到 (RESET)’ 引腳的脈沖寬度由時序要求決定。如果脈沖寬度比標準更短的噪聲輸入到 (RESET)‘ 引腳,則在 MCU 的內部狀態完全初始化之前解除復位。這可能會導致程序失控。

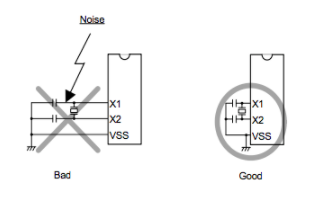

(RESET)’ 引腳的接線時鐘輸入/輸出引腳接線

使連接到時鐘 I/O 引腳的接線長度盡可能短

連接振蕩器的電容器的接地線和 MCU 的 VSS 引腳之間的接線長度(在 20 mm 內)盡可能短。

時鐘輸入/輸出引腳接線

原因:

如果噪聲進入時鐘輸入/輸出引腳,時鐘波形可能不穩定。這可能會導致程序失敗或程序失控。此外,如果 MCU 的 VSS 電平和振蕩器的 VSS 電平之間的噪聲引起電位差,則 MCU 中將不會輸入正確的時鐘。

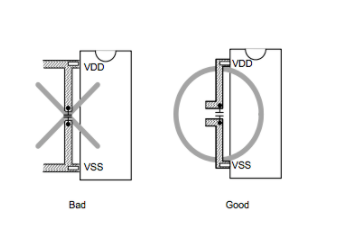

跨 VSS 線和 VDD 線連接旁路電容器

如下所述,在VSS線和VDD線之間連接大約0.1 μF的旁路電容器:

在 VSS 引腳和 VSS 引腳之間連接一個等長的旁路電容

使用盡可能短的接線在 VSS 引腳和 VDD 引腳之間連接一個旁路電容器

VSS和VDD線使用直徑大于其他信號線的線

通過旁路電容將電源線連接到 VSS 引腳和 VDD 引腳。

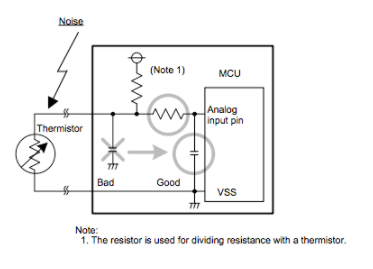

跨 Vss 線和 VDD 線的旁路電容器連接到模擬輸入引腳

將大約100Ω至1kΩ的電阻連接到模擬信號線,該信號線串聯連接到模擬輸入引腳。將電阻盡可能靠近 MCU。

在模擬輸入引腳和 VSS 引腳之間插入一個大約 1000 pF 的電容器,使其盡可能靠近 VSS 引腳。模擬輸入引腳和電容器之間的導線以及VSS引腳和電容器之間的導線應等長。

模擬信號線、電阻器和電容器

原因:

輸入到模擬輸入引腳的信號通常是來自傳感器的輸出信號。大多數檢測事件的傳感器都遠離安裝了 MCU 的電路板。模擬輸入引腳的接線不可避免地更長。這條長接線起到天線的作用,將噪聲吸引到 MCU 中,從而對模擬輸入引腳產生噪聲。

編輯:hfy

-

電容器

+關注

關注

64文章

6227瀏覽量

99773 -

mcu

+關注

關注

146文章

17171瀏覽量

351501 -

電阻器

+關注

關注

21文章

3784瀏覽量

62174 -

模擬信號

+關注

關注

8文章

1133瀏覽量

52483

發布評論請先 登錄

相關推薦

RL78 dataflash pfdl庫使用教程

瑞薩電子推出的RL78/I1x系列微控制器是RL78微控制器系列

RL78/G23 Data flash使用教程

RL78族噪聲的相關注意事項及對策應用說明

E1/E20 Emulator, E2Emulator Lite 用戶手冊附加文件(RL78連接注意事項)(for RL78/G10, RL78/G1M, RL78/G1N)

Renesas Flash Driver RL78 Type 02RL78/F23 和 RL78/F24 用戶手冊

EEPROM 仿真軟件 RL78 Type 02RL78/F23 和 RL78/F24 用戶手冊

Renesas Flash Driver RL78 Type 02RL78/F23 和 RL78/F24 用戶手冊

EEPROM 仿真軟件 RL78 Type 02RL78/F23 和 RL78/F24 用戶手冊

E1/E20 Emulator, E2Emulator Lite 用戶手冊附加文件(RL78連接注意事項)(for RL78/G10, RL78/G1M, RL78/G1N)

RL78 系列的注意事項和噪聲對策分析

RL78 系列的注意事項和噪聲對策分析

評論