本文檔提供了符合IDT的PCI Express 2.0基本規范的系統互連交換機設備系列的系統設計指南。本文檔還描述了以下設備接口,并提供了相關的電路板設計建議。

PCI Express接口:端口配置

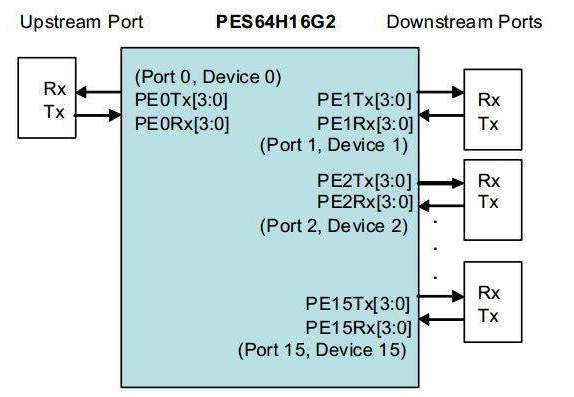

PES64H16G2的16個端口中的每個端口在統計上分配了4個通道,端口標記為0到15。在默認配置中,SWMODE [3:0] = 0x0,端口0始終是上游端口,其余端口始終是上游端口端口始終是下游端口。在多分區配置SWMOE [3:0] = 0xC或多分區串行EEPROM初始化配置SWMOE [3:0] = 0xD中,所有端口都未連接。通過串行EEPROM或從SMBus接口,可以將任何端口配置為上游端口或下游端口。所有端口均可在最大鏈路寬度x4(即4條通道)上運行,并支持2.5 GT / S(第一代)和5.0 GT / S(第二代速度)。

參考時鐘(REFCLK)電路

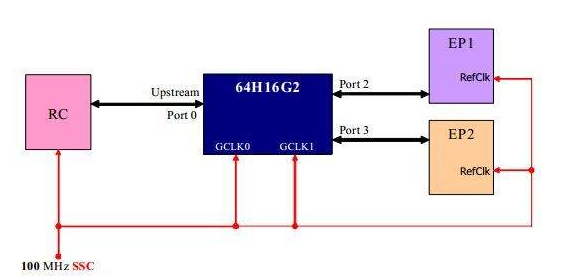

開關具有兩個差分全局參考時鐘輸入(GCLKP [1:0] / GCLKN [1:0]),用于生成內部開關邏輯和SerDes所需的所有時鐘。差分時鐘輸入需要信號源來驅動0V共模,并且REFCLK信號必須滿足PCI Express卡機電規范中定義的電氣規范。參考輸入時鐘上不需要交流耦合。

參考時鐘輸入支持擴頻時鐘(SSC),以降低EMI。所需的方法是調整擴頻技術,使其不允許在標稱頻率以上進行調制。這種技術通常稱為“向下擴展”。如果使用SSC,則所有時鐘都必須來自一個時鐘源。這包括交換機本身的時鐘,連接到交換機下游端口的設備的時鐘,以及連接到交換機上游端口的根聯合體芯片組或其他設備(交換機或網橋)的時鐘。如果不使用SSC,則樹中的每個PCI Express設備都允許使用多個時鐘源。

交換機和十五個下游設備的差分時鐘可以從時鐘緩沖器/發生器(例如ICS9DB803)獲得。系統設計人員可以使用其他與Gen2兼容的時鐘緩沖器/發生器。ICS9DB803器件用于IDT評估板上。

交換機為交換機的每一側提供兩種時鐘操作模式:全局時鐘和本地端口時鐘。系統設計人員必須配置CLKMODE [2:0]引腳,具體取決于為交換機的上游側和下游側選擇了哪種模式。有關每種模式的詳細信息,請參閱《 PES64H16G2,PES48H12G2或PES32H8G2設備用戶手冊》。當在上游端口或下游端口上使用非公共時鐘時,必須禁用擴頻時鐘。

重置(基本重置)方案

PERSTN引腳用于復位開關內部的所有邏輯,它是施密特觸發器輸入,可以從系統或上電復位電路連接到PERST#。在系統中,Tpvperi和Tperst-clk的值取決于使用該開關的機械形狀因數。例如,PCIe卡機電規范,修訂版2.0,規定了Tperst-clk = 100 μs和Tpvperl = 100 ms的最小值。

編輯:hfy

-

emi

+關注

關注

53文章

3597瀏覽量

127886 -

緩沖器

+關注

關注

6文章

1924瀏覽量

45555 -

發生器

+關注

關注

4文章

1368瀏覽量

61760 -

PCI

+關注

關注

4文章

670瀏覽量

130365 -

參考時鐘

+關注

關注

0文章

6瀏覽量

2977

發布評論請先 登錄

相關推薦

交換機與集線器的優缺點 如何監控交換機流量

PCIe交換機與路由器的區別

如何使用反射內存交換機

ISM交換機如何添加VLAN呢?

TS2PCIE412 4通道8:16多路復用器/多路分解器PCI EXPRESS交換機數據表

如何簡化PCIe 6.0交換機的設計

基于PCI Express 2.0的系統互連交換機設備系統設計

基于PCI Express 2.0的系統互連交換機設備系統設計

評論