PI仿真一直都是業(yè)內(nèi)的一個難點,也是存在很多爭議的領(lǐng)域。以上的仿真結(jié)果,就存在一個疑問:由于埋容材料的使用,在一百多兆的位置出現(xiàn)了一個反諧振點,這是埋容材料和By Pass電容共同作用形成的阻抗峰值。這個峰值的存在,就是一個設(shè)計隱患,如果在這個頻段附近存在較大的電流變化的時候,就會導(dǎo)致很大的電源噪聲。

如何處理這個反諧振點,主要有以下思路:

一、 添加相應(yīng)的板級By-Pass電容,抑制這個反諧振峰值。由于頻點在一百多兆,在這頻點起作用的電容值很小,需要的數(shù)量較多。這樣就需要使用大量的小電容,沒有達(dá)成節(jié)約分立電容數(shù)量的目的,并且有過設(shè)計嫌疑。

二、 添加封裝寄生電感和Die電容的參數(shù),準(zhǔn)確仿真整個PDN路徑的阻抗。這個方法困難的地方在于很多時候拿不到封裝和Die的參數(shù)。

三、 不理會100M以上的頻點的峰值。準(zhǔn)確添加了封裝和Die參數(shù)的全路徑PDN阻抗分析, 100M以上頻段的阻抗由于封裝電感和Die電容的影響,一般情況下都會得到很好的抑制。這也是PI工程師經(jīng)典的處理事情的方式,“鐵路工人,各管一段”,忽略不屬于我能解決的頻段。

四、 新的解決方案,取得芯片的CPM模型,然后通過對電流的分析得到準(zhǔn)確的目標(biāo)阻抗要求,避免過設(shè)計

五、 SSN仿真分析,通過分析最終的時域噪聲,來觀察噪聲分布的頻段,以及噪聲大小的變化趨勢,來輔助電源PDN設(shè)計。

時域紋波驗證

這個案例,我們把頻域PDN阻抗曲線的結(jié)果,最終反映到時域的噪聲上,圖十二是針對1.5V時域SSN仿真的結(jié)果,也能看到使用埋容材料前后的區(qū)別

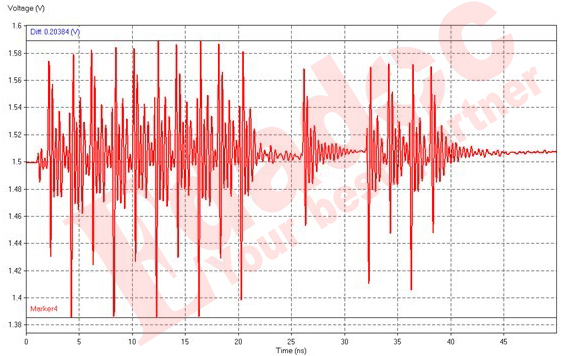

沒有使用埋容的SNN仿真結(jié)果,從波形可以測得SSN的峰峰值為0.204V

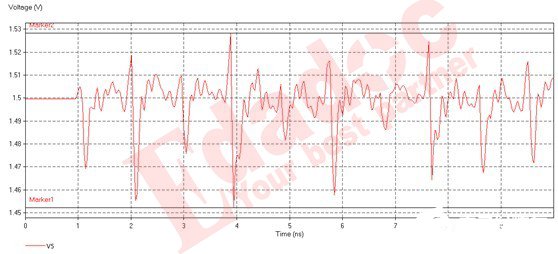

未刪除電容的SNN仿真結(jié)果,從波形可以測得SSN的峰峰值為0.076V

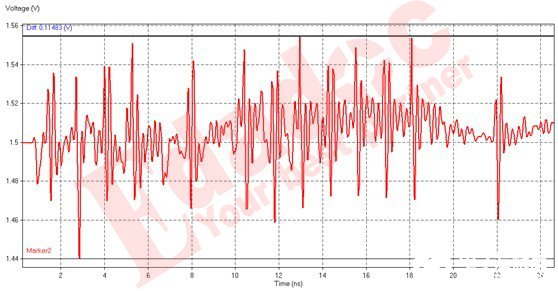

刪除70%電容的SNN仿真結(jié)果,從波形可以測得SSN的峰峰值為0.115V

圖十二 1.5V電源SSN仿真結(jié)果

從SSN仿真來看,使用埋容可以有效抑制噪聲,并且在噪聲裕量允許的范圍內(nèi),可以大幅刪除板上分立電容,節(jié)約板子的空間。

電源Noise測試驗證

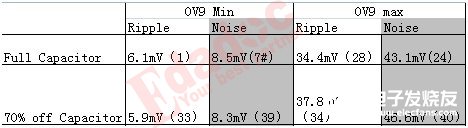

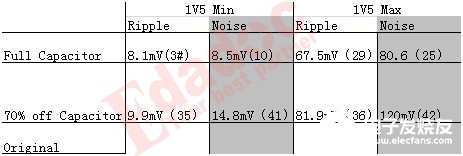

針對0.9V電源,測試結(jié)果如下表:Ripple為電源紋波測試,測試點為電源模塊附近。Noise為電源噪聲測試,測試點在主芯片附近。Min是負(fù)載較輕時的測試結(jié)果,Max為芯片全速運行,負(fù)載最重時的結(jié)果。

表一 0.9V 電源噪聲和紋波測試結(jié)果

從上表可以看出,去除70%分立電容后,板子上的電源噪聲沒有明顯增加, 因為使用埋容材料在177M附近形成的反諧振點沒有導(dǎo)致較大的噪聲。實際電源測試波形如下:

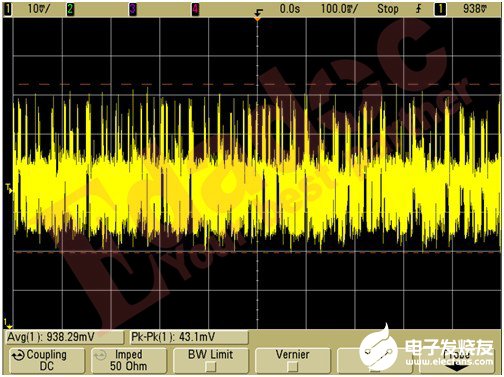

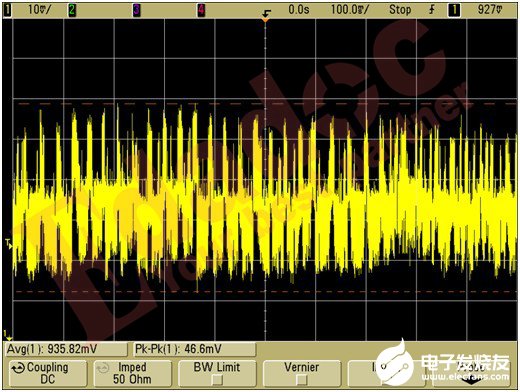

圖十三 0.9V 電源未刪除電容的噪聲測試結(jié)果

圖十四 0.9V 電源刪除70%電容的噪聲測試結(jié)果

針對1.5V的測試結(jié)果如下:

表二 1.5V 電源噪聲和紋波測試結(jié)果

從上表可以看出,去除70%分立電容后,1.5V在滿負(fù)荷工作時,噪聲變大,量值和趨勢與仿真結(jié)果類似。觀察噪聲分布的頻率,能看到實際噪聲是因為PDN阻抗曲線在低頻段整體變大引起的。實際電源測試波形如下:

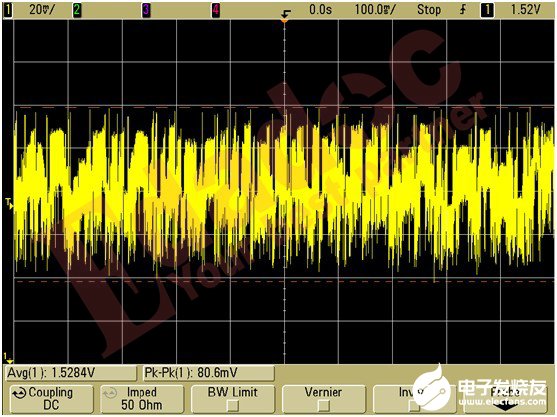

圖十五1.5V 電源未刪除電容的噪聲測試結(jié)果

圖十六 1.5V 電源刪除70%電容的噪聲測試結(jié)果

結(jié) 論

Cadence-Sigrity 仿真軟件,提供了從PDN阻抗分析到時域噪聲SSN分析的全套解決方案,可以完美的支持PI設(shè)計仿真的需要。

通過Power SI提取PDN的阻抗,然后和Target Impedance進(jìn)行對比,來衡量埋容的PCB設(shè)計帶來的影響,同時進(jìn)行電容優(yōu)化。(這時候也可以采用Cadence-Sigrity的OPI 工具來協(xié)助電容選擇和優(yōu)化,效率更高)

然后采用Cadence-Sigrity的Speed 2000來進(jìn)行SSN仿真分析,從時域角度驗證埋容的PCB設(shè)計,確保設(shè)計成功。

編輯:hfy

-

PCB設(shè)計

+關(guān)注

關(guān)注

394文章

4688瀏覽量

85636 -

諧振

+關(guān)注

關(guān)注

5文章

372瀏覽量

39587 -

PDN

+關(guān)注

關(guān)注

0文章

83瀏覽量

22706

發(fā)布評論請先 登錄

相關(guān)推薦

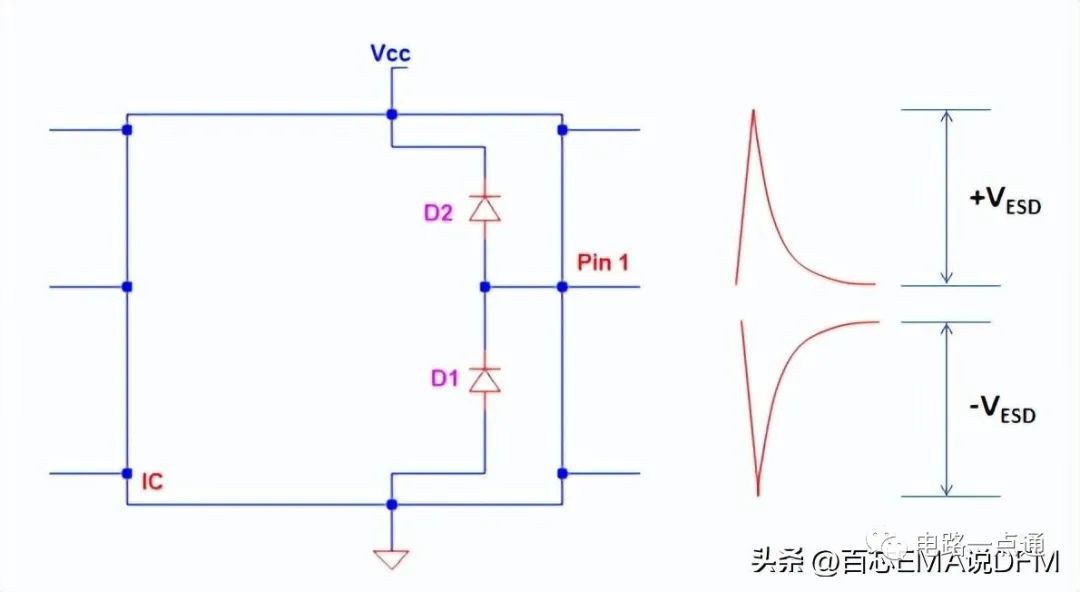

電路設(shè)計和PCB設(shè)計中如何防止ESD損壞設(shè)備

降低PCB設(shè)計風(fēng)險的三點技巧

降低pcb設(shè)計風(fēng)險的三點技巧

PCB設(shè)計如何一版通過?這個工具徹底幫你解決

【8.25直播】PCB設(shè)計電源處理及整體PCB DFM檢測

pcb抄板如何處理掃描圖片_pcb抄板處理掃描圖片的步驟教程詳解

PCB設(shè)計如何處理這個反諧振點

PCB設(shè)計如何處理這個反諧振點

評論