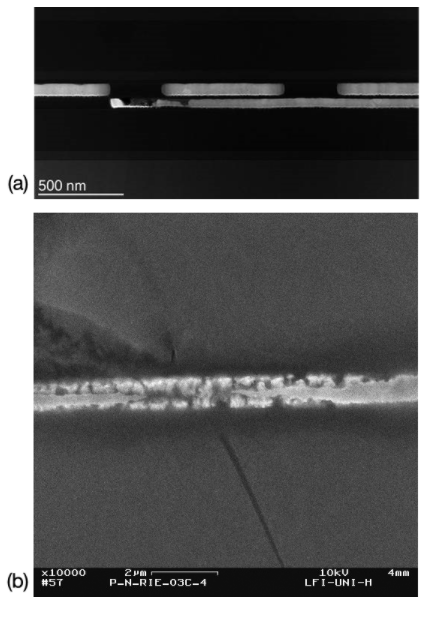

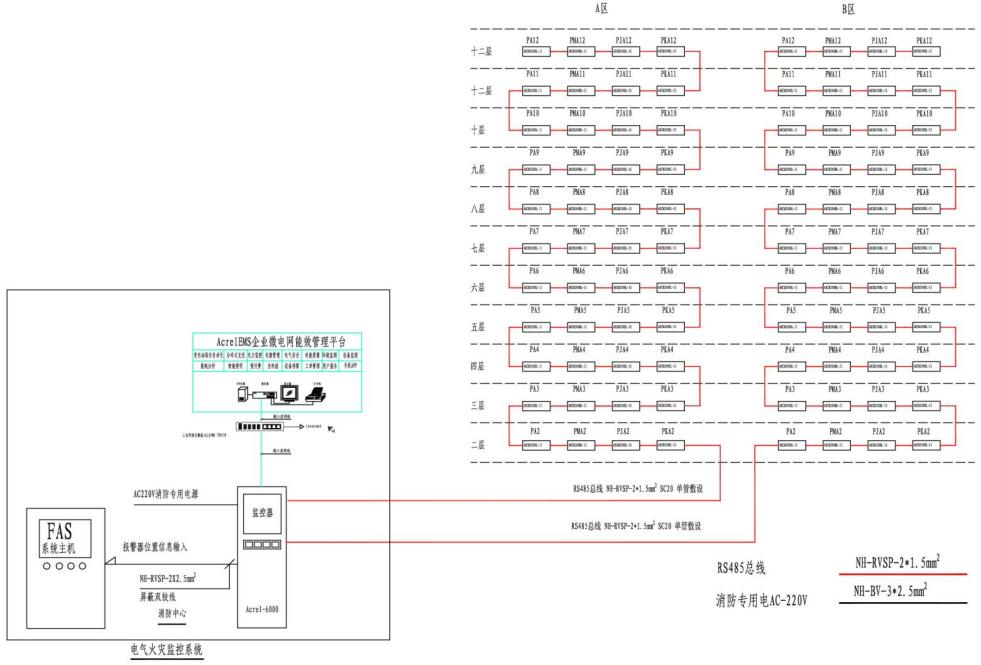

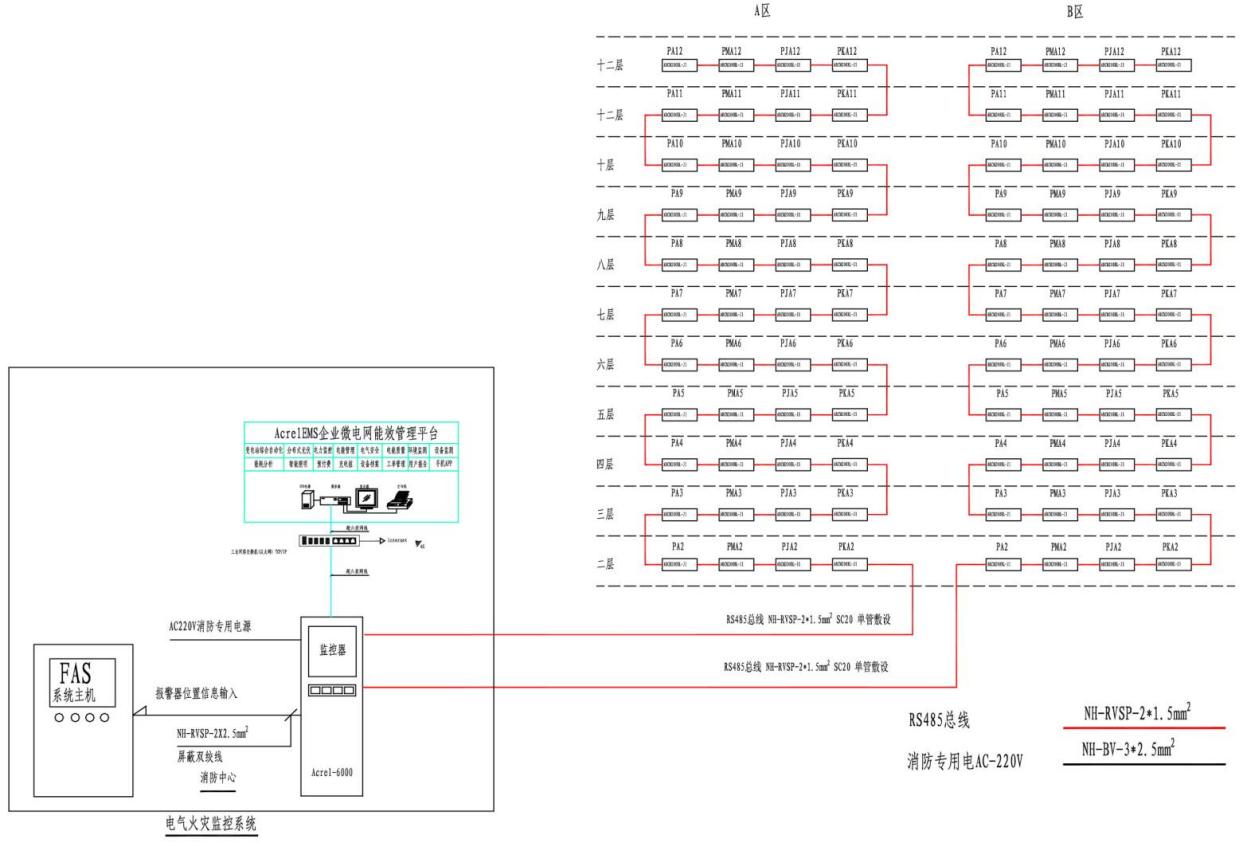

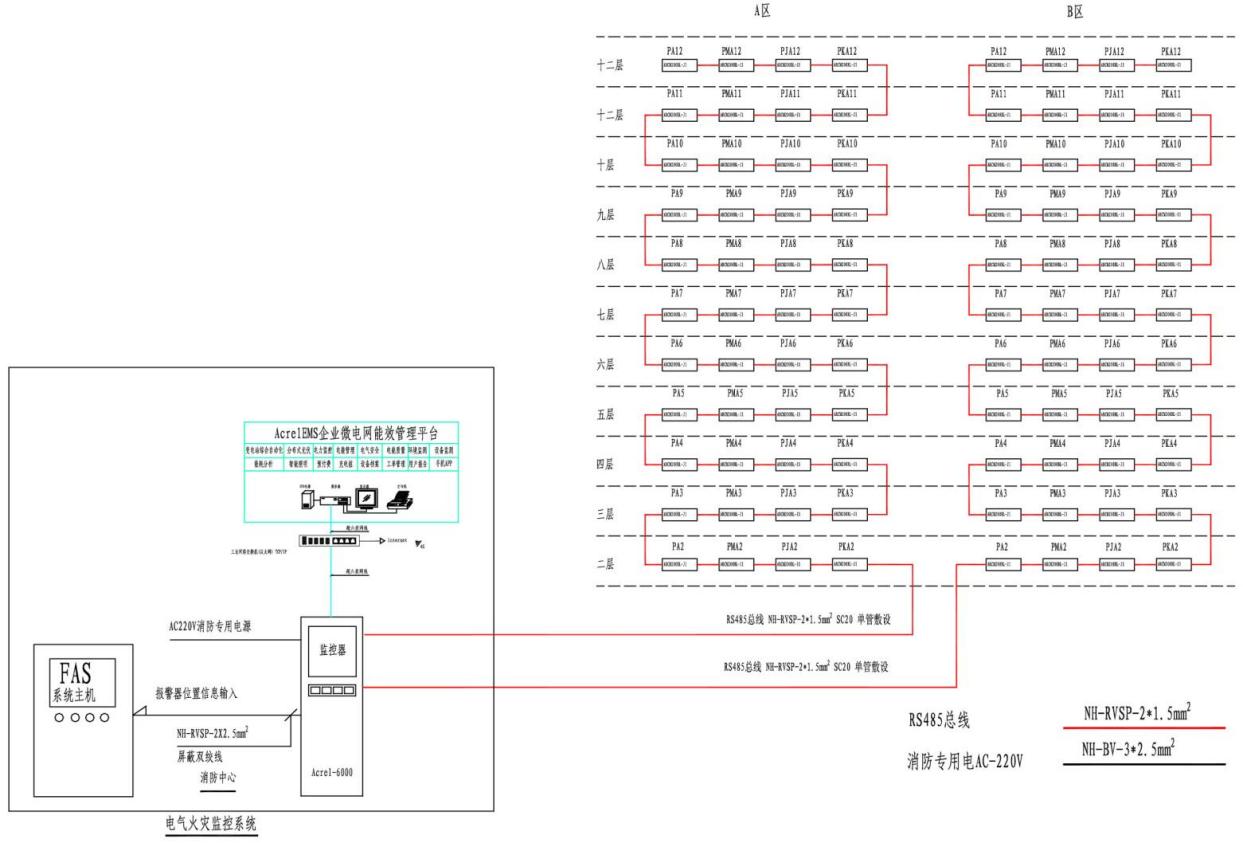

一項創新的測量技術正在為電遷移提供新的見解,電遷移是微電路過早死亡的主要原因。直到最近,這種現象會導致致命的短路并在形成集成電路(IC)晶體管之間電連接的亞微米金屬走線內斷開連接,只能通過使用破壞性的加速老化過程來導致設備故障來研究這種現象。然后將其切開并對其互連進行目視檢查(圖1)。

這項新技術有時被稱為功率譜密度特征分析,它可以分析流經設備的電流中的細微變化,從而為研究人員提供有關電遷移潛在機理及其??預防的新見解。這些見解已經開始幫助IC制造商設計不易過早出現故障的芯片。

圖1a)由于電遷移,兩層銅互連的橫向SEM圖像,下部線條上有空隙。圖片由imec提供。b)由銅互連中的電遷移引起的故障的SEM圖像。圖片由Wikimedia用戶Patrick-EmilZ?rner提供。

深度監聽還可用于快速識別剛制造出來的IC,而這些IC在實際發生故障之前會遭受電遷移的困擾。這項新功能為芯片制造商提供了一種比傳統老化測試更快,更具成本效益的替代方法,傳統老化測試通過在高溫下運行多個小時甚至幾天來加速新制造IC的缺陷的出現。

電遷移:一個日益嚴重的問題

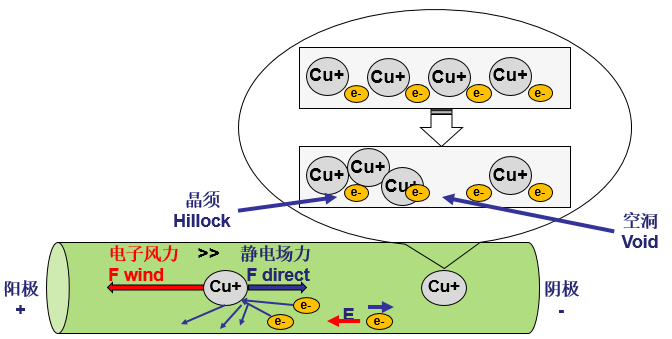

電遷移是由于導電電子與擴散金屬原子1之間的動量轉移而在導體內發生的質量傳輸。遷移水平與許多因素有關,包括導體內的電流和環境溫度。

曾經是100多年前科學家最初觀察到的一種實驗室好奇心2因此,這種現象已成為半導體工業中越來越具有挑戰性的問題。在集成電路的早期,人們對電遷移的了解還不夠,甚至在短短的三周運行后就導致一些早期的商用芯片出現故障。那時,制造商通過在芯片頂部生長二氧化硅(即玻璃)薄層,在玻璃頂部沉積一薄層鋁,然后對其進行蝕刻以形成電路,從而將IC上的晶體管連接起來。對發生故障的芯片的分析表明,在正確的條件下,鋁原子會離開其原始位置,從而在電路走線之間形成空隙或積聚在其他走線上,從而導致開路和短路,從而導致器件發生故障。

對這些故障的進一步研究表明,電遷移活動隨溫度和電流密度的增加而增加,并受互連跡線的幾何形狀的影響。這也導致了黑色的方程式,發展3用于預測IC的壽命公式,和其他工具,允許制造商模式的故障模式,并采用設計實踐取得了芯片的金屬互連電遷移更容易。

根據他們所學到的知識,該行業開發了一些簡單的測試,可以通過使它們經受加速的老化過程來在發貨之前對設備進行過早故障篩查,我們將在下一部分中對其進行詳細介紹。由于這些發展,電子工業能夠制造出使用壽命長達數十年的復雜半導體器件。

盡管如此,電遷移并沒有被擊敗,只是受到了良好的工程實踐的控制。隨著不斷縮小的工藝幾何尺寸開始接近納米區域,IC互連層內的電流密度開始上升,而導電跡線之間的距離縮小,從而為金屬遷移創造了更加有利的條件。另外,越來越多地使用銅作為互連材料也增加了挑戰。盡管銅的優異電性能使設計人員可以制造更小,更快的芯片,但它也更容易受到導致金屬原子從IC內指定位置漂移的作用力的影響。

結果,制造商發現自己試圖用一些過時的工具來應對新的挑戰。在過去的三十多年中,用于電遷移的標準可靠性測試一直是通過在升高的溫度(> 150°C)和電流密度(j> 1MA / cm2)下運行設備直至其失效來加速老化過程的過程。然后可以使用布萊克方程將芯片在壓力條件下失效所需的時間轉換為正常條件下的預期壽命。較不嚴重的加速老化形式(通常稱為“老化”)用于篩選在高可靠性應用中使用的IC,以查找導致在裝運前造成嬰兒死亡的缺陷。

這些加速測試為制造商提供了寶貴的指導,但它們也有許多缺點和盲點。例如,它們的結果有些不可靠,因為它們使用升高的電流和溫度,這可能會導致芯片中發生其他類型的過程,而不是正常情況下所經歷的過程。這些測試還需要大量時間,并且會對芯片造成破壞。盡管可以對發生故障的IC進行物理檢查,以了解發生問題的各種線索(見圖1),但再也無法進行可能產生其他類型有價值信息的有源電氣測試。此外,越來越多地使用會阻礙電遷移的新材料(例如鈷),可能需要對設備進行幾個月的測試,甚至還要在更高的溫度和電流密度下進行測試。

一種新方法

作為KU Leuven的一名學生,與imec合作為我的博士進行半導體研究,很明顯,20世紀測試技術的局限性已成為生產21世紀IC的障礙。從那時起,我和我的同事就開始探索其他測試和分析技術,這些技術可能會提供有關電遷移的新見解。在考慮了幾種選擇之后,我們開始研究由其輸出電流波動產生的IC的電子簽名,即使在穩定狀態下運行,這些波動也會出現。

聆聽芯片內的瀑布

當直流電流流過金屬時,由于電子散射,會出現較小的電流波動。這些微小的波動可以作為時間的函數進行測量,并且可以使用傅立葉變換在頻域中表示。將該波動描述為頻率與幅度的函數的變換,可用于導出波動的功率譜密度(PSD)。

由于尚未完全理解的原因,流經金屬的電流似乎會產生PSD簽名,該簽名在低頻范圍內遵循1 / f頻譜。這種噪聲,也稱為“粉紅色噪聲”,通常發生在自然現象中,例如瀑布的轟鳴聲。遵循1 / f和1 / f2頻譜的噪聲稱為低頻噪聲,因為與這種噪聲相比,低頻聽起來要比高頻聽起來更大(與白噪聲相反,白噪聲中所有頻率都是相同的)。

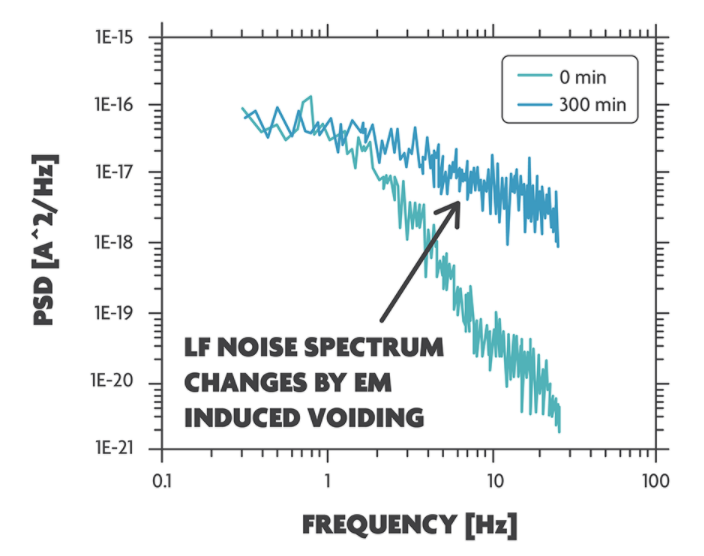

測量芯片中的低頻噪聲很有趣,因為當發生諸如電遷移的現象時,頻率似乎會突然改變(圖2)。

圖2經過僅300分鐘的熱和電應力(旨在刺激電遷移),此處測試的設備的低頻噪聲特征發生了明顯變化。這些變化是由于電遷移在金屬通道中產生新的空隙時發生的電流變化而引起的。

新技術產生新見解

盡管imec研究人員已經在相對較短的時間內使用了這項新技術,但他們已經得出了許多令人驚訝的見解,可將其應用于商業半導體設計和制造實踐。例如,他們發現,隨著金屬通道的寬度變小,刺激電遷移所需的活化能閾值也降低,并且當寬度降至30nm以下時顯著降低。在對銅互連的研究中,研究人員了解到,這在很大程度上是由于晶粒更緊密的金屬結構中多晶的百分比不斷增加,從而為電遷移的進行提供了更多的擴散位置。

到目前為止,IC的設計規則一直基于以下假設:由相同材料制成的所有線路后端(BEOL)互連都具有單一激活能量。由于有了這一新見識,未來的設計規則可能將基于針對不同路徑寬度的較低的不同能量。

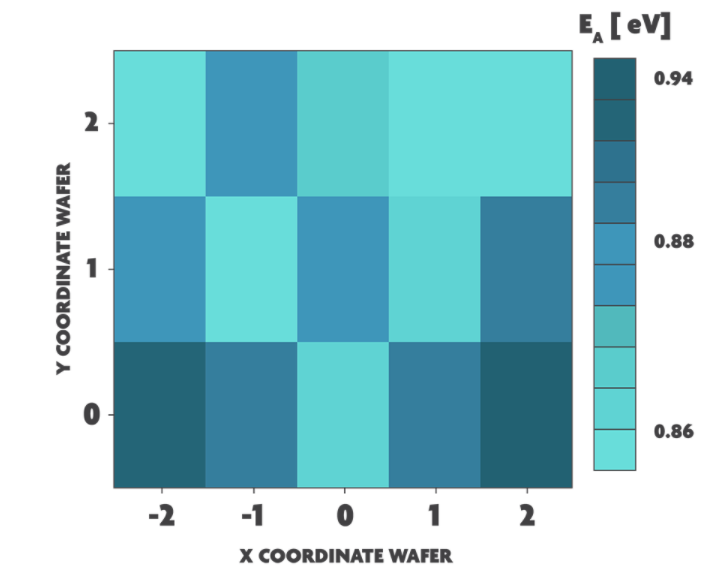

研究人員還了解到,可以在晶圓上的不同芯片之間觀察到PSD簽名的變化。可以預計,在不久的將來,制造商將能夠在生產測試期間使用PSD簽名分析來創建晶圓圖,以顯示每個芯片的預期壽命-這是標準方法無法實現的。

圖3晶片圖顯示了晶片上每個芯片的激活能量(通過測量低頻噪聲定義)的變化。圖片由imec提供。

使用新測試的第三項研究領域是測試釕的電遷移可靠性,該材料被認為是BEOL中銅通道的替代材料。由于釕具有抗電遷移的能力,因此常規測試將花費很長時間,并且需要更高的溫度和電流密度。相反,PSD分析可以相當快地確定新材料的活化能。這項研究還產生了許多有關不同類型的勢壘如何有效減少或消除電遷移的新信息。例如,釕襯里似乎對銅互連的耐電遷移性具有積極作用,向籽晶層中添加錳也是如此。

除了可以在故障發生之前進行預測外,該技術是非破壞性的,并且比傳統測試花費的時間要少得多。此外,測試產生的數據可提供對電遷移的性質和發生情況的更深入的了解。由于PSD簽名分析是在設備的額定溫度范圍內進行的,因此觀察到的現象也很有可能與實際使用中的芯片所產生的現象相同。

準備服務

PSD簽名分析已證明其作為半導體研究工具的價值,并有望成為制造商的寶貴工具。Imec的合作伙伴公司和大學研究小組已經在探索如何使用它來更深入地了解電遷移的潛在機制,這些機制可用來更好地防止新材料和現有材料的故障。

對于芯片制造商而言,該方法對于研究和生產都非常重要。在生產中,它通過對單個芯片的電遷移電阻提供更深的基礎見解和預測,對現有方法進行了補充。例如,上一節中討論的晶片圖可用于查明晶片中每個器件中電遷移活化能和缺陷濃度的變化。這將有可能根據更高的活化能和/或更低的缺陷集中度,根據成品的可靠性對成品進行分類,而不是傳統老化測試所提供的簡單合格測試。使用壽命更長的設備可以針對航空航天,醫療或汽車系統等關鍵應用以高價出售。

Sofie Beyne是imec和KU Leuven的博士學位學生,研究作為REMO團隊一部分的納米互連中的電遷移。

編輯:hfy

-

集成電路

+關注

關注

5391文章

11593瀏覽量

362545 -

測量技術

+關注

關注

1文章

192瀏覽量

24741 -

晶體管

+關注

關注

77文章

9723瀏覽量

138603 -

微電路

+關注

關注

1文章

19瀏覽量

9557

發布評論請先 登錄

相關推薦

HarmonyOS Next 應用元服務開發-應用接續動態配置遷移保持遷移連續性

晶振過驅的影響及其預防措施:電阻與電容在晶振電路中的應用

變壓器預防性試驗項目及意義

淺談醫院電氣火災的起因與預防

淺談變電站運維管理中習慣性違章預防措施研究

淺談建筑電氣設計中的火災隱患及其對策方案

淺談電氣火災的分析和預防

淺談醫院電氣火災的起因與預防

電遷移導致半導體失效的機理探討

淺談因電遷移引發的半導體失效

淺談有關電遷移潛在機理及其??預防的新見解

淺談有關電遷移潛在機理及其??預防的新見解

評論