1、 層疊設計與同層串擾

很多時候,串擾超標的根源就來自于層疊設計。也就是我們第一篇文章說的設計上先天不足,后面糾正起來會比較困難。

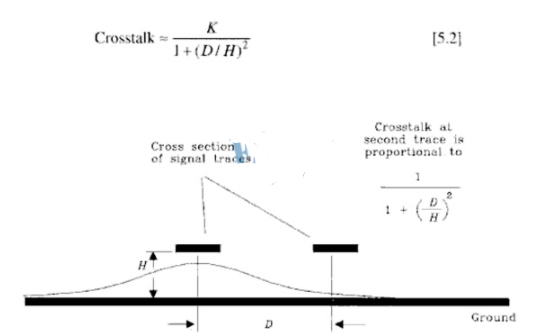

講到層疊對串擾的影響,這里有另一張圖片,和上文提到的參考平面的圖片一脈相承。我們能看到,層間距離H是影響串擾的關鍵因素。當D=3H的時候,不考慮K的話,串擾大約在10%左右。這也是所謂3H原則的由來吧,我們在了解串擾之后,就需要把3W原則改為3H原則了。

從上圖還可以留意到,如果要減小串擾的話,可以減小H或者增大D。只不過H太小,為了控制阻抗,線寬也會相應變小,增大加工難度,或者增加了導體損耗。而增大D,當然會受到布線空間的約束。所以我們一直提倡的,PCB設計是權衡的藝術,而權衡的技巧,就來自于對理論的深入理解,以及適當的工程量化能力。

2、層疊設計與層間串擾

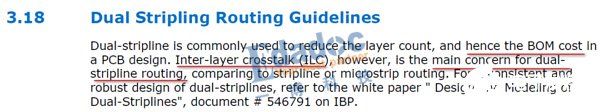

提到權衡,就必須講一下現在各種規則里面提的比較多的雙帶線,也就是Dualstripline結構。各大公司對Dualstripline的設計都會制定非常詳細的設計規則。

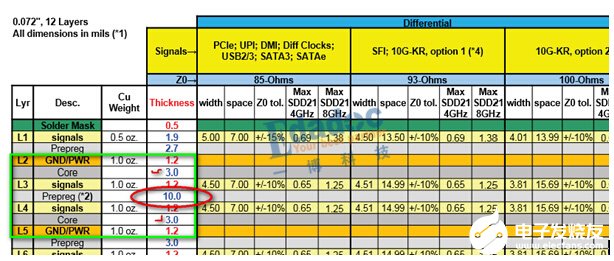

以Intel的Purley平臺規則為例,為了降低成本,雙帶線結構經常被采用,要注意層間串擾。推薦的層疊可以看到,L2~L5之間構成雙帶線結構,L3和L4之間的距離是10mil,而L2到L3以及L4到L5是3mil,從層疊的源頭來控制層間串擾。

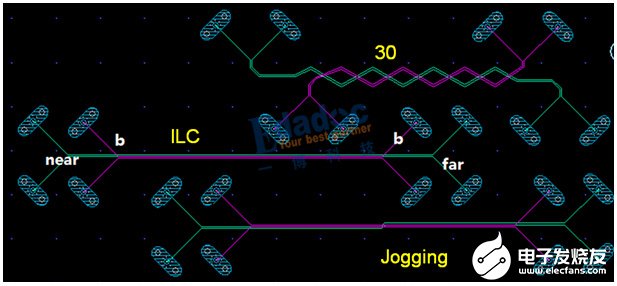

具體的設計建議中,還提出用30度夾角來規避雙帶線結構層間串擾的方法。以及使用Jogging的方式來平衡串擾。下圖就是我們針對這些不同的走線方式做的測試板。

一直關注高速先生的朋友,都知道我們經常會做一些測試板來驗證各種走線細節的差異。我們通過驗證分析,比較有把握的結論都已經陸續在研討會Paper以及高速先生的文章中進行分享。還有一些結論,要么是我們也還有困惑,要么就是結論還不夠充分,我們還會繼續深入研究。雙帶線的30度夾角以及Jogging走線就屬于我們認為還不夠充分,也還有些疑惑的Item。所以這次就不公開發表結論了

感興趣的朋友,或者想和高速先生一起來分析的朋友,可以在關注高速先生微信公眾號(搜索:高速先生),并在后臺留下具體的聯系方式(姓名、公司、Email、電話等信息),我們可以把階段性的研究成果單獨發給你們,大家一起來看看現在的結論有沒有問題,下一步該往哪個方向研究。

Anyway,雙帶線的層間串擾是業內都關心的問題,這樣的結構,層疊設計非常重要,從一開始就要做好規劃。

編輯:hfy

-

串擾

+關注

關注

4文章

189瀏覽量

26949 -

層疊設計

+關注

關注

0文章

12瀏覽量

7673

發布評論請先 登錄

相關推薦

PCB設計與串擾-真實世界的串擾(上)

示波器通道間串擾的影響

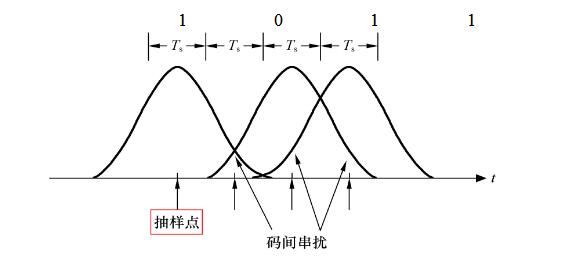

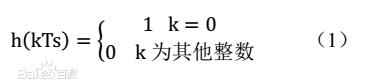

如何消除碼間串擾_怎么避免碼間串擾

淺談層疊設計、同層串擾、層間串擾

淺談層疊設計、同層串擾、層間串擾

評論