隨著航天航空電子設備中越來越多地使用低壓,高電流負載(例如FPGA),工程師越來越需要設計開關模式調節器來生成電源軌。之前,我描述了降壓拓撲如何執行dc-dc轉換,以及從供應商選擇空間級設備時要考慮的標準。大多數合格部件都集成了開關和低端FET,但需要一個外部電感器以及輸入和輸出電容器。這些無源器件的選擇非常重要,因為它們決定了轉換的質量,即輸入和輸出紋波,負載調節以及對單事件效應(SEE)的響應。

電源設計從其本質上講就充滿了折衷和折衷,例如成本,尺寸,性能和可靠性。但是,還存在優化和減小儲能無源元件的尺寸和質量的范圍。

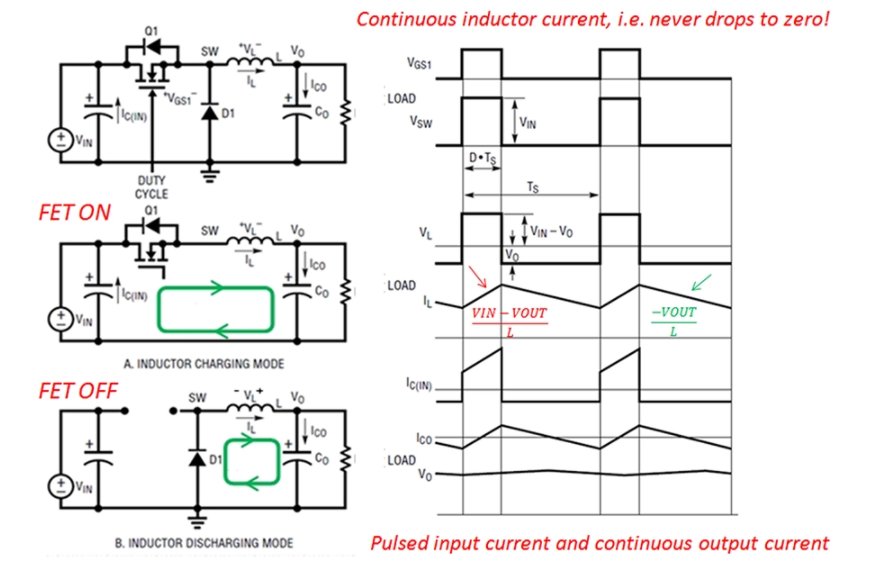

開關DC-DC通過控制通態和關態的占空比,基于流入和流出DC-DC的能量來調節輸出電壓。當開關導通時,能量從輸入源流入轉換器,在降壓的情況下,其中一些以磁能(0.5 *LI2)的形式存儲在電感器中,而另一些則直接傳遞到輸出中(正向)拓撲)。類似地,在關閉間隔期間,能量從轉換器傳遞到負載。為了降壓,它來自電感器,該電感器先前在FET導通時存儲在該電感器中。

在導通時間內添加到電感的能量始終等于開關斷開時傳遞到負載的能量,即,電感在每個周期結束時的電流和能量與開始時完全相同。穩態的定義!

圖1該圖顯示了降壓調節器的開關周期。

例如,假設開關頻率為500 kHz,輸入為+ 5.5V,負載電壓為+ 0.95V,負載電流為18 A,轉換效率為90%,則得到的輸入和輸出功率為19和17.1W。在每個開關周期內汲取的源能量為38 μJ,FET關斷時的能量輸出為34.2 μJ。在500 kHz的頻率下,調節器處理的總能量為17.1 J / s或按定義為17.1W。

當我們向電感器添加能量時,流經電感器的電流會線性上升。當我們去除能量時,電流會下降,從而導致觀察到交流電流紋波。以類似的方式,當我們向電容器添加能量時,電容器兩端的電壓線性上升。當我們除去能量時,電壓下降,從而導致觀察到交流電壓紋波。開關動作不斷地增加和消除能量,從而產生流經電感器的電流紋波和電容器兩端的電壓紋波。對于這兩者,都有相對于其直流電平的最大可容忍交流變化量的準則。

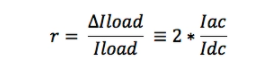

對于降壓穩壓器,當開關FET導通時,電感器將輸入能量存儲在其磁場中,而當高端晶體管關斷時,電感器將其傳遞到負載。電感值的選擇基于要傳遞給負載的電流紋波的大小,由幾何比r定義:

其中Iload是平均電感器電流,ΔIload是電流擺幅,Iac和Idc分別是電感器電流的ac和dc值。亨利中與r相關的最終電感可以通過以下公式計算:

其中fsw是赫茲的開關頻率。

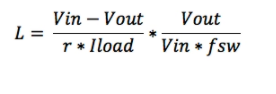

例如,要在18 A電流下產生+ 0.95V電壓軌,下表列出了以安培為單位的絕對峰峰值電感電流紋波和Iload的百分比,以及作為r的函數得出的電感:

表1電感紋波和電感的計算

電感的值與負載電流和開關頻率成反比,而其物理尺寸和質量與Iload成正比。

完全集成的空間級降壓穩壓器可提供總體上較小的外形尺寸,并且易于設計,同時還必須添加外部磁和無源元件,從而使設計人員可以更好地控制電流紋波的電平,從而控制電壓變化傳遞給負載。

圖2比較完全集成和非集成的空間級開關穩壓器。

大電感會產生較小的電流紋波,從而降低負載中的電壓波動。較大的電感(由于其自然會抵抗電流變化的趨勢)會減慢調節器的瞬態響應,并由于較大的固有dc電阻而增加功率損耗。較小的電感可提高調節速度,但會增加輸出紋波量,并有將電感驅動至飽和的風險。重要的是,不要超過電感的均方根電流和飽和電流額定值,后者要大于計算出的峰值。磁體的物理尺寸必須與其能量處理能力相匹配,并且需要更大的磁芯來處理更高的功率。另請檢查電感的容差,對于某些供應商,其容差可能會高達30%,

電感器電流紋波表現為輸出電壓的變化,輸出電容的功能之一是減少負載看到的紋波量。電容器ESR和ESL是確定與電感器電流相關的輸出電壓紋波的重要參數。

電容器自然可以抵抗交流電的變化。電壓,一旦充電,就有保持電壓的趨勢,尤其是在直流電之上存在紋波的情況下。如果電容器尺寸適當,將太慢而無法跟上由于紋波引起的電壓波動,因此它們會被濾除。

當FET關斷時,輸入與輸出斷開,但是,負載始終需要連續的能量流。在這段時間內,輸出電容還必須存儲足夠的電荷以為負載提供輸出:當開關斷開時,電感電流在為負載供電時會減小,而輸出電容則可以緩沖這種電流變化,因此負載的電壓幾乎恒定。

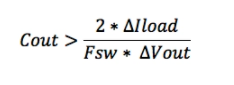

輸出電容還決定了調節器如何響應負載電流的大變化。它的大小必須適當以在DC-DC無法且直到DC-DC的反饋控制回路能夠響應之前提供負載。下面的公式指定了完成此操作所需的最小輸出電容:

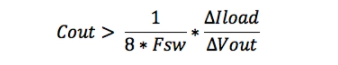

而以下公式可計算滿足目標輸出電壓紋波要求的最小輸出電容:

由電感器和輸出電容形成的LC濾波器去除了開關波形的ac分量,以輸出平均(dc)電壓。對于降壓穩壓器,輸出電容通過以負載電壓為中心的紋波反復充電和放電。圖1中的跡線Ico繪制了流入輸出電容的連續電流。

通常,并聯使用各種不同的電容器,以最小化等效串聯電阻(ESR)和等效串聯電感(ESL)對輸出紋波和均流的影響,以確保可靠的工作。根據零件的額定紋波電流,工作電壓和寄生蟲來選擇零件。

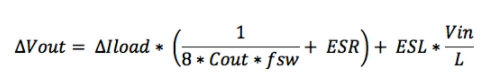

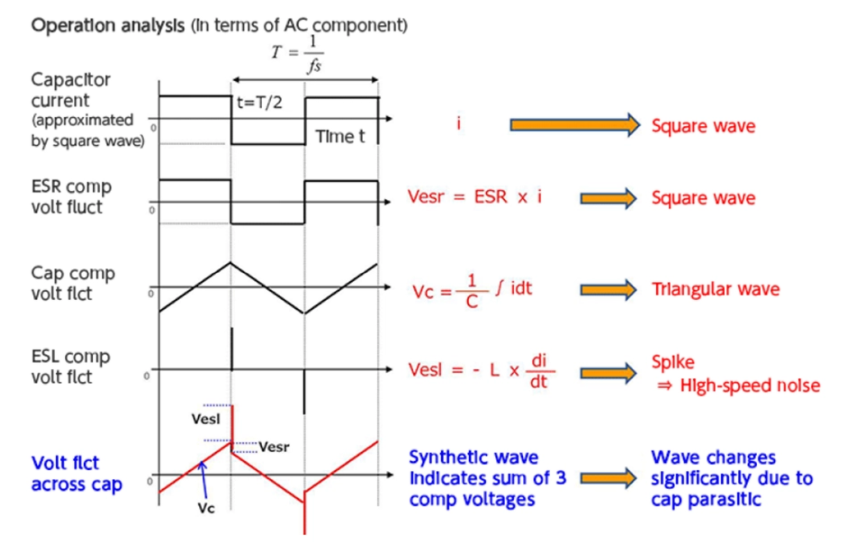

圖3繪制了由ESR,ESL和電容產生的紋波電壓貢獻。ESR的貢獻是電阻*電流,電容分量是電流和時間的積分,產生三角波,ESL分量可以表示為導數,在每個開關瞬間都會產生瞬時尖峰,從而產生高頻脈沖-像噪音。電容器兩端的總電壓波動包括以下三個成分的總和:

在輸出端看到的峰峰值電壓紋波與電容和開關頻率成反比,但與負載電流,ESR和ESL成正比。

圖3此操作分析顯示了ESR,ESL和電容對紋波電壓的影響。

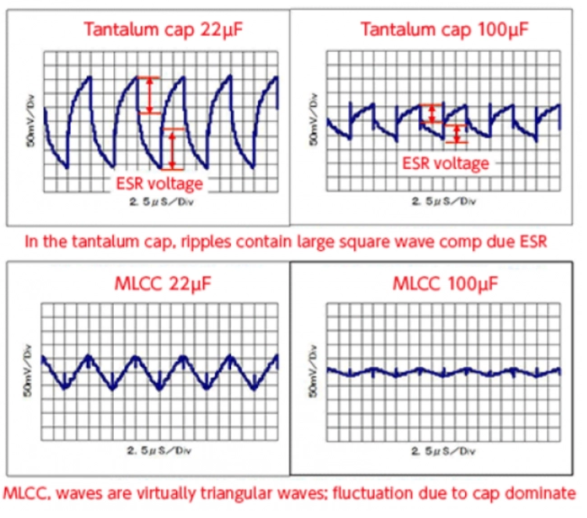

圖4比較了從鉭電容和多層陶瓷電容器(MLCC)測得的紋波電壓。MLCC具有較低的固有ESR,并且增加電容量可進一步降低紋波。

圖4這些圖顯示了電容器類型和電容對紋波電壓的影響。

輸入電容可將在DC-DC開關處看到的源紋波電壓降低到大容量電容器可以處理的水平,而不會影響大容量電容器的ESR耗散。對于降壓穩壓器,當FET導通并導通時,其輸入電流的ac部分由電容提供。當高端開關斷開時,輸入電容充電,圖1中的跡線Ic(IN)繪制出具有高di / dt和峰峰值幅度的不連續梯形波形。該源無法產生如此迅速變化的脈動電流。

大容量輸入電容用于最小化電源電壓偏差,以確保負載瞬變期間的穩定輸出。電容越高,擾動越小,它與負載電流的變化成正比。

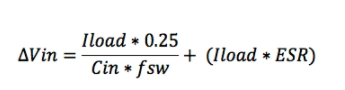

確定輸入電容量的一個很好的起點是指定峰峰值電壓紋波的目標電平,該目標電平與電容和開關頻率成反比,但與負載電流和ESR成正比:

對于降壓穩壓器,輸入電容器的均方根電流要比輸出電容器中的均方根電流高得多,前者是由其應力要求決定的,而在輸出端,僅是最大允許負載紋波決定了電容的大小。電容器的最大允許均方根電流可以根據其最大功耗(由其外殼尺寸,ESR和可承受的溫升得出)來計算。

通常,并聯使用各種不同的電容器以最小化ESR和ESL對輸入紋波以及電流共享的貢獻,以確保可靠的工作。根據零件的額定紋波電流,工作電壓,自發熱,ESR和ESL選擇零件,并使用多層陶瓷,因為它們的寄生系數低。因此,觀察到的紋波幾乎完全歸因于實際電容,因此必須注意熱和直流偏置對電容器值的影響。對溫度不太敏感的電介質通常用于最小化電容的變化。溫度越高,包括壽命在內的可靠性越低。

設計降壓穩壓器時,需要權衡很多:較高的開關頻率可降低輸入和輸出電容器中的紋波電壓電平,并減少DC-DC所需的電容量。但是,減小后者會增加電壓紋波的幅度,而以更快的速率進行切換則會增加交流損耗,從而影響效率。還存在優化的機會,例如,對于給定的電壓紋波目標,如果增加開關頻率以使用較小的能量存儲組件,則可以減小電容。

較小的電感具有較低的DCR,可改善瞬態響應,并且對于給定的瞬態性能,所需的輸出電容也較小。較大的電感導致較低的紋波電流,因此等效輸出紋波所需的電容較小。

如果超過電感的飽和電流,其電感將下降,從而增加紋波電流:電感下降30%將使紋波電流增加40%以上,并使磁芯飽和。屏蔽電感器可降低EMI和潛在干擾,但由于制造成本增加,價格稍貴。屏蔽會降低飽和電流,從而降低最大允許均方根電流。Lsat也隨溫度而變化!

直到下個月,第一個告訴我0603和0805尺寸MLCC的最大功率消耗的人將贏得“火箭科學家世界巡回賽T恤”課程。恭喜來自加拿大多倫多的戴夫(Dave),第一個回答我上一篇文章中的謎語的人。

Rajan Bedi博士是Spacechips的首席執行官和創始人,該公司設計和制造了一系列先進的L至Ku頻段,超高通量板載處理器和應答器,用于電信,地球觀測,導航,互聯網和M2M / IoT衛星。

編輯:hfy

-

電容器

+關注

關注

64文章

6222瀏覽量

99633 -

電感器

+關注

關注

20文章

2330瀏覽量

70535 -

DC-DC

+關注

關注

30文章

1948瀏覽量

81661 -

降壓穩壓器

+關注

關注

2文章

324瀏覽量

29190 -

無源器件

+關注

關注

5文章

194瀏覽量

23569

發布評論請先 登錄

相關推薦

空間級開關穩壓器選擇無源器件的技巧分享

空間級開關穩壓器選擇無源器件的技巧分享

評論