關于DDR的設計,經歷過無數項目歷練的攻城獅們,肯定是很得心應手的。對于信號質量方面的改善,相信大家應該已經有自己的獨門技巧了。同組同層,容性負載補償,加上拉電阻等等,總有一款適合你的DDR。但是對于時序方面的控制,理論上只有一個辦法——繞等長,速率越高的DDR,等長控制越嚴格,從±100mil,到±50mil,甚至±10mil。

本來我們的layout工程師也是在這樣一條路上穩步前進。但是最近有個DDR4的項目,繞好了等長,如下圖所示,一切都安排的明明白白之后,給SI工程師仿真,只等仿真結果一出來就gerber out,根本不用懷疑,信號質量肯定妥妥的,沒問題。

結果,SI工程師沒有同意投板,卻提出了不合常理的時序要求,如下圖所示:

等長要求CS,CKE,ODT這些信號比其余CMD信號每段長120mil,按照這樣來算的話,到U1這個位置,長度差就到了600mil。這和設計指導不一樣。

瞬間感覺自己很委屈,這樣的等長到時候地址控制線之間的延時會相差100ps左右,這樣時序的margin就會變小,甚至可能跑不到要求的2400Mbps,于是硬氣的提出了自己的質疑。

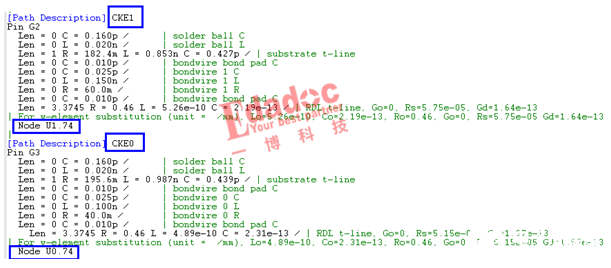

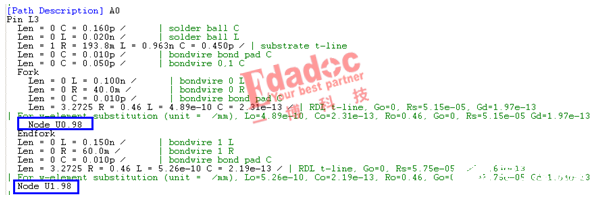

SI工程師也知道這種情況下,應該和設計人員普及一下關于時序方面的知識,不然后續遇到類似的DDR,不做仿真的話,可能會需要降頻運行。于是將U1的仿真結果給設計人員看,藍色的是CS,ODT,CKE等信號,綠色是其他的CMD信號,從時間上來看,藍色的比綠色的信號快90ps左右。

這種情況的原因不是因為設計人員的誤操作,或者不同層的時序不一致,也不是像上次文章中提到的層疊中的DK設置不一樣,而是因為DDR顆粒的選型導致的,如下面圖片所示:

這款SDRAM的CS,CKE,ODT為單DIE結構,但是其他的信號卻是雙DIE結構,在封裝中做T型拓撲,這樣意味著雙DIE的信號的容性更大一些,那么相應的上升沿會更緩一些,這個是比較好的影響,這樣的話,信號質量會比較好,從圖中的結果也可以看出來,綠色信號的振鈴比較小。另一個影響是容性更大,意味著時延會更慢一些,所以相同等長的情況下,由于顆粒內部拓撲的影響,導致CMD信號會傳輸的更慢一些,體現在仿真結果中,自然是雙DIE信號和單DIE信號會有不一樣的上升沿和一定的延時差。

layout工程師恍然大悟,這是因為顆粒內部的結構和常規設計不一樣導致,自然不能沿用常規的設計指導,以后遇到這種雙DIE的DDR還是需要仿真之后再調整等長,不然可能會出問題。于是很愉快的按照上面的時序意見修改了版本,結果如下,后期客戶反饋,DDR2400跑的飛起,一版成功。

編輯:hfy

-

SDRAM

+關注

關注

7文章

428瀏覽量

55262 -

DDR

+關注

關注

11文章

712瀏覽量

65387 -

Layout

+關注

關注

14文章

405瀏覽量

61838

發布評論請先 登錄

相關推薦

關于ddr3等長控制的8個問題

PCB設計中DDR布線要求及繞等長要求

cc2541一個主機能一個一個的連接從機?

關于DDR4的繞等長,您想知道的這本書上都有

關于Altium Designer使用等長布線問題

DDR怎么學習,從仿真開始

【驅動】一種中斷接收的不等長不規則uart數據機制

關于一個一個等時不等長的DDR設計

關于一個一個等時不等長的DDR設計

評論