11月9日,第十八屆中國半導體封裝測試技術與市場年會在甘肅天水舉行,中國半導體行業(yè)協(xié)會副理事長、長電科技CEO鄭力以《高精密芯片封測技術扛起后摩爾時代產(chǎn)業(yè)發(fā)展大旗》為主題發(fā)表了演講。

鄭力表示,后摩爾定律時代封裝的技術,尤其是高精密封裝技術,在今后的半導體產(chǎn)業(yè)發(fā)展中會越來越重要。在未來,封測技術和封測企業(yè)的發(fā)展與整個集成電路產(chǎn)業(yè)生態(tài)圈的發(fā)展將會是一脈相承、相輔相成的。

從應用端折射的未來

鄭力指出,封測行業(yè)是整個集成電路產(chǎn)業(yè)中,與應用市場聯(lián)系最緊密的一個環(huán)節(jié)。集成電路從一粒沙子經(jīng)過成千上百道的工序,最后封裝和測試完過后才能交付到應用場景去生產(chǎn)。芯片到了應用場景以后,出現(xiàn)最多的問題往往不是質(zhì)量問題,而是后道緊密相關的封裝和測試,所以要看封測產(chǎn)業(yè)未來的發(fā)展,首先應該從應用的角度再來觀察。

近年來,新興應用中被提及較多的就是5G和人工智能。但鄭力認為,從真正落地的角度來看,5G和人工智能大規(guī)模落地的應用都不是很多,還以數(shù)據(jù)處理和高性能為主要應用場景。

鄭力預測,未來五年內(nèi)運算能力至少成長1000倍,這是集成電路產(chǎn)業(yè),尤其是封測行業(yè)實現(xiàn)高性能跨越性發(fā)展的堅實基礎。而在此發(fā)展過程中,半導體制造工藝從10nm制程開始,包含設計到流片在內(nèi)的全過程所需要的資本投入也在節(jié)節(jié)高升。7nm總開發(fā)成本大約是10nm的2倍,5nm的成本則已高達5億美元。

目前,臺積電和三星是唯二能量產(chǎn)7nm和5nm工藝的廠商。鄭力指出,到了7nm和5nm節(jié)點,臺積電要8年的時間才能夠回收資本投入。所以,集成電路產(chǎn)業(yè)向前發(fā)展正面臨一個巨大的資金成本障礙。

另外,萬物智能的市場趨勢大大提高了對芯片功能應用多元化的需求,One-SoC-Fits-All已不足以勝任。鄭力強調(diào),不同應用場景的芯片在性能、能耗、成本等方面必然側(cè)重不同,因此異構集成不可或缺。異構集成可避免對多種類芯片工藝一刀切,節(jié)省時間成本,并在3D維度有效延續(xù)摩爾定律。

談到摩爾定律的延續(xù),鄭力還認為,摩爾定律的核心并不單單只是18個月單位面積的晶體管數(shù)量提升,而是指半導體產(chǎn)業(yè)每在一個比較短的時間內(nèi),芯片的性能都會有大幅度的提高,這也是集成電路的魅力和活力所在。

高精密封測技術發(fā)展

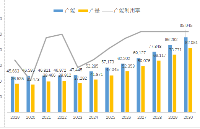

魏少軍教授在大會上指出,中國大陸集成電路封測業(yè)十五年間的年均復合增長率為15.23%,總體規(guī)模僅次于芯片設計業(yè)。銷售額方面,封測業(yè)也高于IC制造業(yè)。鄭力表示,封測業(yè)在中國大陸的集成電路領域的確起到了舉足輕重的作用,但前幾年封測行業(yè)還相對比較沉寂,外界普遍認為其高科技含量并不高。

集成電路的封測技術正在實現(xiàn)從先進封裝到高精密封裝的轉(zhuǎn)變,這使得封測行業(yè)與生態(tài)鏈技術上的緊密合作愈發(fā)凸顯,包括前道晶圓廠、IDM、材料與設備廠、EDA與IP廠商等。

鄭力表示,高精密封裝測試在設計封測結(jié)構和相關材料時,就可以發(fā)現(xiàn)封裝行業(yè)與生態(tài)鏈的相關性已變得非常之強,包括對電磁屏蔽材料、膠粘材料、散熱材料、塑膜材料、熱導介質(zhì)材料以及基板材料等生態(tài)鏈技術產(chǎn)品都提出了更高要求。因此,在后摩爾時代,實現(xiàn)高精密封測及異構集成標準化的首要條件就是一個涵蓋晶圓制造、封測、材料、協(xié)同設計仿真等的行業(yè)生態(tài)圈。

顯然,在對材料提出高要求的同時,高精密封測也順勢推動了本土高端材料工藝加速創(chuàng)新,例如高精密RDL電鍍成型材料、高精密封裝Bump塑膜材料、高精密封裝基板材料工藝、高精密銅面增加光滑度材料等。

除了材料的技術革新,測試和仿真也在整個高精密封裝環(huán)節(jié)中扮演重要角色。鄭力指出,封裝行業(yè)本身更多的元素是制造,設計的成分并不大。但隨著高精密封裝向前發(fā)展,協(xié)同設計也變得越來越重要。長電科技本身也在不斷加大在設計方面的投入,確保客戶在做高精密、高功效產(chǎn)品時,能夠無縫連接。

更大的挑戰(zhàn) 更高的上限

之所以說先進封裝到高精密封裝實現(xiàn)了跨越,國際上也有一個比較統(tǒng)一的共識,也就是高精密封裝需要克服三大技術挑戰(zhàn)。

鄭力指出,第一大挑戰(zhàn)就是I/O和Bump Pitch之間的間距越來越小,這對異構集成帶來了更為精密的挑戰(zhàn)。第二大挑戰(zhàn)是由存儲器帶來的,由于存儲器的異構集成相對于CPU而言比較慢,所以要將一快一慢一起封裝,就會帶來新的技術難題。第三大挑戰(zhàn)就是解決高密度I/O與各個GPU之間如何實現(xiàn)互聯(lián)的問題。

鄭力表示,從市場數(shù)據(jù)來看,業(yè)界對高精密封裝的定義還有兩個硬性要求,即RDL要小于3μm,Bump Pitch小于50μm。在2019年以前,只有臺積電和日月光能做到這兩點,但今年長電科技符合業(yè)界定義的高精密封裝工藝也即將開始量產(chǎn)。

整體來看,高精密封裝市場還非常小,2019年時總市場規(guī)模只有5億美元,但其增長速度十分驚人。鄭力預計,到2025年時市場規(guī)模將達到15億美元,屆時長電科技有望拿下8%的市場份額。

“隨著集成電路不斷的向高精尖領域發(fā)展,集成電路的封裝測試技術正在從定義模糊的先進封裝時代,走進高精密封測這樣一個嶄新的時代。無論是設計還是封測技術,都會迎來一個更高的上限。”鄭力說,“封測行業(yè)在向高精密封裝時代發(fā)展的過程當中,通過不斷的創(chuàng)新,與整個產(chǎn)業(yè)鏈的合作會變得越來越緊密。相信集成電路封測技術將在后摩爾定律時代起到非常關鍵的作用。”

責任編輯:tzh

-

集成電路

+關注

關注

5391文章

11617瀏覽量

362822 -

半導體

+關注

關注

334文章

27687瀏覽量

221489 -

封裝

+關注

關注

127文章

7990瀏覽量

143272 -

5G

+關注

關注

1356文章

48503瀏覽量

565516

發(fā)布評論請先 登錄

相關推薦

智能駕駛傳感器發(fā)展現(xiàn)狀及發(fā)展趨勢

新型儲能產(chǎn)業(yè)發(fā)展現(xiàn)狀及趨勢-2024年上半年數(shù)據(jù)發(fā)布簡版

高精密的電路噪聲如何計算?

金屬瓶密封測試儀的工作原理

包裝創(chuàng)新之路:密封測試儀引領密封性檢測新風尚

醫(yī)療機器人發(fā)展現(xiàn)狀與趨勢

工控機廠家發(fā)展現(xiàn)狀及未來趨勢

LED高精密燈板:卓越照明

2.晶體和振蕩器 行業(yè)研究及十五五規(guī)劃分析報告(行業(yè)發(fā)展現(xiàn)狀及“十五五”前景預測)

密封測試儀的主要構成部分

密封測試儀的操作要領

STM32國內(nèi)外發(fā)展現(xiàn)狀

密封測試儀的應用與重要性

萬兆電口模塊的產(chǎn)業(yè)發(fā)展現(xiàn)狀與前景展望

國產(chǎn)光耦2024:發(fā)展機遇與挑戰(zhàn)全面解析

評論