Vivado提出了UFDM(UltraFast Design Methodology)設計方法學,其核心思想是盡可能在設計初期發現潛在問題并解決。畢竟,越是在后期發現問題,越難發現關鍵問題,解決起來越費力,甚至會出現牽一發而動全身的被動局面。這是因為在Implementation階段,Vivado在每個子步驟或多或少都會做一些優化,這些優化可能會掩蓋一些問題。那么就時序收斂而言,在綜合之后要分析什么呢?

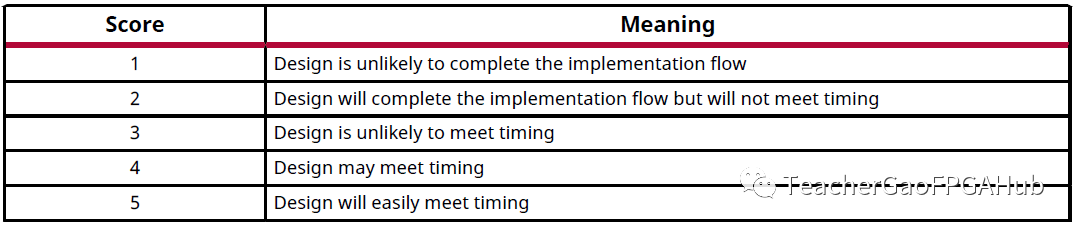

首先,很明確的是在綜合之后就要著手對設計進行分析,需要分析邏輯級數、資源利用率、時鐘拓撲結構、時鐘資源利用率和控制集,此外,還要分析BRAM/URAM/DSP的使用是不是最優的(例如,是否使用輸出寄存器或者級聯寄存器等),這些要素都會影響設計時序。這里重點要說的是Vivado提供的一個很好的命令report_qor_assessment。該命令可對設計進行整體的評估,并給出一個分數,以表征時序收斂問題的嚴重程度。Xilinx建議最好在綜合后就開始執行此命令。具體分數及其含義如下表所示(表格來源:Table 5, ug949)。

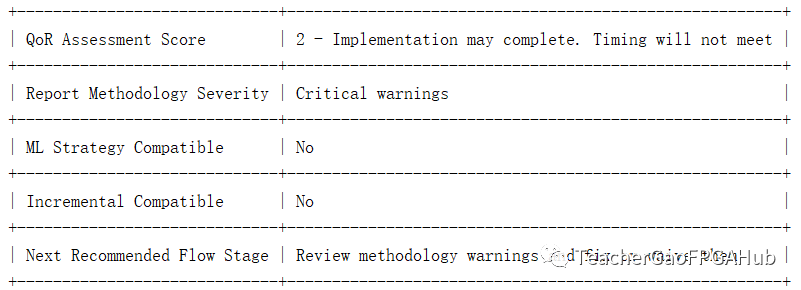

這個命令使用方法很簡單,只要打開綜合后的設計,在Vivado Tcl Console中輸入report_qor_assessment回車即可。生成的報告第一部分如下圖所示,可以看到第一行就是評分結果。如果這個分數是1/2/3,那么基本上可以不用執行后續流程,時序很難收斂,此時要把精力放在綜合階段所發現的問題上。

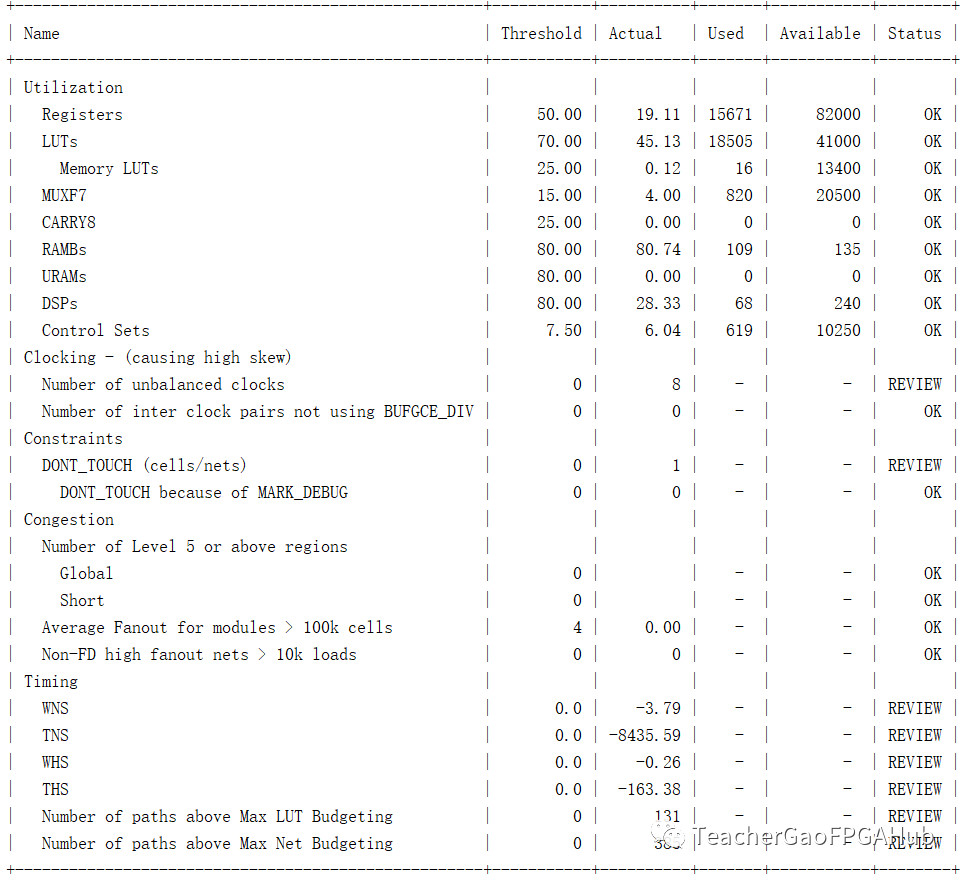

這個命令的第二部分是關鍵部分,如下圖所示。一方面給出了資源利用率,重要的是給出了資源利用率的真實值和指導值,一旦超過指導值,Status一欄會顯示為REVIEW。超過指導值不是不可以接受,而是會很大程度上給時序收斂帶來麻煩。另一方面,該報告也會分析邏輯級數、控制集、擁塞和扇出等。凡是Status標記為REVIEW的,需要格外關注,可接著用相應的命令進一步分析。例如,這里發現unbalanced clock,那么可以用report_clock_networks再進一步分析。

由此可見,分析的過程是先運行report_qor_assessment,再從中發現Status為REVIEW的條目,接著用相應的命令進一步分析。這會提高分析的效率,做到有的放矢。

責任編輯:PSY

原文標題:Vivado綜合后要分析什么

文章出處:【微信公眾號:Lauren的FPGA】歡迎添加關注!文章轉載請注明出處。

-

可編程邏輯

+關注

關注

7文章

516瀏覽量

44123 -

Vivado

+關注

關注

19文章

815瀏覽量

66715

原文標題:Vivado綜合后要分析什么

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

探索Vivado HLS設計流,Vivado HLS高層次綜合設計

如何在Vitis中把設置信息傳遞到底層的Vivado

vivado:時序分析與約束優化

在vivado中綜合Soc設計時發現的錯誤,請問如何解決?

在Vivado圖形化界面IDE中運行和調試Tcl命令

Vivado邏輯分析儀使用教程

在Vivado下利用Tcl腳本對綜合后的網表進行編輯過程

使用Vivado 2016.3中IBERT調試的好處及步驟

Vivado綜合引擎的增量綜合流程

在Vivado中怎么定制Strategy

在Vivado中怎么定制Strategy

Vivado綜合參數設置

Vivado每個子步驟在綜合之后要分析什么呢?

Vivado每個子步驟在綜合之后要分析什么呢?

評論