1 引言

本課題來源于一個無紙記錄儀的項目。在該項目中要求無紙記錄儀中有一路通道將工業(yè)現(xiàn)場采集到的頻率信號測量并顯示出來。傳統(tǒng)的測頻系統(tǒng)大多采用單片機(jī)加邏輯器件構(gòu)成,而這類測頻系統(tǒng)存在測頻速度慢、準(zhǔn)確度低、可靠性差的缺點(diǎn),故而使測量儀表達(dá)不到工業(yè)現(xiàn)場的要求。鑒于此,本文設(shè)計了一種基于嵌入式微處理器SEP3203和FPGA的測頻系統(tǒng)。將嵌入式微處理器靈活的控制功能與FPGA的設(shè)計靈活、高速和高可靠性的特點(diǎn)有機(jī)結(jié)合,從而達(dá)到工業(yè)現(xiàn)場的實(shí)時測量要求,而且該測頻系統(tǒng)具有可重構(gòu)性。

2 測頻原理

常用的直接測頻方法主要有測頻法和測周期法2種。測頻法就是在確定的閘門時間tw內(nèi),記錄被測信號的變化周期數(shù)(或脈沖個數(shù))Nχ,被測信號的頻率為fχ=Nχ/tw。測周期法需要有標(biāo)準(zhǔn)信號的頻率fs,在待測信號的一個周期內(nèi)tχ,記錄標(biāo)準(zhǔn)頻率的周期數(shù)Ns,被測信號的頻率為fχ=fs/Ns。這2種方法的計數(shù)值會產(chǎn)生±1個字的誤差,并且測試精度與計數(shù)器中記錄的數(shù)值Nχ或Ns有關(guān)。為了保證測試精度,一般對于低頻信號采用測周期法,對于高頻信號采用測頻法,這樣測試時很不方便,所以人們提出了等精度測頻的方法。

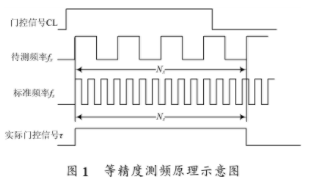

等精度測頻方法是在直接測頻方法的基礎(chǔ)上發(fā)展起來的,他的閘門時間不是固定的值,而是被測信號周期的整數(shù)倍,即與被測信號同步,消除了對被測信號計數(shù)所產(chǎn)生±1個字的誤差,達(dá)到了在整個測試頻段內(nèi)保持等精度測量。

在測量過程中,有2個計數(shù)器分別對標(biāo)準(zhǔn)信號和被測信號同時計數(shù)。首先給出閘門開啟信號(預(yù)置閘門上升沿),此時計數(shù)器并不開始計數(shù),而是等到被測信號的上升沿到來時,計數(shù)器才真正開始計數(shù)。然后預(yù)置閘門關(guān)閉信號(下降沿)到時,計數(shù)器并不立即停止計數(shù),而是等到被測信號的上升沿到來時才結(jié)束計數(shù),完成1次測量過程。從而實(shí)現(xiàn)了實(shí)際門控信號與被測信號的同步,進(jìn)而消除對被測信號計數(shù)產(chǎn)生的一個脈沖的誤差。

設(shè)在1次實(shí)際閘門時間τ中計數(shù)器對被測信號的計數(shù)值為Nχ,對標(biāo)準(zhǔn)信號的計數(shù)值為Ns。標(biāo)準(zhǔn)信號的頻率為fs,則被測信號的頻率為:

fχ=(Nχ/Ns)×fs (1)

3 誤差分析

由式(1)可知,若忽略標(biāo)頻的誤差,則等精度測頻可能產(chǎn)生的相對誤差為:

δ=(fχ-fe/fe)×100% (2)

其中,fe為被測信號頻率的準(zhǔn)確值。在測量中,由于fχ計數(shù)的起停時間都是由該信號的上升沿觸發(fā)的,在閘門時間τ內(nèi)對fχ的計數(shù)Nχ無誤差(τ=Nχtχ);對fs的計數(shù)Ns最多相差1個數(shù)的誤差,即│△Ns│≤1,其測量頻率為:

fe=[Nχ/(Ns+△Ns)]/fs (3)

將式(1)和式(3)代入式(2),并整理得:

δ=│△Ns│/Ns≤1/Ns-1/(τ×fs) (4)

由上式可以看出:測量頻率的相對誤差與被測信號頻率的大小無關(guān),僅與閘門時間和標(biāo)準(zhǔn)信號頻率有關(guān),即實(shí)現(xiàn)了整個測試頻段的等精度測量。閘門時間越長,標(biāo)準(zhǔn)頻率越高,測頻的相對誤差就越小。標(biāo)準(zhǔn)頻率可由穩(wěn)定度好、精度高的高頻晶體振蕩器產(chǎn)生,在保證測量精度不變的前提下,提高標(biāo)準(zhǔn)信號頻率,可使閘門時間縮短,即提高測試速度。

4 設(shè)計實(shí)現(xiàn)

(1)前級電路

即首先對待測信號進(jìn)行處理使其達(dá)到與后級電路相兼容的脈沖信號。

第一級電路是由開關(guān)三極管組成的零偏置放大電路,以保證放大電路具有良好的高頻響應(yīng),當(dāng)輸入信號為零或負(fù)電壓時,三極管工作在截止?fàn)顟B(tài),輸出為高電平,當(dāng)輸入為正電壓時,三極管工作在飽和狀態(tài)(導(dǎo)通),輸出電壓隨輸入電壓上升而下降。零偏置放大電路把如正弦波樣的正負(fù)交替波形變換成單向脈沖,這使得該電路可以測量任意方波信號、正弦波信號、鋸齒波信號、三角波信號等頻率。

第二級采用的是施密特非門觸發(fā)器CC74HC14,是對放大器輸出的信號進(jìn)行整形,使其輸出的信號成為與后級電路相兼容的脈沖信號。

(2)后級電路

各模塊用硬件描述語言Verilog HDL描述,通過EDA工具(ModelSim,Synplify,QuartusⅡ)進(jìn)行編譯、仿真、延時分析、管腳調(diào)整、綜合等步驟,最后燒錄到FPGA芯片中。將芯片與被測信號的放大整形模塊等外圍電路相連接,通過調(diào)試便完成了整個設(shè)計。

工作過程表示如下:

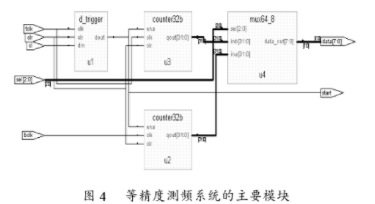

d_trigger實(shí)體實(shí)現(xiàn)門控信號和被測信號TCLK同步控制功能,內(nèi)部有一個受被測信號TCLK上升沿同步的D觸發(fā)器和預(yù)置門控信號CL共同作用產(chǎn)生實(shí)際的門控信號。counter32b1和counter32b2分別對標(biāo)準(zhǔn)頻率BCLK和被測頻率TCLK計數(shù),內(nèi)部為帶異步復(fù)位的32位二進(jìn)制計數(shù)器的時序進(jìn)程。mux64_8是數(shù)據(jù)選擇器,根據(jù)地址信號se1不同取值,64位數(shù)據(jù)依次從data_out[7:0]端輸出。

即當(dāng)CLR為1,D觸發(fā)器及兩個計數(shù)器清零。當(dāng)預(yù)置門控信號CL為1時,及經(jīng)放大整形后的被測信號TCLK上升沿到來時,同步電路輸出dout=1,帶使能端的2個計數(shù)器開始計數(shù);當(dāng)預(yù)置門控信號CL為0時,被測信號TCLK下一個上升沿到來時,同步電路輸出dout=0,即ena1=ena2=0,2個計數(shù)器停止計數(shù)。然后根據(jù)地址信號se1不同取值,64位數(shù)據(jù)依次從data_out[7:0]端輸出送入后端的乘法器和除法器模塊,按公式計算出被測頻率的值。

(3)嵌入式微處理器讀取測頻結(jié)果

本系統(tǒng)采用東南大學(xué)國家集成電路工程中心自主研發(fā)的嵌入式微處理器SEP 3203,并通過JTAG仿真器連接到PC機(jī)上的集成調(diào)試環(huán)境(IDE)軟件平臺,在IDE中統(tǒng)一完成C語言的編輯、編譯、連接。IDE選擇了ARM公司的開發(fā)軟件ADS 1.2,利用處理機(jī)的Embedded-ICE性能,通過JTAG接口實(shí)現(xiàn)實(shí)時的仿真調(diào)試。整個系統(tǒng)具有高性能、低功耗、低成本的特點(diǎn)。

FPGA與嵌入式微處理器SEP 3203之間采用總線的方式進(jìn)行數(shù)據(jù)交換,也就是將FPGA看作總線上的一個并行外部設(shè)備。FPGA通過一個SRAM接口與嵌入式微處理器SEP 3203相通信。即從嵌入式微處理器SEF‘3203的角度來看,F(xiàn)PGA與嵌入式微處理器SEP3203之間的通信就相當(dāng)于SEP 3203與一個SRAM之間的通信。在程序中讀寫指定區(qū)域的地址,可以實(shí)現(xiàn)對FPGA的讀寫操作。

處理器SEP 3203的外部存儲器接口(EMI)提供了6個可配置的片選信號:CSA,CSB,CSC,CSD,CSE,CSF,用來實(shí)現(xiàn)對ROM,SRAM,NOR FLASH的片選。其中CSE,CSF、可以配置成SDRAM片選信號。FPGA模塊使用的是CSB片選信號。CSB片選的默認(rèn)地址范圍為0x24000000~0x27FFFFFF,即FPGA組成的外設(shè)映射在SEP3203的地址空間為0x24000000~0x27FFFFFF,所以SEP3203在訪問FPGA時只需讀寫該地址空間中的任何一個地址,SEP3203能自動產(chǎn)生相應(yīng)的總線操作,從而讀取到FPGA的測頻結(jié)果。

5 仿真及驗(yàn)證

例1:標(biāo)準(zhǔn)頻率Fs為1 MHz;待測頻率Fχ為1 kHz。

看出Ns=0x7DOH=2 000;Nχ=0x2H=2,故測得頻率Fχ=(N=/Ns)*Fχ=1 kHz。

例2:標(biāo)準(zhǔn)頻率Fs為1 MHz;待測頻率Fχ為7.288 kHz。

看出Ns=0x80AH=2 058;Nχ=0xFH=15,故測得頻率Fχ=(Nχ/Ns)*Fs=7 288.630 Hz。

采用等精度頻率測量方法測量精度保持恒定,不隨所測信號的變化而變化,再結(jié)合FPGA集成度高、高速和高可靠性的特點(diǎn),使頻率的測頻范圍可達(dá)到0.1~1×10 8Hz,測頻全域的相對誤差恒定。

6 結(jié)語

本測頻系統(tǒng)將嵌入式微處理器靈活的控制功能與FPGA器件的結(jié)合,突破了傳統(tǒng)電子系統(tǒng)的設(shè)計模式,使系統(tǒng)開發(fā)速度快、成本低、系統(tǒng)性能大幅度提高。因此,在目前的電子設(shè)計中,充分利用嵌入式微處理器+FPGA結(jié)構(gòu)將起到事半功倍的效果。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1630文章

21779瀏覽量

604905 -

嵌入式

+關(guān)注

關(guān)注

5089文章

19161瀏覽量

306668 -

微處理器

+關(guān)注

關(guān)注

11文章

2272瀏覽量

82622

發(fā)布評論請先 登錄

相關(guān)推薦

SEP3203處理器的FPGA數(shù)據(jù)通信接口設(shè)計

SEP3203與偽彩LCD驅(qū)動SSD1770的接口設(shè)計

SEP3203處理器實(shí)現(xiàn)FPGA數(shù)據(jù)通信接口設(shè)計

基于ARM的無紙記錄儀系統(tǒng)設(shè)計

基于ARM的無紙記錄儀系統(tǒng)設(shè)計

SEP3203處理器與FPGA數(shù)據(jù)通信接口設(shè)計

基于嵌入式Linux的無紙記錄儀通信設(shè)計

基于SEP3203拉力試驗(yàn)機(jī)嵌入式測控系統(tǒng)設(shè)計

基于SMARTDAC+GP系列便攜式無紙記錄儀

彩色無紙記錄儀大概多少錢?

基于SEP3203和FPGA實(shí)現(xiàn)無紙記錄儀測頻系統(tǒng)的設(shè)計

基于SEP3203和FPGA實(shí)現(xiàn)無紙記錄儀測頻系統(tǒng)的設(shè)計

評論