MPC57xx 系列微控制器是 NXP 推出的一款采用 Power Architecture 技術(shù)構(gòu)建,面向汽車和工業(yè)動(dòng)力總成、發(fā)動(dòng)機(jī)管理、電機(jī)控制、車身控制、網(wǎng)關(guān)、底盤和安全、儀表板和顯示屏管理應(yīng)用。

其特點(diǎn)如下:

MPC57xx 低端到高端產(chǎn)品的軟件和硬件均兼容。采用高密度浮柵技術(shù)實(shí)現(xiàn)的嵌入式閃存。從單核到多核產(chǎn)品,運(yùn)行頻率從 32 MHz 到 300 MHz 以上,性能具有很高的擴(kuò)展性。根據(jù)SafeAssure 功能安全保障計(jì)劃設(shè)計(jì),使系統(tǒng)制造商輕松達(dá)到功能安全標(biāo)準(zhǔn),如 ISO 26262 ASIL-D 級(jí)安全完整性的要求。多種片上冗余和安全選項(xiàng),例如延遲鎖步內(nèi)核、DMA 控制器、存儲(chǔ)器保護(hù)單元、故障采集和控制單元,以及端到端 ECC。無(wú)以倫比的能效 – 并行處理加上一組精密的外設(shè),以及Power Architecture 工具和軟件生態(tài)合作體系的支持。

本期博文接之前的 MPC5744P 原理圖設(shè)計(jì)指南,給大家介紹下 MPC5744P 在 PCB(Layout)上的一些注意事項(xiàng),并結(jié)合我司自行設(shè)計(jì)的域控制器 - Lion 實(shí)例來(lái)講解。

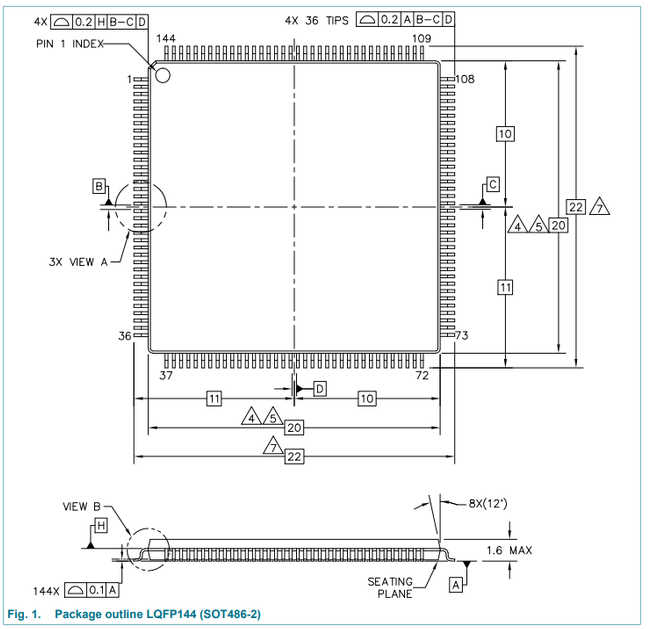

1. 封裝介紹1.1 封裝信息MPC5744P 封裝包括兩種:144 引腳 LQFP 封裝、257 引腳 PBGA 封裝。

兩種封裝在資源以及接口上的區(qū)別對(duì)比如下圖所示:

1.2 封裝尺寸

LQFP144 封裝信息:

https://www.nxp.com/docs/en/package-information/SOT486-2.pdf

PBGA257 封裝信息:

https://www.nxp.com/docs/en/package-information/SOT1547-1.pdf

2. PCB 設(shè)計(jì)建議

本設(shè)計(jì)指南 Layout 部分的示意圖引用了我司自行設(shè)計(jì)的“ADAS 域控制器 - Lion”,設(shè)計(jì)選用了 MPC5744P – 257 MAPBGA 封裝。大家如果對(duì)此方案的設(shè)計(jì)有想深入了解的,也可以轉(zhuǎn)至我們大大通的微博專區(qū)搜索關(guān)鍵字:【ADAS 域控制器硬件設(shè)計(jì)】,或者方案專區(qū)搜索方案:“域控制器”關(guān)鍵字即可找到對(duì)應(yīng)資源。

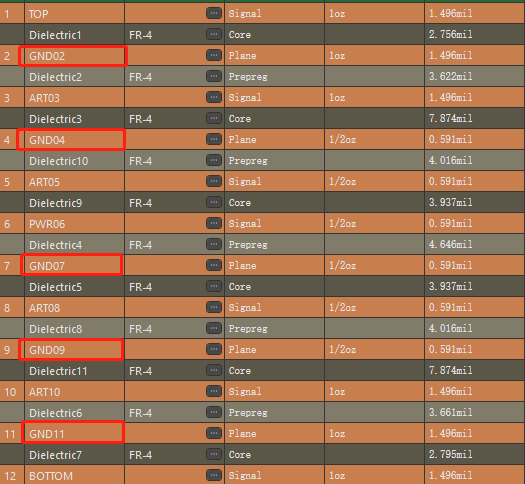

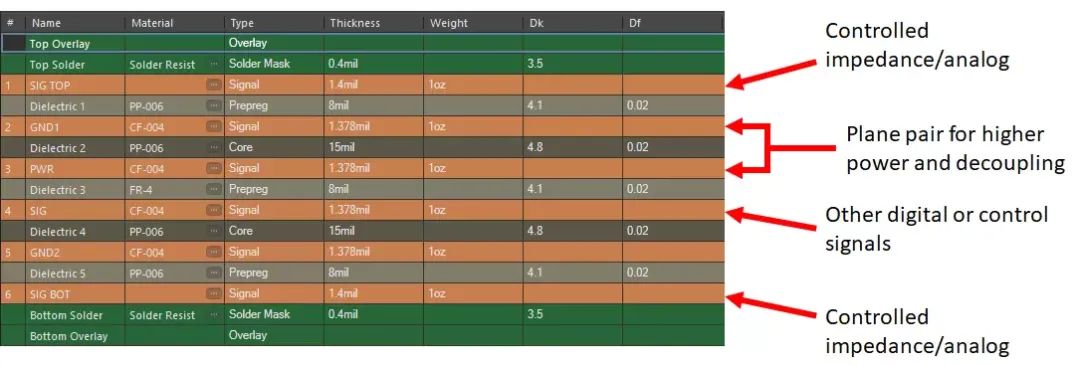

2.1 PCB 疊層結(jié)構(gòu)

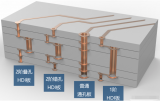

2.1.1 層的定義設(shè)計(jì)原則

器件面下層(第二層)為地平面,為器件面布線提供參考平面;所有信號(hào)層盡可能與地平面相鄰;主電源層盡可能與對(duì)應(yīng)地層相鄰;建議采用對(duì)稱結(jié)構(gòu)設(shè)計(jì)。針對(duì)于 MPC5744P 兩種封裝,推薦采用 4 層板設(shè)計(jì),以保證參考平面的完整性(BGA 257 封裝必須 4 層板,其中還有部分高速信號(hào)需要完整的參考平面例如 Zipwire)

下面的 PCB 設(shè)計(jì)參考建議基于 PBGA257 封裝,并采用 6 層板的疊層結(jié)構(gòu)設(shè)計(jì)。

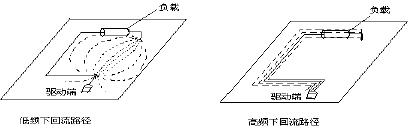

2.1.2 地和電源層設(shè)計(jì)注意事項(xiàng)

注意電源與地層的完整性,避免出現(xiàn)導(dǎo)通孔密集區(qū)域,破壞平面層的完整性;

平面分隔要考慮高速信號(hào)回流路徑的完整性;

高速信號(hào)、時(shí)鐘等關(guān)鍵信號(hào)要有一個(gè)相鄰地平面;

如高速信號(hào)在鄰層的回流路徑被分割,應(yīng)在其它布線層做補(bǔ)償;

20H 規(guī)則:為防止電源層向外輻射電磁干擾,應(yīng)內(nèi)縮 20H(電源層與地之間的介質(zhì)厚度)。

2.2 高速信號(hào)走線建2.2.1 晶振走線指導(dǎo)

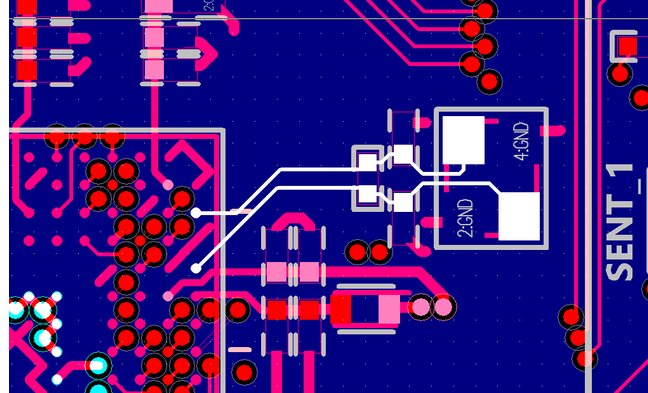

晶體盡量靠近主控放置,晶體的負(fù)載電容靠近管腳放置;晶體走線盡量短且走在表層,避免打孔換層;晶體電路建議包地處理,以隔離噪聲;晶體走線的鄰層保持完整地平面作參考,避免被任何走線分割

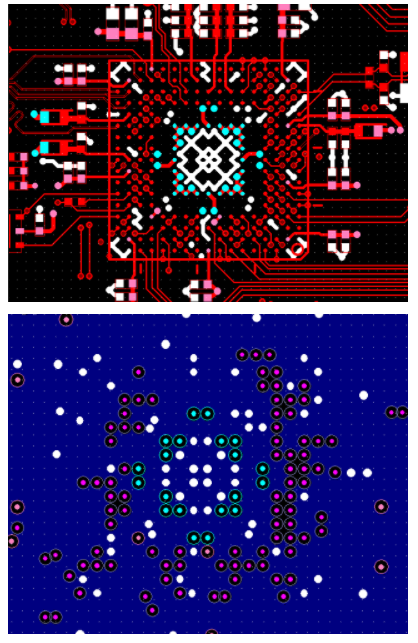

下圖為 Crystal 部分信號(hào)走線 Layout 示意圖:

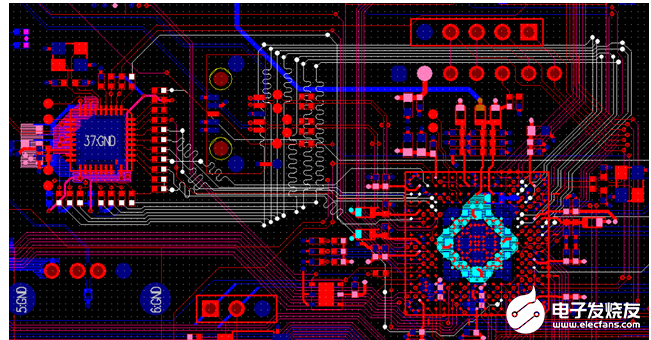

2.2.2 Ethernet 走線指導(dǎo)① PHY 盡量靠近主控,EMI 效果越好,控制在 15cm 以內(nèi);② 下述信號(hào)如有串聯(lián)匹配電阻,請(qǐng)靠近 PHY 放置,以改善 EMI

RXD[0:3],RX_CLK,RX_DV 走線盡量短并做等長(zhǎng)處理,走線長(zhǎng)度誤差小于 100mil;

RX_CLK 包地處理;

③ 下述信號(hào)如有串聯(lián)匹配電阻,請(qǐng)靠近 MPC5744P 放置,以改善 EMI

TXD[0:3],TX_CLK,TX_EN 走線盡量短并做等長(zhǎng)處理,走線長(zhǎng)度誤差小于 100mil;

TX_CLK 包地處理;

④ MDI (Media-Dependent Interface) 線對(duì)間做等長(zhǎng)處理,誤差小于 10mil,總長(zhǎng)度小于 12cm;⑤ 確保 PHY 的所有高速信號(hào)線有完整的參考面,與其它信號(hào)間距滿足 3W 布線原則;

下圖為 MII 部分信號(hào)走線 Layout 示意圖:

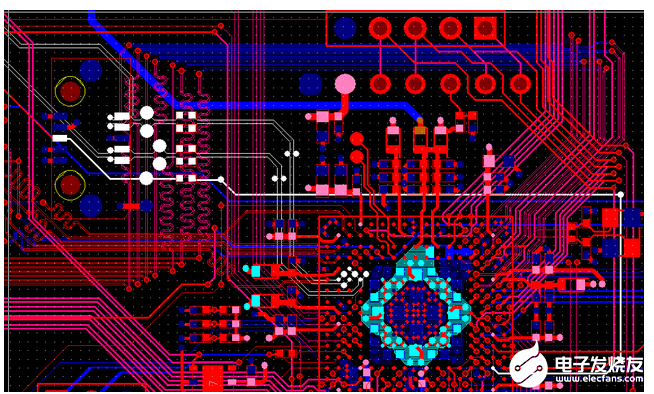

2.2.3 Zipwire 走線指導(dǎo)

信號(hào)走線按差分規(guī)則處理,保證有連續(xù)完整的參考面,差分阻抗控制在 100ohm±10ohm;差分走線盡量短并注意等長(zhǎng)處理,線對(duì)間誤差小于 10mil;

下圖為 Zipwire 部分信號(hào)走線 Layout 示意圖:

2.3 電源設(shè)計(jì)建議2.3.1 GND 設(shè)計(jì)

PCB 上必須有一層完整的 GND 層,用于散熱和保證信號(hào)完整性;

保證芯片每一個(gè) GND PAD 有對(duì)應(yīng)的過(guò)孔,連接到主地上。

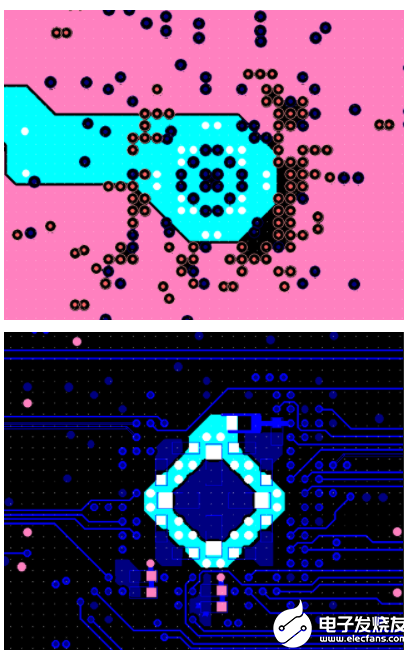

下圖為 GND 部分信號(hào)走線(鋪銅/L2) Layout 示意圖:

2.3.2 電源設(shè)計(jì)

電源網(wǎng)絡(luò)采用鋪銅處理;

采用多層網(wǎng)絡(luò)供電;

每個(gè) VDD_LV_CORE PAD 有對(duì)應(yīng)的一個(gè)過(guò)孔連到電源平面。

下圖為 VDD_LV_CORE 部分信號(hào)走線(鋪銅/L3) Layout 示意圖:

3. 參考文檔

① MPC5744P Datasheet:《MPC5744P microcontrollers - Data Sheet (REV 6.1)》② 大大通方案《基于 NXP S32V234+NXP MPC5744P ADAS 域控制器解決方案》:https://www.wpgdadatong.com/cn/solution/detail?PID=524

-

Layout

+關(guān)注

關(guān)注

14文章

405瀏覽量

61877 -

adas

+關(guān)注

關(guān)注

309文章

2189瀏覽量

208747 -

高速信號(hào)

+關(guān)注

關(guān)注

1文章

231瀏覽量

17726

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

PCB設(shè)計(jì)中的疊層原則

6層PCB疊層設(shè)計(jì)指南

原創(chuàng)|PCB設(shè)計(jì)中疊層結(jié)構(gòu)的設(shè)計(jì)建議

PCB原創(chuàng)|高速PCB設(shè)計(jì)軟件層疊結(jié)構(gòu)設(shè)計(jì)的建議

PCB設(shè)計(jì)中疊層算阻抗時(shí)需注意哪些事項(xiàng)?

【資料】PCB的EMC設(shè)計(jì)之常見(jiàn)的PCB疊層結(jié)構(gòu)

【資料】PCB疊層結(jié)構(gòu)(1-8層)參考及建議

【資料】淺談PCB疊層設(shè)計(jì)

PCB設(shè)計(jì)中6層板疊層怎么選

PCB疊層結(jié)構(gòu)設(shè)計(jì)詳解

各種疊層結(jié)構(gòu)的PCB圖內(nèi)部架構(gòu)設(shè)計(jì)

PCB設(shè)計(jì)建議 PCB疊層結(jié)構(gòu)

PCB設(shè)計(jì)建議 PCB疊層結(jié)構(gòu)

評(píng)論