來自復旦大學微電子學院的消息,該校周鵬團隊針對具有重大需求的3-5nm節點晶體管技術,驗證了雙層溝道厚度分別為0.6 /1.2nm的圍柵多橋溝道晶體管(GAA,Gate All Around),實現了高驅動電流和低泄漏電流的融合統一,為高性能低功耗電子器件的發展提供了新的技術途徑。

據悉,相關成果已經在第66屆IEDM國際電子器件大會上在線發表。

報道提到,工藝制程提升到5nm節點以下后,傳統晶體管微縮提升性能難以為繼,需要做重大革新。于是GAA晶體管乘勢而起,它可實現更好的柵控能力和漏電控制。

此番周鵬團隊設計并制備出超薄圍柵雙橋溝道晶體管,驅動電流與普通MoS2晶體管相比提升超過400%,室溫下可達到理想的亞閾值擺幅(60mV/dec),漏電流降低了兩個數量級。

什么是GAA晶體管

據悉,GAA晶體管也被譯作“環繞柵極晶體管”,它的出現是為了取代華人教授胡正明團隊研制的FinFET(鰭式場效應晶體管)。

為什么要談“取代”,首先要從FinFET說起。根據知乎作者“淺醉閑眠”一篇科普文章中的介紹,所謂的晶體管,是指一種等效于水龍頭作用的電子器件。水龍頭可以用來控制水流的大小以及開關,與之類似晶體管的作用是控制電流的大小與開關。這里面另外一個關鍵詞是場效應,指的是這種對電流的控制是通過施加一個電場來實現的,而決定場效應晶體管效率的一個重要因素就是柵極對通道的控制能力。

柵極越小,在同樣的電壓下能實現的電流也越大。這是決定晶體管性能的一個關鍵參數。但是5nm之后,鰭式晶體管將會面臨許多問題。

比如隨著柵線之間的間距縮小,很難再像之前那樣在一個單元內填充多個鰭線。而如果只做一個鰭線的話,生產工藝又很難保證不同器件之間性能一致。因為控制多個鰭線的平均尺寸要遠比控制單個鰭線的尺寸容易得多。其次也是更為致命的問題是,隨著柵線之間的間距進一步減小,鰭式晶體管的靜電問題急速加劇并直接制約晶體管性能的進一步提升。這里所說的靜電問題是指鰭式晶體管本身的結構帶來的一系列寄生電容以及電阻的問題。例如柵極與柵極之間的寄生電容,柵極與通道之間的寄生電容,柵極與金屬電極之間的寄生電容,以及源極與漏極之間的寄生電阻等問題。IMEC之前的模擬表明,當柵線之間的間距縮小至40納米之后,鰭式晶體管的性能將會趨于飽和。因此,在5納米之后,工業界迫切需要一個新的結構來替代鰭式晶體管結構,這就帶來了全環繞柵極晶體管。

全環繞柵極晶體管的特點是實現了柵極對溝道的四面包裹,源極和漏極不再和基底接觸,而是利用線狀(可以理解為棍狀)或者平板狀、片狀等多個源極和漏極橫向垂直于柵極分布后,實現MOSFET的基本結構和功能。這樣設計在很大程度上解決了柵極間距尺寸減小后帶來的各種問題,包括電容效應等,再加上溝道被柵極四面包裹,因此溝道電流也比FinFET的三面包裹更為順暢。在應用了GAA技術后,業內估計基本上可以解決3nm乃至以下尺寸的半導體制造問題。

簡單概括就是,隨著摩爾定律的演進,傳統結構已無法滿足先進工藝的需求,GAA晶體管的出現能夠讓其繼續往下延續,進一步芯片工藝的極限。

三星3nm或先用上GAA晶體管,臺積電求穩

當前7nm成主流,5nm成熟且可以量產,再下一個節點就是3nm工藝了,這個節點非常重要,因為摩爾定律一直在放緩,FinFET晶體管一度被認為只能延續到5nm節點,3nm要換全新技術方向。所以GAA晶體管技術已經被不少半導體企業所關注。

據悉,三星打算從2022年投產的第一代3nm就引入GAA晶體管,據介紹,基于全新的GAA晶體管結構,三星通過使用納米片設備制造出了MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應管),該技術可以顯著增強晶體管性能,主要取代FinFET晶體管技術。此外,MBCFET技術還能兼容現有的FinFET制造工藝的技術及設備,從而加速工藝開發及生產。

具體來說,與現在的7nm工藝相比,3nm工藝可將核心面積減少45%,功耗降低50%,性能提升35%。

由于之前在先進工藝上進度落后了,三星在3nm進行了一場豪賭,是第一個大規模上馬GAA技術的,目的就是希望通過激進的手段迅速扭轉晶圓代工市場上的地位,GAA成敗很關鍵。

臺積電可能沒有三星這么激進,在3nm節點也會跟之前的7nm工藝一樣采取兩步走的方式,第一代3nm工藝還會繼續改進FinFET晶體管工藝,在第二代3nm或者2nm節點才會升級到GAA晶體管技術。

這樣做一方面是出于技術研發的考慮,臺積電在GAA技術上落后三星12到18個月,另一方面則是要在進度上趕超,2021年3月份就準備試產,所以不能急著上GAA工藝,先用FinFET工藝頂上。

-

芯片

+關注

關注

456文章

51062瀏覽量

425804 -

晶體管

+關注

關注

77文章

9728瀏覽量

138641

發布評論請先 登錄

相關推薦

IBM與Rapidus在多閾值電壓GAA晶體管技術的新突破

晶體管故障診斷與維修技巧 晶體管在數字電路中的作用

晶體管反相器的原理及應用

達林頓晶體管概述和作用

單結晶體管的作用和工作區域

NMOS晶體管和PMOS晶體管的區別

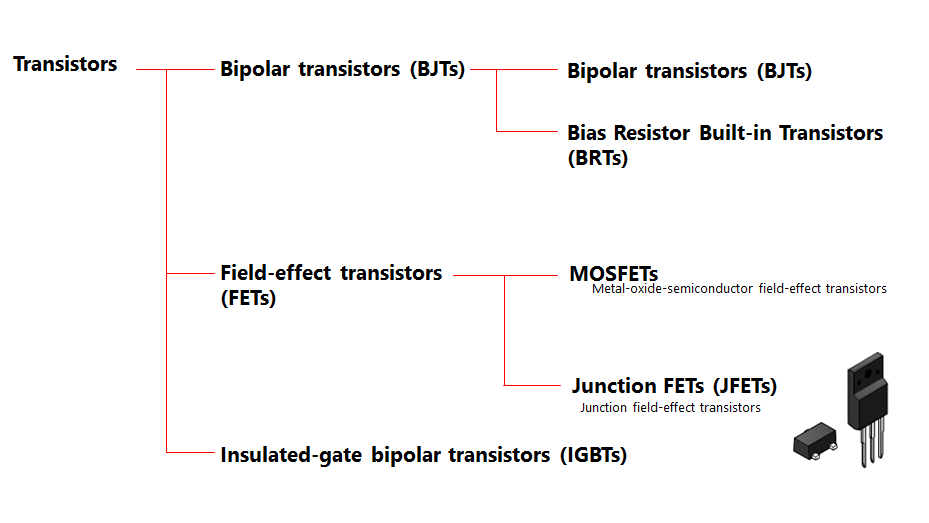

晶體管的主要類型有哪些

晶體管的主要材料有哪些

GaN晶體管的應用場景有哪些

晶體管處于放大狀態的條件是什么

晶體管電流的關系有哪些類型 晶體管的類型

晶體管的分類與作用

晶體管測試儀的主要作用

如何判斷晶體管基本放大電路是哪種

什么是達林頓晶體管?達林頓晶體管的基本電路

GAA晶體管是什么,它的作用有哪些

GAA晶體管是什么,它的作用有哪些

評論