在ISSCC 2020上臺積電呈現了其基于ULL 22nm CMOS工藝的32Mb嵌入式STT-MRAM。該MRAM具有10ns的讀取速度,1M個循環的寫入耐久性,在150度下10年以上的數據保持能力和高抗磁場干擾能力。

ULL 22nm STT-MRAM的動機

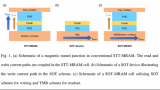

與閃存相比,TSMC的嵌入式STT-MRAM具有明顯的優勢。閃存需要12個或更多額外的掩模,只能在硅基板上實現,并且以頁面模式寫入。而STT-MRAM在后段(BEOL)金屬層中實現,如圖1所示,僅需要2-5個額外的掩模,并且可以字節模式寫入。

該STT-MRAM基于臺積電的22nm ULL (Ultra-Low-Leakage)CMOS工藝平臺,具有10ns的極高讀取速度,讀取功率為0.8mA /MHz/bit。對于32Mb數據,它具有100K個循環的寫入耐久性,對于1Mb數據,具有1M個循環的耐久性。它支持在260°C下進行90s的IR回流焊,在150°C下10年的數據保存能力。它以1T1R架構實現單元面積僅為0.046平方微米,25度下的32Mb陣列的漏電流僅為55mA,相當于在低功耗待機模式(LPSM,Low Power Standby Mode)時為1.7E-12A / bit。。它利用帶有感應放大器微調和1T4R參考單元的讀取方案。

圖1. M1和M5之間的BEOL金屬化層中的STT-MRAM位單元的橫截面。

1T1R MRAM的操作和陣列結構

為減小寫電流路徑上的寄生電阻,采用了兩列公共源極線(CSL,common source line )陣列結構,如圖所示。

圖2.1T1R單元在帶有2列CSL的512b列的陣列示意圖

字線由電荷泵過驅動,以提供足夠的數百毫安的開關電流用于寫操作,要求將未選擇的位線偏置在“寫禁止電壓”(VINHIBIT,write-inhibit voltage)上,以防止訪問時在所選行中未選中列的晶體管上產生過高的電應力。為了減少未選中的字線上的存取晶體管的位線漏電流,該字線具有負電壓偏置(VNEG)。用于讀取,寫入-0和寫入-1的陣列結構的偏置如圖3所示。

圖3.讀,寫0和寫1操作的字線和位線的單元陣列電壓表。

MRAM讀取操作

為了從LPSM快速,低能耗喚醒以實現高速讀取訪問,它采用了細粒度的電源門控電路(每128行一個),分兩步進行喚醒(如圖4所示)。電源開關由兩個開關組成,一個開關用于芯片電源VDD,另一個開關用于從低壓差(LDO, Low Drop-Out )穩壓器提供VREG的穩定電壓。首先打開VDD開關以對WL驅動器的電源線進行預充電,然后打開VREG開關以將電平提升至目標電平,從而實現<100ns的快速喚醒,同時將來自VREG LDO的瞬態電流降至最低。

圖4.具有兩步喚醒功能的細粒度電源門控電路(每128行一個)。

圖5所示的隧道磁電阻比(TMR)House曲線是反平行狀態Rap與平行狀態Rp之間的比率隨電壓的變化,在較高溫度下顯示出較低的TMR和較小的讀取窗口。

圖5 TMR的House曲線顯示了在125°C時減小的讀取窗口

Rap和Rp狀態的電阻分布,當計入位線金屬電阻和訪問晶體管電阻時,總的讀取路徑上的電阻,在兩個狀態之間的差值減小,如圖6所示。

圖6.Rap和Rp的電阻分布間距在計入寄生電阻時變小

為了感測MTJ的電阻,必須在讀取期間將其兩端的電壓通過晶體管N1和N2鉗位到一個低值,以避免讀取干擾,并對其進行微調以消除感測放大器和參考電流偏移。參考電阻是1T4R配置R?(R p + R ap)/ 2 + R1T,如圖7所示。

圖7.具有微調能力的感測放大器顯示了晶體管N1和N2上的讀取鉗位電壓,以防止讀取干擾。參考R(R p + Rap)/ 2 + R1T

如圖8,讀取時序圖和shmoo圖所示,這種配置在125°C時能夠實現小于10ns的讀取速度。

圖8. 125°C時的讀取時序圖和讀取shmoo圖。

-

臺積電

+關注

關注

44文章

5651瀏覽量

166659 -

IC設計

+關注

關注

38文章

1297瀏覽量

104073

發布評論請先 登錄

相關推薦

臺積電熊本工廠正式量產

臺積電2納米制程技術細節公布:性能功耗雙提升

臺積電2nm制成細節公布:性能提升15%,功耗降低35%

臺積電2納米制程技術細節公布

臺積電CoWoS產能將提升4倍

臺積電布局FOPLP技術,推動芯片封裝新變革

曝臺積電考慮引進CoWoS技術

瑞薩電子宣布已開發具有快速讀寫操作的測試芯片MRAM

臺積電開發出SOT-MRAM陣列芯片,功耗極低

臺積電引領新興存儲技術潮流,功耗僅為同類技術的1%

臺積電STT-MRAM技術細節講解

臺積電STT-MRAM技術細節講解

評論