作者:邢萬(wàn),俞珍傳,賀磊,陸鋒

1 引言

隨著IC設(shè)計(jì)方法與工藝技術(shù)的不斷進(jìn)步,集成電路結(jié)構(gòu)和功能日益復(fù)雜,測(cè)試問(wèn)題成為必 須考慮的關(guān)鍵問(wèn)題,測(cè)試成本作為整個(gè)IC產(chǎn)品成本的主要組成部分,也受到了極大的重視。由 于國(guó)內(nèi)自動(dòng)測(cè)試設(shè)備(Automatic testing EquIPMent)主要依賴進(jìn)口,價(jià)格昂貴,測(cè)試圖形產(chǎn)生, 特別是測(cè)試量產(chǎn)過(guò)程的花費(fèi)(例如測(cè)試時(shí)間),就顯得尤為重要。為了使測(cè)試成本保持在合理 的限度內(nèi),最有效的方法就是采用可測(cè)性設(shè)計(jì)(Design For Testibility)。可測(cè)性設(shè)計(jì)(DFT) 是適應(yīng)集成電路的發(fā)展要求所出現(xiàn)的一種技術(shù),主要任務(wù)是通過(guò)適當(dāng)?shù)脑O(shè)計(jì)重構(gòu)或調(diào)整來(lái)提高電路整體性能的輔助設(shè)計(jì)方法,其核心是通過(guò)適當(dāng)?shù)那捌诖鷥r(jià)來(lái)提高電路的可測(cè)性,即可控制 性和可觀察性,降低產(chǎn)品的測(cè)試成本。本文設(shè)計(jì)的RISC_CPU是一個(gè)復(fù)雜的數(shù)字邏輯電路,采用DFT策略可以很好地解決測(cè)試問(wèn)題。

2 CPU 結(jié)構(gòu)

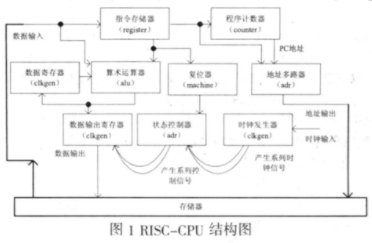

本文設(shè)計(jì)的RISC_CPU,主要分為幾個(gè)模塊,各個(gè)模塊之間的互連關(guān)系如圖1所示。

1. 時(shí)鐘發(fā)生器(clkgen):產(chǎn)生一系列的時(shí)鐘信號(hào)送往 CPU 其他部件;

2. 指令寄存器(register):存儲(chǔ)指令;

3. 累加器(accum):存放算術(shù)邏輯運(yùn)算單元當(dāng)前的結(jié)果,它也是算術(shù)邏輯運(yùn)算單元雙目運(yùn)算中的一個(gè)數(shù)據(jù)來(lái)源;

4. 算術(shù)邏輯運(yùn)算單元(alu):根據(jù)輸入的不同操作碼分別實(shí)現(xiàn)相應(yīng)的加、與、讀、寫(xiě)、異或,跳轉(zhuǎn)等指令;

5. 數(shù)據(jù)輸出控制器(datactl):控制累加器的數(shù)據(jù)輸出;

6. 狀態(tài)控制器(control):CPU 的控制核心,用于產(chǎn)生一系列的控制信號(hào),啟動(dòng)或停止某些部件;

7. 程序計(jì)數(shù)器(counter):提供指令地址,以便讀取指令;

8. 地址多路器(adr):選擇輸出的地址是 PC(程序計(jì)數(shù))地址還是跳轉(zhuǎn)的目標(biāo)地址;

9. 狀態(tài)復(fù)位器(machine),狀態(tài)控制器復(fù)位信號(hào)生成模塊。

3 基本概念釋義

3.1 掃描

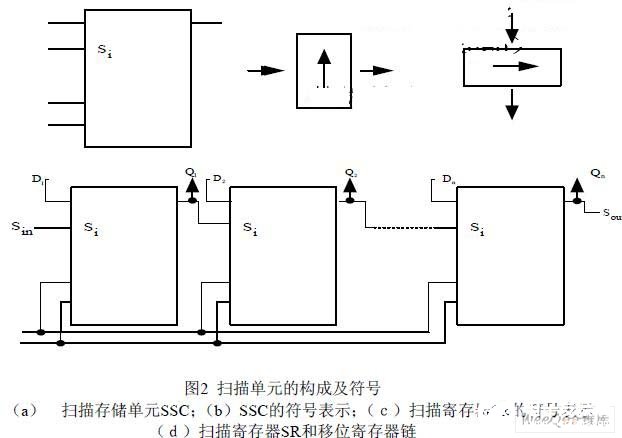

掃描設(shè)計(jì)方法是通過(guò)將電路中的時(shí)序元件替換為相應(yīng)的可掃描的時(shí)序元件(即掃描單元), 然后將它們串聯(lián)起來(lái),形成一個(gè)從測(cè)試輸入到測(cè)試輸出的串行移位寄存器。這樣,測(cè)試數(shù)據(jù)由 測(cè)試輸入,通過(guò)移位,到達(dá)要控制的單元;內(nèi)部數(shù)據(jù),再次通過(guò)移位,由測(cè)試輸出的端口,觀 察結(jié)果。

3.2 基于沿觸發(fā)的掃描單元結(jié)構(gòu)

圖2是掃描單元構(gòu)成,其工作原理是:在掃描模式控制下實(shí)現(xiàn)數(shù)據(jù)的掃描輸出,即T/N =1 時(shí),掃描數(shù)據(jù)從i s 輸入,在時(shí)鐘作用下從Q輸出,輸出的是掃描輸入的數(shù)據(jù)。而當(dāng)T/N = 0時(shí), 掃描單元處于正常工作模式,也就是在時(shí)鐘作用下從Q輸出,但輸出的是單元正常工作的數(shù)據(jù)。

4 掃描設(shè)計(jì)

4.1 自動(dòng)掃描單元替換

RISC_CPU有近萬(wàn)個(gè)時(shí)序單元,為了獲得較高的故障覆蓋率,采用了全掃描的設(shè)計(jì)方案, 使用Synopsys公司Design Compiler自動(dòng)完成測(cè)試插入功能,用最基本的掃描觸發(fā)器來(lái)替換時(shí)序 單元,共設(shè)計(jì)了9條掃描連, 測(cè)試激勵(lì)使用Synopsys公司的TetraMAX測(cè)試產(chǎn)生工具產(chǎn)生出來(lái):共 產(chǎn)生組合測(cè)試向量1413個(gè),其故障覆蓋率達(dá)到95.06%;產(chǎn)生時(shí)序測(cè)試向量147個(gè),覆蓋率增加到 97.39%。在剩余2.61%未覆蓋的故障中,1.4%的故障是電路設(shè)計(jì)中的冗余故障。

4.2 掃描移位測(cè)試

測(cè)試使能端test_se=1,將電路置為掃描模式,每條掃描鏈上的所有觸發(fā)器數(shù)為n,從scan_in送 入一個(gè)長(zhǎng)為n+4的輸入序列:00110011…0011。這個(gè)序列將在每個(gè)掃描觸發(fā)器中產(chǎn)生所有可能的 4種跳變信號(hào)情況:0→0,0→1,1→1,1→。從scan_out可以觀測(cè)到信號(hào)跳變情況。這個(gè)測(cè)試覆 蓋了觸發(fā)器中大多數(shù)單故障型故障,從而確保掃描鏈的移位操作不出錯(cuò)。由于9條掃描鏈可以并 發(fā)測(cè)試,以最長(zhǎng)掃描鏈的長(zhǎng)度為準(zhǔn),完成移位測(cè)試的測(cè)試時(shí)間約為582=(289*2+4)個(gè)測(cè)試時(shí)鐘 周期。

4.3 固定型故障的測(cè)試

單固定型故障是芯片測(cè)試的主要目標(biāo)。由于我們采用全掃描設(shè)計(jì),因此對(duì)大部分電路可以 使用組合電路的測(cè)試方式完成,即測(cè)試輸入數(shù)據(jù)通過(guò)掃描鏈準(zhǔn)備好后,只經(jīng)過(guò)一個(gè)節(jié)拍就進(jìn)行 輸出響應(yīng)的捕獲。但是,由于RAM的存在,讀寫(xiě)RAM的信號(hào)不可觀測(cè)和控制,因此對(duì)于最靠近 RAM的一級(jí)觸發(fā)器到RAM之間的組合邏輯,稱為RAM的陰影邏輯(shadow logic),無(wú)法通過(guò)組 合電路的測(cè)試方式完成。解決這個(gè)問(wèn)題一般有兩種方式,一種方式是在RAM外部插入測(cè)試點(diǎn)來(lái) 提高陰影邏輯的可控制性和可觀測(cè)性, 由于這會(huì)影響訪存RAM的性能,這種方案在該 RISC_CPU中不可取。另一種方式被采用,即對(duì)RAM建立等價(jià)功能模型,這將導(dǎo)致需要用測(cè)試 時(shí)序電路的方式來(lái)測(cè)試陰影邏輯。

為了保證測(cè)試時(shí)鐘的可控性,在芯片測(cè)試時(shí)需要將測(cè)試控制信號(hào)test 置為有效(test=1),使 芯片工作在測(cè)試方式。對(duì)一個(gè)芯片的測(cè)試過(guò)程如下:在掃描模式下,測(cè)試激勵(lì)通過(guò)一條或幾條 掃描的scan_in管腳,串行移位到響應(yīng)的掃描觸發(fā)器。當(dāng)一個(gè)測(cè)試的所有輸入激勵(lì)準(zhǔn)備好后,使 用系統(tǒng)時(shí)鐘將測(cè)試激勵(lì)送入被測(cè)邏輯。一個(gè)時(shí)鐘周期(對(duì)組合測(cè)試)或幾個(gè)時(shí)鐘周期(對(duì)時(shí)序 測(cè)試)后從被測(cè)模塊的輸出端口所在的掃描鏈上,將輸出信號(hào)依次串行移位到相應(yīng)的scan_out 引 腳,將讀出的數(shù)據(jù)與期待的輸出比較,以判斷被測(cè)邏輯中是否存在故障。

5 存儲(chǔ)器測(cè)試

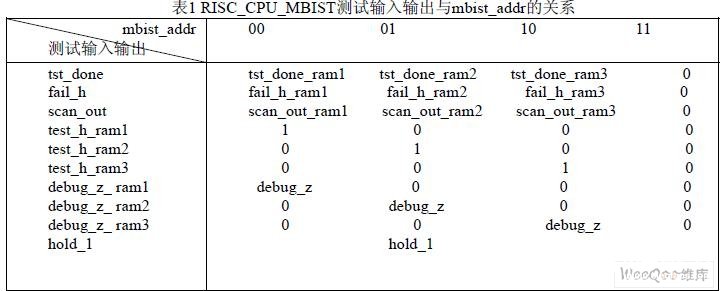

本文采用了Mentor 公司的MBIST 插入工具M(jìn)BISTArchitect。MBISTArchitect 可以創(chuàng)建和 連接RTL 級(jí)BIST 邏輯到待測(cè)芯片中。RISC_CPU 的存儲(chǔ)器由RAM1、RAM2、RAM3 三塊大 小分別為20*128 字節(jié)、64*128 字節(jié)、64*48 字節(jié)的存儲(chǔ)器構(gòu)成面積約為45%,我們用三塊帶有 比較結(jié)構(gòu)的MBIST 電路,這三塊MBIST 是通過(guò)mbist_addr 和MBIST 模塊來(lái)控制的,三塊MBIST 電路共享測(cè)試控制信號(hào)hold_1 和診斷控制信號(hào)debug_z 以及三個(gè)測(cè)試輸出tst_done、fail_h 和 scan_out(錯(cuò)誤定位即診斷數(shù)據(jù)輸出)。MBIST 測(cè)試使能信號(hào)由mbist_addr 解碼得到,從而決定三塊MBIST 電路的工作次序以及最終的芯片測(cè)試輸出,他們之間的關(guān)系由表1 給出。

由表1可知:當(dāng)mbist_addr為00時(shí),ram1的MBIST電路的控制信號(hào)即為外部相應(yīng)輸入的控制 信號(hào),其他兩個(gè)ram模塊的MBIST電路的控制信號(hào)輸入置為0。異步復(fù)位置位有效,系統(tǒng)處于ram1 的測(cè)試狀態(tài),系統(tǒng)測(cè)試輸出即為ram1的測(cè)試輸出;當(dāng)mbist_addr為01時(shí),系統(tǒng)處于ram2的測(cè)試狀 態(tài),系統(tǒng)測(cè)試輸出即為ram2的MBIST測(cè)試輸出;當(dāng)mbist_addr為10時(shí),系統(tǒng)處于ram3的測(cè)試狀 態(tài),系統(tǒng)測(cè)試輸出為ram3的MBIST測(cè)試輸出。

為了得到每一塊RAM的測(cè)試結(jié)果,我們將MBIST的測(cè)試結(jié)果通過(guò)第九條掃描鏈移出,在多 個(gè)分組測(cè)試中,測(cè)試時(shí)間最長(zhǎng)的執(zhí)行MBIST算法大約需要1044800個(gè)時(shí)鐘周期,加上初始化和測(cè) 試完成后將測(cè)試結(jié)果掃描移出的時(shí)間,共需要的時(shí)鐘周期數(shù)不超過(guò)10445900個(gè),如果測(cè)試時(shí)鐘 的頻率為20MHZ,則測(cè)試時(shí)間約為0.52秒。借助于BIST,對(duì)嵌入式存儲(chǔ)器的單固定型故障、開(kāi) 路故障、地址譯碼故障均獲得了100%的故障覆蓋率,達(dá)到了預(yù)定的要求。

6 結(jié)束語(yǔ)

本文合理地選擇了邊界掃面和內(nèi)建自測(cè)試方式,根據(jù)時(shí)鐘域劃分各個(gè)功能單元,修改設(shè)計(jì), 消除了設(shè)計(jì)規(guī)則違反,選擇了適當(dāng)?shù)木C合流程,在對(duì)設(shè)計(jì)負(fù)面影響不大的情況下,僅增加了0.2% 的時(shí)序消耗和0.02%的面積消耗,取得了良好的可測(cè)性效果,達(dá)到了芯片邏輯的97.39%的單固 定型故障覆蓋率,能夠監(jiān)測(cè)到RAM中100%的單固定型故障覆蓋率,滿足了芯片生產(chǎn)測(cè)試需求。

責(zé)任編輯:gt

-

控制器

+關(guān)注

關(guān)注

112文章

16402瀏覽量

178591 -

IC

+關(guān)注

關(guān)注

36文章

5965瀏覽量

175799 -

cpu

+關(guān)注

關(guān)注

68文章

10882瀏覽量

212224

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

DFT的優(yōu)缺點(diǎn)比較 DFT在機(jī)器學(xué)習(xí)中的應(yīng)用

DFT與離散時(shí)間傅里葉變換的關(guān)系 DFT在無(wú)線通信中的應(yīng)用

DFT在圖像處理中的作用 DFT在音頻信號(hào)處理中的應(yīng)用

DFT在信號(hào)處理中的應(yīng)用 DFT與FFT的區(qū)別

SiFive 推出高性能 Risc-V CPU 開(kāi)發(fā)板 HiFive Premier P550

Imagination CPU 系列研討會(huì) | RISC-V 平臺(tái)的性能分析和調(diào)試

香蕉派 BPI-CanMV-K230D-Zero 采用嘉楠科技 K230D RISC-V芯片設(shè)計(jì)

晶心科技與Arteris攜手加速RISC-V SoC的采用

RISC-V的MCU關(guān)于USB高速通信設(shè)計(jì)的難點(diǎn)

龍芯:自主研發(fā)CPU提升性能,單核通用性能提高20倍

Imagination 推出全新Catapult CPU,加速RISC-V 設(shè)備采用

瑞薩推出采用自研CPU內(nèi)核的通用32位RISC-V MCU 加強(qiáng)RISC-V生態(tài)系統(tǒng)布局

芯來(lái)科技推出1000系列,進(jìn)一步開(kāi)啟了亂序高性能CPU的篇章

采用DFT策略提高RISC_CPU的性能設(shè)計(jì)

采用DFT策略提高RISC_CPU的性能設(shè)計(jì)

評(píng)論