在轉換器領域,不能不提GSPS ADC—也稱RF ADC。關于使用RF ADC的優勢,以及如何使用它們進行設計并以高的速率捕獲數據,人們進行了大量的討論。但是,人們似乎忘了一件事情,即低直流信號。

高性能ADC之前的輸入配置或者前端設計,對于實現所需的系統性能非常關鍵。通常重點在于捕獲寬帶頻率,例如大于1 GHz的寬帶頻率。然而,在某些應用中,也需要直流或近直流信號,并且受到最終用戶的歡迎,因為它們也可以傳輸重要信息。因此,通過優化整體前端設計來捕獲直流和寬帶信號需要直流耦合前端,該直流耦合前端一直連接到高速轉換器。 考慮到應用的本質,將需要開發一個有源前端設計,因為用于將信號耦合到轉換器的無源前端和巴倫本身就已交流耦合。接下來我們以實際系統解決方案為例,概述共模信號的重要性,以及如何正確對放大器前端進行電平轉換。

共模

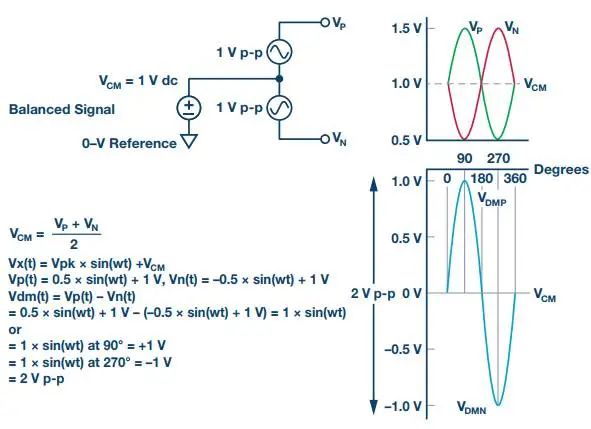

圖1顯示了轉換器如何查看差模與共模信號。CM電壓只是信號移動的中點—參見圖1。

圖1. 差模與共模信號示例

您也可以將其視為新中點或零代碼—放大器,通常通過一個VOCM引腳或類似的器件,在輸出端建立CM。不過要小心,這些引腳也有一定的電流和電壓范圍要求。最好查閱一下放大器數據手冊,并且/或者使用不會使電路內部的任何相鄰電路或基準點負荷過重的穩定偏置點。不要只是分接一個轉換器的基準電壓引腳(VREF),它通常是轉換器滿量程的一半。可能無法提供充分的高精度偏置。謹慎起見,也應查閱轉換器數據手冊上的引腳技術規格。一般而言,電阻容差1%的簡單分壓器和/或緩沖器驅動器之類,可正確設置放大器的CM偏置。

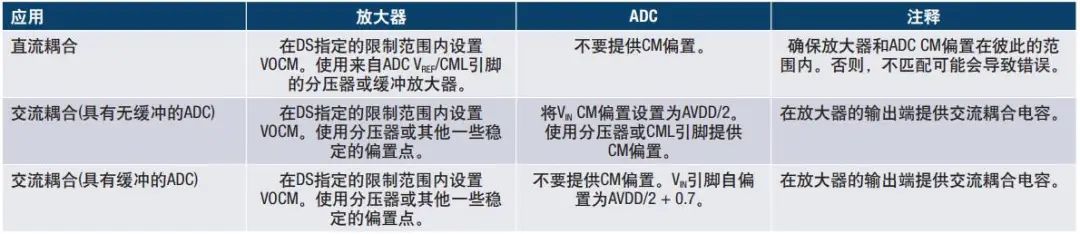

在下面表1中簡要列出了如何連接每個應用的放大器和轉換器。

表1. 共模矩陣

圖2顯示了一些正確的電路示例。

圖2. 用于放大器/轉換器前端的交流耦合與直流耦合應用示例

共模:已斷開

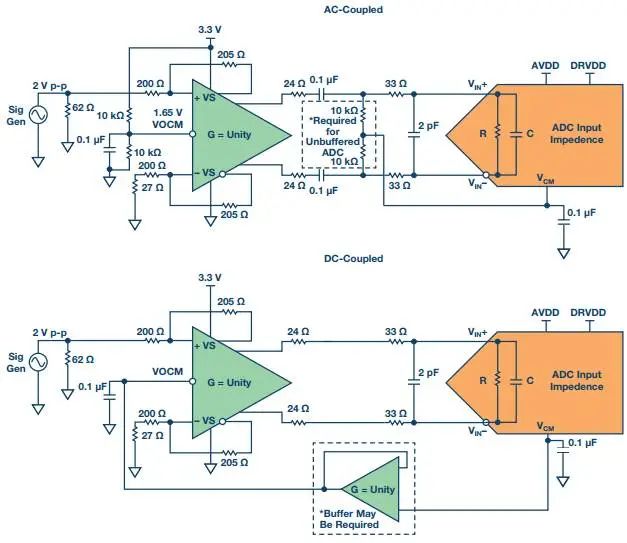

如果未提供或保持共模偏置,轉換器將產生增益和失調誤差,使獲取的總體測量性能下降。簡單地說—轉換器輸出將如圖3所示,或者略有變化。

圖3. 放大器和轉換器之間的CM不匹配

輸出頻譜的形態將與過載滿量程輸入相似。這意味著轉換器的零點偏離中心,不是最優。你可能會發現轉換器會較早削波或者達不到轉換器的滿量程。但是,由于轉換器開始使用1.8 V電源和更低的電源,這一問題變得更為嚴重。這意味著模擬輸入的CM偏置為0.9 V或AVDD/2。并非所有的單電源放大器都支持這樣的低共模電壓,同時還保持相對較好的性能。

但是,并不是任何舊款放大器都能使用,因為裕量可能非常受限,并且內部晶體管可能會開始塌陷。如果將雙電源與放大器配合使用,大多數情況下應該會有充足的裕量來實現適當的CM偏置。缺點是增加了一個額外的電源—可能不標準的負電源,這意味著更多的器件和更高的成本。簡單的反相器電路有助于解決這一問題。

將器件連接起來

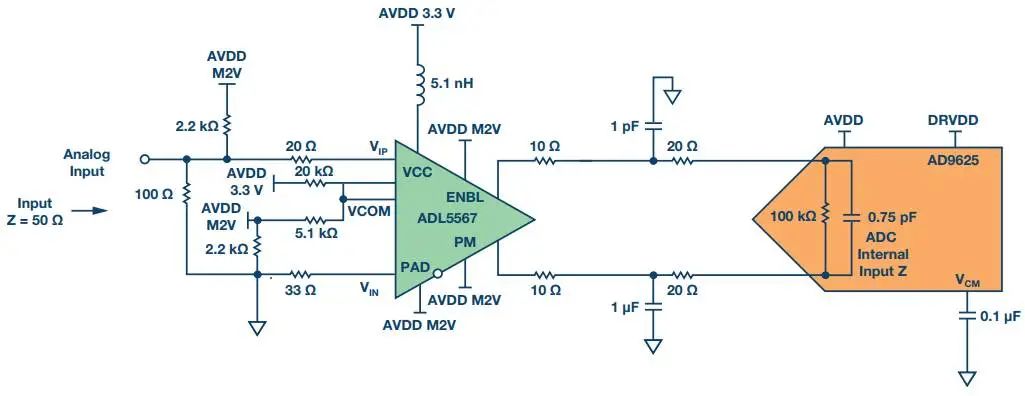

了解共模和直流耦合之后,我們可以開始組建信號解決方案。例如,ADL5567是雙通道差分放大器,增益為20 dB。它具有4.8 GHz帶寬,適合連接GSPS ADC,例如AD9625,這是12位、2.5 GSPS轉換器,具有JESD204B 8通道接口。圖4所示為整體設置框圖。

圖4. 直流到WB 放大器/轉換器信號鏈示例

在顯示的該配置中,前端接口針對寬帶采樣進行了優化,同時保留信號的直流成分。由于器件為+5.5 V耐壓。該設計使用+3.3 V 和?2 V AVDD 分離電源。這使得放大器的輸出端和ADC的輸入端之間共模簡單對齊,兩者均需在AIN+和AIN?保持+0.525 V。同樣,注意幾個接地使能的放大器引腳功能(VSS),單電源現強制設置為?2 V供電(新VSS)。

CM電壓輸出很簡單,但是弄清楚放大器輸入的共模需求可能有點麻煩。需要為接口做兩件事:

1

輸入端CM電壓需要配置為0 V,否則,驅動放大器失調將使輸出軌偏向一側。這將導致圖3所描述的性能問題或更嚴重,—將出現放大器和轉換器信號鏈交流性能不佳。為此,放大器輸入端的每一側都需要允許電流流向地面,或該直流耦合案例中2 V。因此,在每個放大器輸入端添加2.2 k?的電阻來抑制失調電流。

工作原理:放大器輸出約為0.525 V,放大器輸入CM電壓為0 V。具有500 ?的內部反饋電阻和約50 ?的輸入電阻使得它看起來有550 ?;或在本例中,我們假設一個50 ?源電阻與100 ?電阻并聯,得到33 ?。再串聯20 ?增加到53 ?。這是串聯了500 ?內部反饋電阻或總計553 ?。也就是形成了500 ?和53 ?的0.525 V電阻分壓器。反過來,產生了900 μA (或0.525/553)的電流。為將此分流至地面或新VSS或?2 V,添加2.2 k?電阻或?2 V/2.2 k? = 900 μA。

2

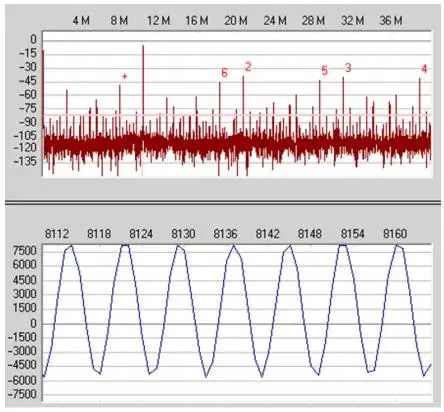

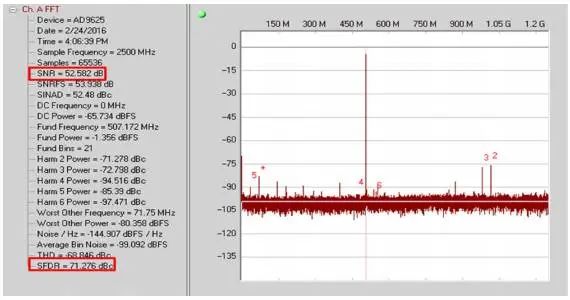

輸入為單端輸入且需要適當配置來保持最佳性能,同時維持較低偶數階失真。同樣,100 ?與50 ?源電阻有效并聯,得到33.33 ?戴維南等效電阻,如前所述。這通常又會反映在VIN節點上,來平衡設備的輸入,因為它是單端驅動的。但是,為了改善偶數階失真,VIN+節點上的20 ?用于保持所有寬帶頻率的低失真。這通過使用特定中頻約500 MHz完成,—或參見圖 5 測試示例。

圖5. 典型FFT性能@ 507 MHz AIN @ 2500 MSPS

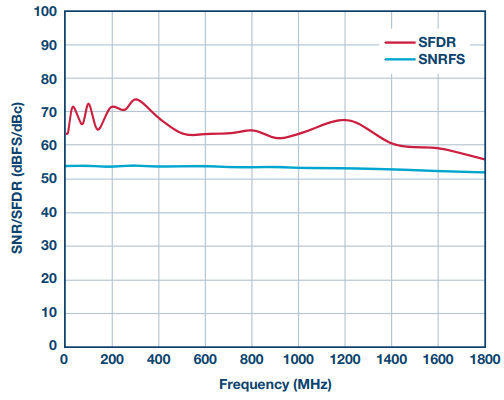

由于它是一個迭代的過程,所以會有些乏味。圖6中所示為信號鏈設計中最高2 GHz輸入頻率的典型交流頻率掃描性能。

圖6. 典型交流頻率掃描性能@ 2500 MSPS

值得注意的是,添加了5.1 nH電感與電源的正供電軌輸入串聯。這有助于通過捕捉和再循環放大器內部的這些不平衡電流來再次提高偶數階線性度性能與頻率。

最后,需要針對放大器和ADC之間的前端BW優化接口。這通常也以迭代的方式完成。但是,對于兩個IC之間某些值的設置有幾點需注意。為了在接口中獲得最佳BW,請遵循以下規則——

根據經驗和/或ADC數據手冊建議,選擇一個反沖電阻器(RKB),(本例中為?),通常介于5 ?和36 ?之間。

選擇放大器外部串聯電阻(RA)。如果放大器差分輸出阻抗在100 ?至200 ?范圍內,RA應小于10 ?。如果放大器輸出阻抗為12 ?或更低,RA應介于5 ?和36 ?之間。此時,為ADL5567選擇10 ?串聯電阻和阻抗為10 ?的差分輸出。

放大器輸出的串聯與并聯總電阻應與放大器的表征負載(RL)接近。這里,圖4電路中為160 ?,或2 RA + 2 RKB + RADC = 20 +40 + 100。ADL5567具有200 ?的RL,所以如果設計值偏離放大器的RL特性值太多,線性度性能可能出現偏差。

將內部ADC電容CADC添加至10 ?串聯電阻后的并聯電容,來幫助完成內部ADC采樣網絡反沖。這也提供了軟低通濾波來減少任何折回帶內的寬帶諧波。

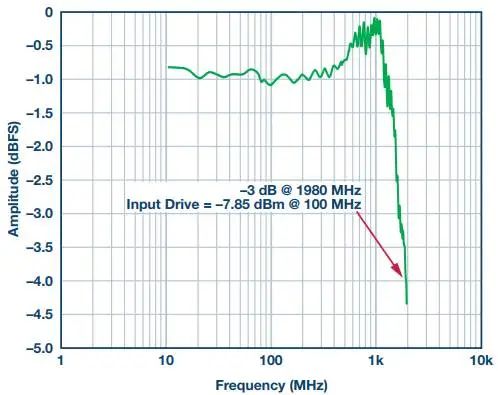

使用上述標準開發出2 GHz通帶平坦度響應產品,以捕捉1st和2nd奈奎斯特區內的頻率,假設采樣速率為2.5 GSPS。該設計的輸入驅動規格將為?8 dBm或252 mV p-p,假設在100 MHz基準頻率下具有50 ?輸入阻抗。這是放大器輸入要求轉換器達到滿量程的輸入滿量程電平。

圖7. 典型通帶平坦度性能和輸入驅動電平

在任何直流耦合設計中,忽略轉換器的共模輸入電壓規格均可引起嚴重問題。如果使用了多個級別,信號鏈中的共模水平必須保持一致,以防止兩個組件相互沖突。如果未正確耦合,其中一個將經常在各級間取勝,產生虛假測量。對于交流耦合應用,需在兩級之間使用一個耦合電容來打破這種共模不匹配。這樣設計才能夠優化放大器輸出和ADC輸入的偏置。否則,系統設計中需考慮雙電源或電平轉換電路,如以上直流耦合設計中的描述。

責任編輯:lq

-

轉換器

+關注

關注

27文章

8703瀏覽量

147175 -

模擬信號

+關注

關注

8文章

1130瀏覽量

52463 -

共模信號

+關注

關注

1文章

85瀏覽量

14158

原文標題:從直流到寬帶,模擬信號鏈設計不可忽略的“共模”

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

運算放大器和普通放大器的區別

前級放大器作用與功能

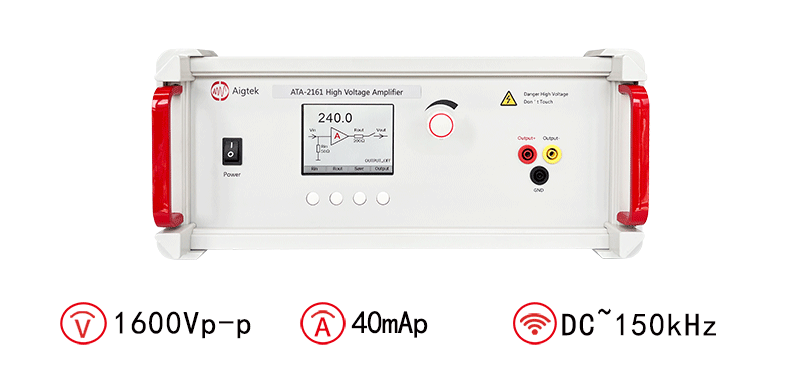

安泰功率放大器怎么用

同相放大器和鎖相放大器的區別

交流放大器可以放大直流信號嗎

c類放大器效率怎么算

什么是放大器?

如何正確對放大器前端進行電平轉換

如何正確對放大器前端進行電平轉換

評論