opensbi下的riscv64裸機編程2(中斷與異常)

1.本文說明

2.riscv特權模式下的異常

2.1 CSPs

2.2 異常開關的寄存器

2.3 與中斷相關的指令

3.中斷測試

3.1 設置中斷向量表

3.2 開啟中斷設置

3.3 初始化timer

3.4 開啟中斷

3.5 中斷處理

4.測試及校驗

5.總結

1.本文說明

任何時候,中斷和異常的產生都是十分值得關注的,這些將破壞程序原有的執行邏輯。按照芯片的設計來說,中斷和異常大致上可以分為三類異常(Exception)、陷入(Trap)、外部中斷(Interrupt)。

異常(Exception)

在一條指令執行的過程中發生了錯誤,可以通過異常處理函數進行處理,最常見的異常包括無效的內存地址訪問、非法指令異常、缺頁異常等等。當發生這些異常后可以進行處理。

陷入(Trap)

主動的讓其進入異常處理函數,常見的是系統調用syscall。而在riscv上為ecall或者進入斷點的ebreak。

外部中斷(Interrupt)

一般由外部事件觸發,比如定時器中斷、GPIO中斷等。這些異常是不可預知的。

對于一般的中斷處理流程,進入中斷后需要進行上下文的保存與恢復。

2.riscv特權模式下的異常

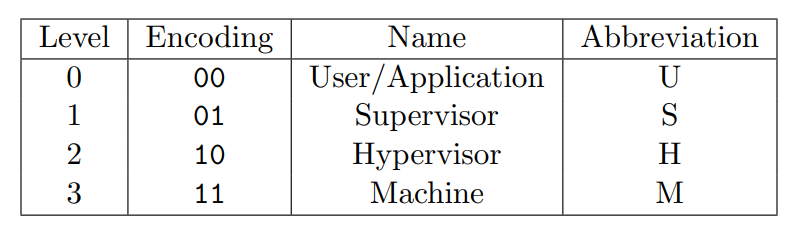

涉及到中斷和異常,RISCV的特權模式是不能繞開的。在RISCV中,無論在任何模式發生的異常,硬件線程都會將控制權交給M-Mode的異常處理程序。然而對于類Unix的操作系統來說,異常都是由操作系統來處理。而操著系統運行的模式是S-Mode,所以RISCV也可以選擇將異常重新導向到S-Mode,也支持異常委托機制(Machine Interrupt Delegaintion)將異常直接通過S-Mode進行處理,這樣可以大大的增加操作系統的靈活性。

一般來說M-Mode是必須實現的,S-Mode也一般會有,而U-Mode是選擇性擴展的。目前的RISCV芯片中例如蜂鳥的E203與K210都只支持了RISCV架構中的Machine Mode。

2.1 CSPs

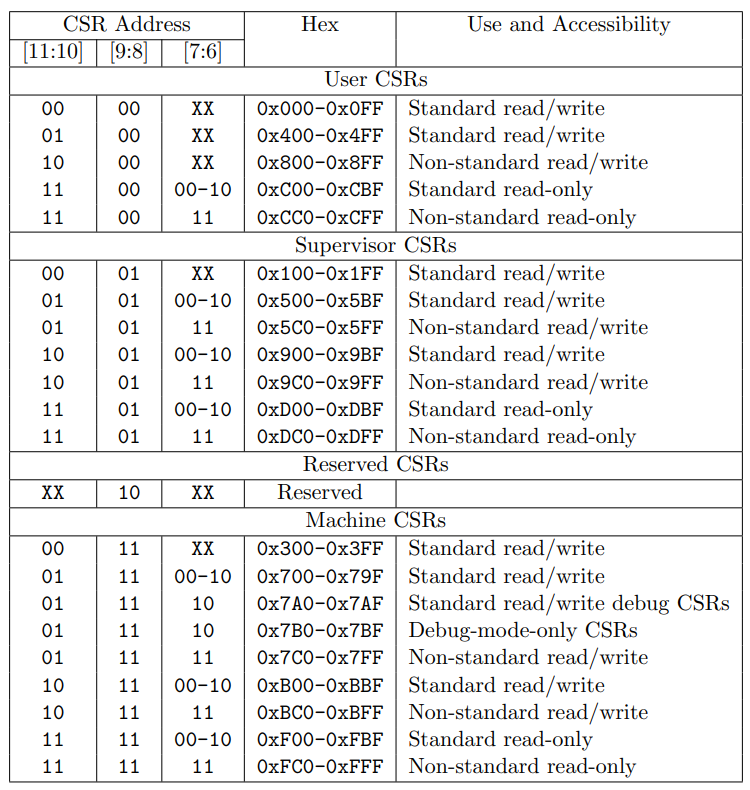

實際上RISCV在實現系統指令集的時候,是支持多種模式的擴展的,這一系列的指令集通過Control and Status Registers (CSRs)來進行控制。

CSR地址是擴展了12位,也就是可以設計最大4096個指令。

通過下面的網站可以看到當前CSRs的實現狀態。

http://www.five-embeddev.com/quickref/csrs.html

這里只針對S-Mode下的異常處理進行分析,M-Mode下的異常處理類似。

| Name | Number | Feature/Extensions | Description |

|---|---|---|---|

| sepc | 0x0141 | supervisor | Supervisor Exception Program Counter |

| scause | 0x0142 | supervisor | Supervisor Exception Cause |

| stval | 0x0143 | supervisor | Supervisor bad address or instruction. |

| stvec | 0x0105 | supervisor | Supervisor Trap Vector Base Address |

| sstatus | 0x0100 | supervisor | Supervisor Status |

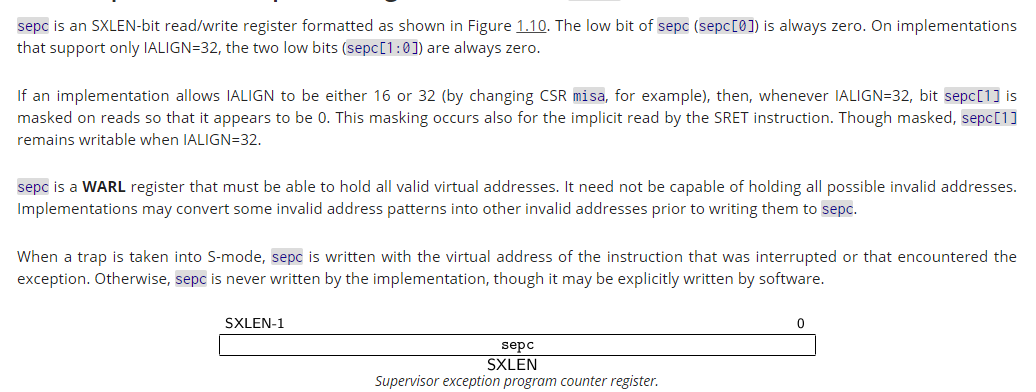

Supervisor Exception Program Counter (sepc)

當中斷發生時,存放需要跳轉的PC值。這里需要利用stvec提供中斷向量表的基地址。

該寄存器的值是在32位下是4字節對齊的。

Supervisor Cause Register (scause)

該寄存器表示中斷發生的原因。下面的表格中表述了中斷的發生原因:

| Interrupt | Exception Code | Description |

|---|---|---|

| 1 | 0 | Reserved |

| 1 | 1 | Supervisor software interrupt |

| 1 | 2–4 | Reserved |

| 1 | 5 | Supervisor timer interrupt |

| 1 | 6–8 | Reserved |

| 1 | 9 | Supervisor external interrupt |

| 1 | 10–15 | Reserved |

| 1 | ≥16 | Designated for platform use |

| 0 | 0 | Instruction address misaligned |

| 0 | 1 | Instruction access fault |

| 0 | 2 | Illegal instruction |

| 0 | 3 | Breakpoint |

| 0 | 4 | Load address misaligned |

| 0 | 5 | Load access fault |

| 0 | 6 | Store/AMO address misaligned |

| 0 | 7 | Store/AMO access fault |

| 0 | 8 | Environment call from U-mode |

| 0 | 9 | Environment call from S-mode |

| 0 | 10–11 | Reserved |

| 0 | 12 | Instruction page fault |

| 0 | 13 | Load page fault |

| 0 | 14 | Reserved |

| 0 | 15 | Store/AMO page fault |

| 0 | 16–23 | Reserved |

| 0 | 24–31 | Designated for custom use |

| 0 | 32–47 | Reserved |

| 0 | 48–63 | Designated for custom use |

| 0 | ≥64 | Reserved |

Supervisor Trap Value (stval) Register

由于scause不足以表示異常發生的所有信息,比如發生了缺頁異常,就會將stavl設置成需要訪問但是不在內存中的地址。以便于操作系統將這個地址加載進來。

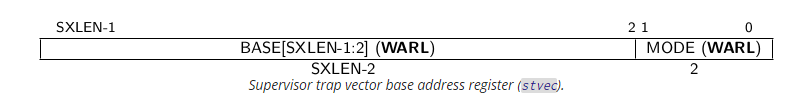

Supervisor Trap Vector Base Address Register (stvec)

設置中斷處理的基地址,同時設置模式

對于基地址的模式有如下兩種:

| Value | Name | Description |

|---|---|---|

| 0 | Direct | All exceptions set pc to BASE. |

| 1 | Vectored | Asynchronous interrupts set pc to BASE+4×cause. |

| ≥2 | — | Reserved |

Direct:顧名思義,當異常發生的時候,每次都會跳轉到這個地址,然后通過這個地址的中斷處理程序去判斷哪種中斷。

Vectored:在這種模式下,會跳轉到BASE + 4 * cause 進行處理流程。每種異常的cause都不一樣。

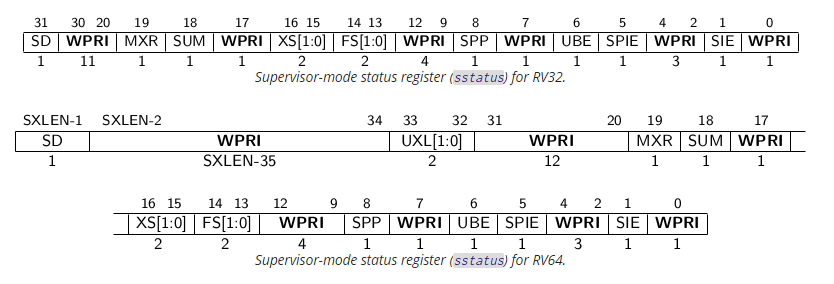

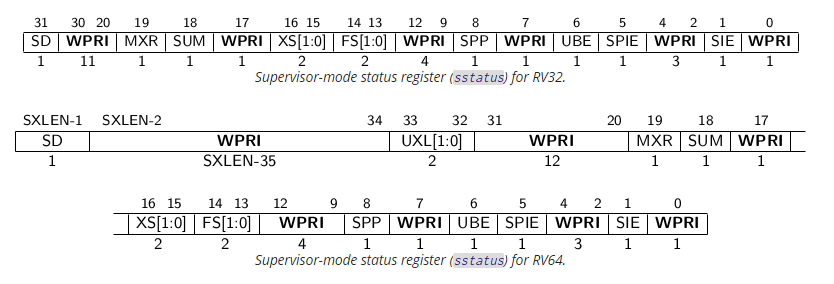

Supervisor Status Register (sstatus)

控制中斷的狀態等等,也可以控制全局中斷的時能等等。

SIE域表示全局中斷使能。當該MIE域值為1時,表示所有中斷的全局開關打開,當MIE域的值為0時候,表示全局關閉所有中斷。

SPIE用于保存進入異常之前MIE域的值。

2.2 異常開關的寄存器

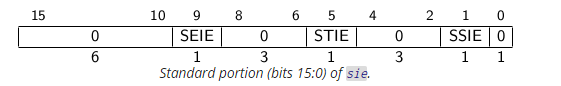

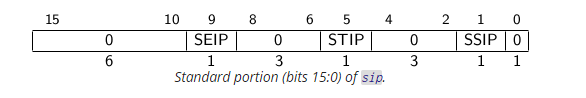

對于S-Mode中斷的Enable與Pending,還需要關注兩個寄存器。sie與sip。

Supervisor Interrupt Enable(sie)

Supervisor Interrupt Pending(sip)

可以看到有三種類型的中斷,由芯片廠家進行自定義設計。

Supervisor software interrupt

Supervisor timer interrupt

Supervisor external interrupt

2.3 與中斷相關的指令

CSR Read Write(csrrw)

csrrw dst, csr, src:將指定的CSR寄存器寫入dst,同時將src的值寫入CSR。

CSR Read(csrr)

csrr dst,csr:讀一個CSR寄存器到dst。

CSR Clear(csrc)

csrc(i) csr, rs1:將指定的位清零。

CSR Set(csrs)

csrs(i) csr, rs1:將指定的位置一。

3.中斷測試

由于在qemu上,中斷的產生可以通過定時器來發生,所以需要理解riscv上對timer的使用。timer又需要通過sbi的接口進行訪問。

相關的代碼文件可以參考:

https://github.com/bigmagic123/riscv64_opensbi_baremetal/tree/master/03_interrupt

已經實現了timer中斷的產生過程。

3.1 設置中斷向量表

本程序需要設置中斷向量表,前面提到過,中斷向量的跳轉有兩種模式:Direct與Vectored。Direct可以直接轉到固定的pc地址,然后由統一的入口進行處理,這種比較容易實現,所以設置為這種模式。

.globaltable_val_set table_val_set: lat0,trap_entry csrwstvec,t0 jrra

直接將trap_entry函數的入口寫到stvec的寄存器中。由于函數地址4字節對其,所以設置后模式為Direct。

3.2 開啟中斷設置

要開啟時鐘中斷,這樣才能產生時鐘,而根據手冊,開啟時鐘中斷實際上是設置Supervisor Interrupt Enable(sie),也就是設置SIE的寄存器開啟。

所以只需要設置即可。

voidenable_timer_interrupt(void) { w_sie(r_sie()|SIE_STIE); }

3.3 初始化timer

對于timer的填充,其實就是設置中斷的值。當timer達到設定的值后會產生中斷。

voidset_timer(uint64stime_value) { SBI_TIMER(stime_value); } //getcurrenttime uint64get_cycle() { returnr_time(); } voidclock_set_next_event() { set_timer(get_cycle()+TIMEBASE); }

函數填充了下一個tick的值。

3.4 開啟中斷

中斷的開啟通過sstatus全局的狀態寄存器設置。

通過設置SIE位就可以達到使能或者關閉中斷的作用。

voidinterrupt_enable(void) { w_sstatus(r_sstatus()|SSTATUS_SIE); }

3.5 中斷處理

中斷處理需要保存當前的上下文寄存器(寄存器壓棧操作),然后跳轉到中斷處理函數去處理具體的中斷。當處理完成之后返回現場(寄存器出棧)。

這里先不做這么復雜的工作,中斷產生后直接跳轉到中斷處理函數中,只執行一次。

.globaltrap_entry trap_entry: csrra0,scause csrrca1,stval,zero csrra2,sepc mva3,s0 /*scause,stval,sepc,sp*/ callhandle_trap

其中a0為第一個參數,保存中斷發生的原因。

a1是中斷發生的具體信息。

a2表示了中斷異常返回值。

然后進入hande_trap。

uintptr_thandle_trap(uintptr_tscause,uintptr_tstval,uintptr_tsepc,uintptr_tsp) { tfp_printf("handle_trap%08lx:%08lx:%08lx:%08lx ",scause,stval,sepc,sp); while(1); return0; }

4.測試及校驗

因為工程文件的增加,所以使用了Makefile進行工程的構建工作。

%.o:%.c%.s $(CC)$(CFLAGS)-c$

Makefile的語法規則基本

TARGET…:DEPENDENCIES… COMMAND

這里也不過多的涉及了。

輸入make后,在fw_bin目錄下執行run.sh腳本即可。

最后可以看到中斷的原因

最高位是8,相應的中斷描述為Supervisor timer interrupt。

5.總結

riscv的異常和中斷的處理模式在M-Mode或者S-Mode下都可以設計,具體要看芯片的設計方式,如果設計在M-Mode,對于操作系統來說,可以通過轉發或者代理給S-Mode的操作系統,如果S-Mode存在中斷處理,那么處于S-Mode的系統可以直接處理,這樣比較簡潔。

責任編輯:xj

原文標題:opensbi下的riscv64裸機編程2(中斷與異常)

文章出處:【微信公眾號:嵌入式IoT】歡迎添加關注!文章轉載請注明出處。

-

編程

+關注

關注

88文章

3616瀏覽量

93752 -

裸機

+關注

關注

0文章

39瀏覽量

6379 -

RISC-V

+關注

關注

45文章

2283瀏覽量

46174

原文標題:opensbi下的riscv64裸機編程2(中斷與異常)

文章出處:【微信號:Embeded_IoT,微信公眾號:嵌入式IoT】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何快速入門HAL庫編程 HAL庫與裸機編程的比較

【「RISC-V體系結構編程與實踐」閱讀體驗】-- SBI及NEMU環境

ARM處理器的異常中斷響應過程

freertos和裸機有什么區別

嵌入式C編程常用的異常錯誤處理

在ubuntu 24.04下嘗試使用riscv64-linux-musleabi_for_x86_64-pc-linux-gnu工具鏈編譯cv1800大核出現報錯的原因?

谷歌安卓系統即將取消對RISC-V架構的支持

RISCV soft JTAG調試_v1.2

全志D1s開發板裸機開發之壞境搭建

RISCV soft JTAG調試_v1.1

聊聊KUKA機器人高級編程:中斷

opensbi下的riscv64裸機編程:中斷與異常

opensbi下的riscv64裸機編程:中斷與異常

評論