2020年6月15日至18日(美國時間,第二天為日本時間)舉行了“ 2020年技術與電路專題討論會(VLSI 2020年專題討論會)”,但實際上所有的講座錄了視頻,并可付費觀看至2020年8月底。 如果像過去那樣在酒店場所召開會議,則您只能參加眾多平行會議中的一個會議。但是以視頻點播形式,您可以根據需要觀看所用會議。這樣做需要花很長時間,因此應許多與會者的要求,付費會議注冊者的視頻觀看時間已經延長了大約兩個月,直到8月底。 在這個VLSI研討會中,共有86個工藝研討會,110個電路研討會,總共約200篇論文。本次技術研討會上,與內存相關的會議是最多的,并且針對每種存儲器類型(例如NAND / NOR / PCM,RRAM,RRAM,FeRAM,STT MRAM和下一代MRAM)均舉行了會議,覆蓋先進器件/工藝,先進Si CMOS,先進工藝,Ge/SiGe器件,用于量子計算的器件以及新器件領域。除此之外,與3D堆疊封裝相關的還有3個會議。 接下來,我想在這大約200個演講中,挑選并介紹一些受到高度贊揚的論文和演講。首先,我要介紹是比利時IMEC的BPR工藝,其次是法國Leti和IBM關于先進CMOS技術領域的演講。

IMEC針對5nm及以下尖端工藝的BPR技術

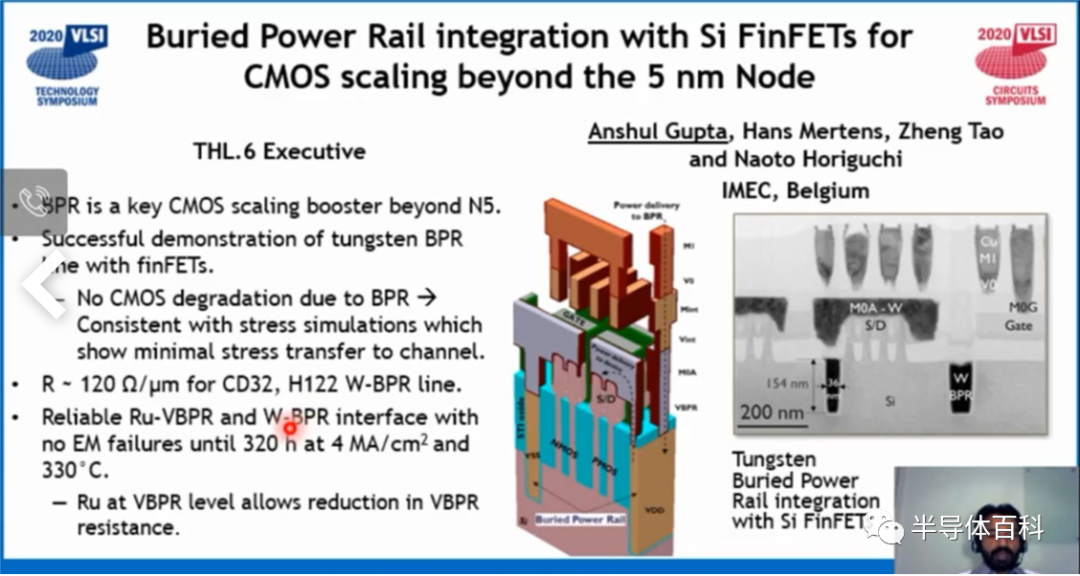

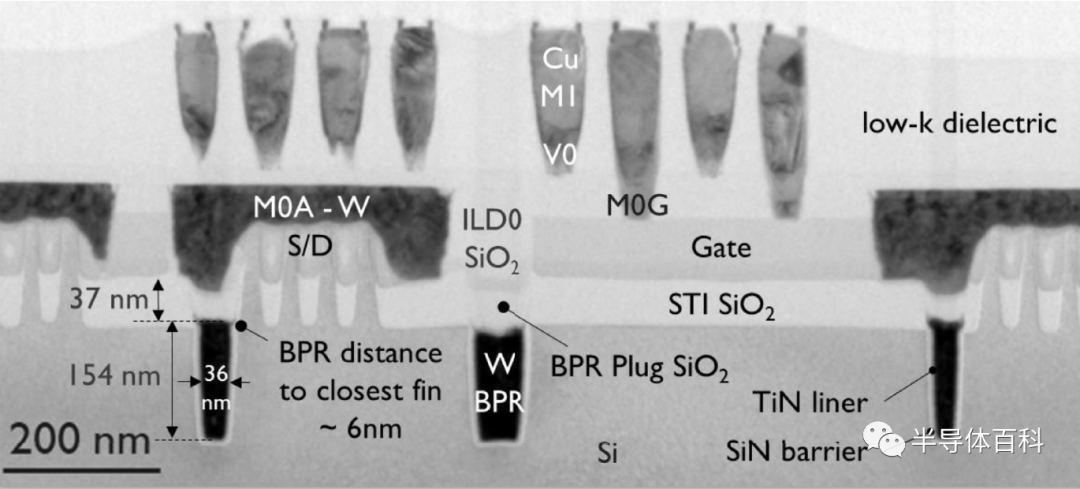

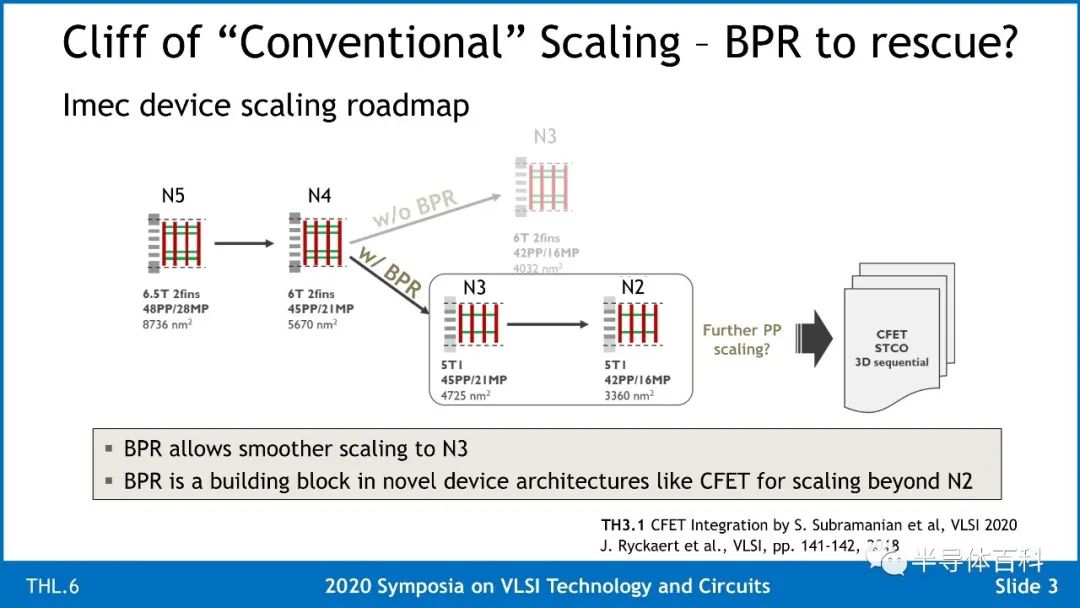

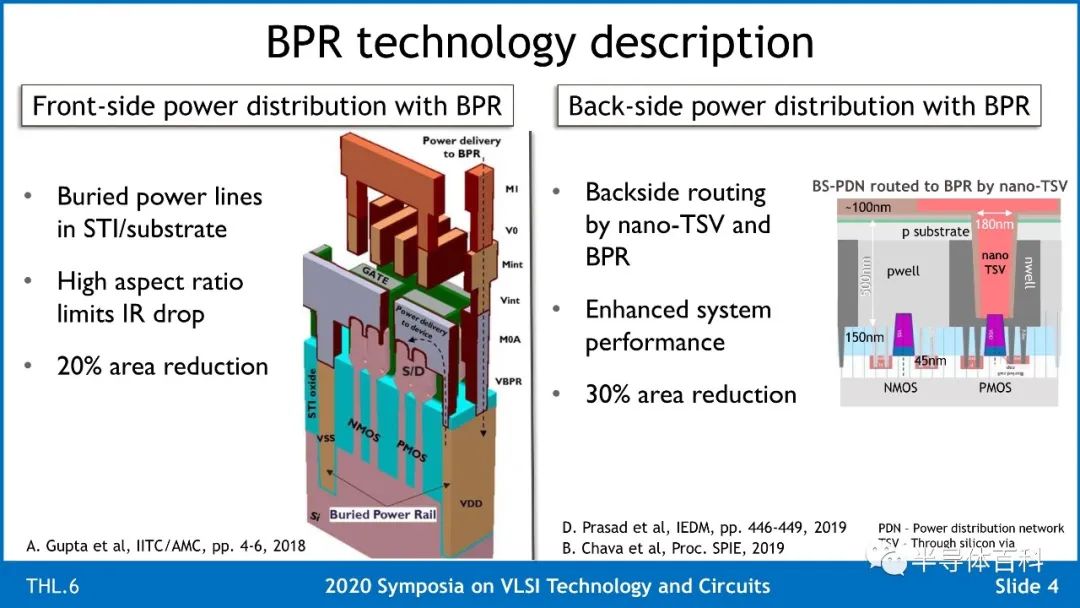

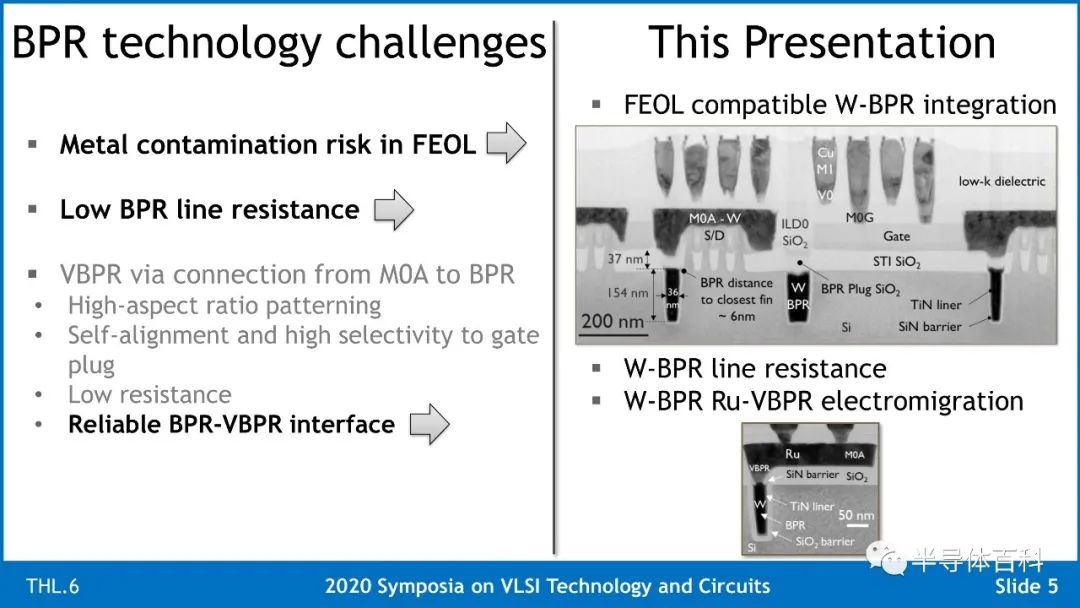

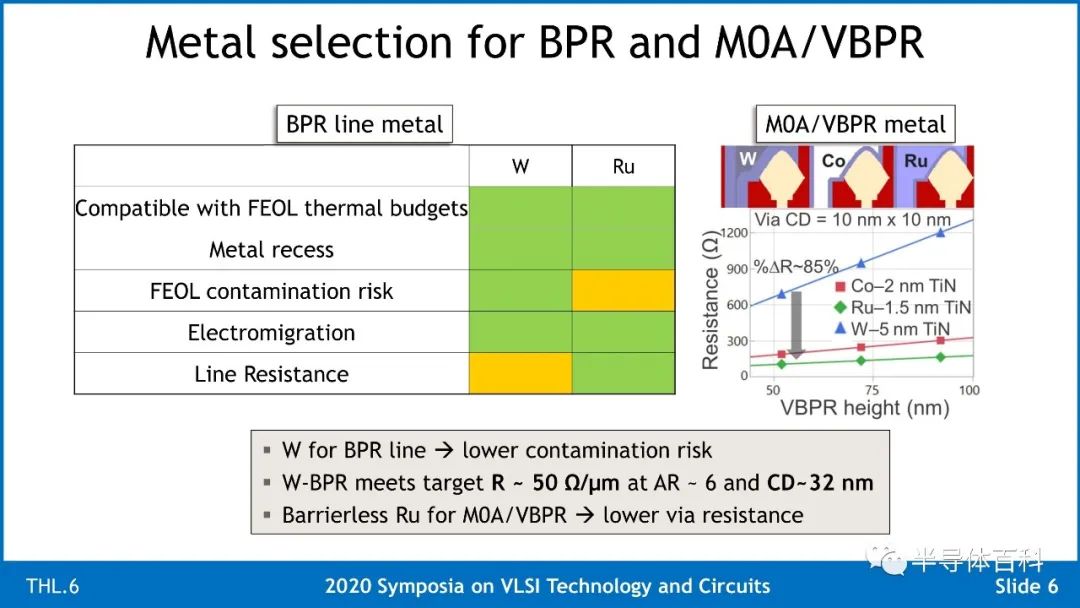

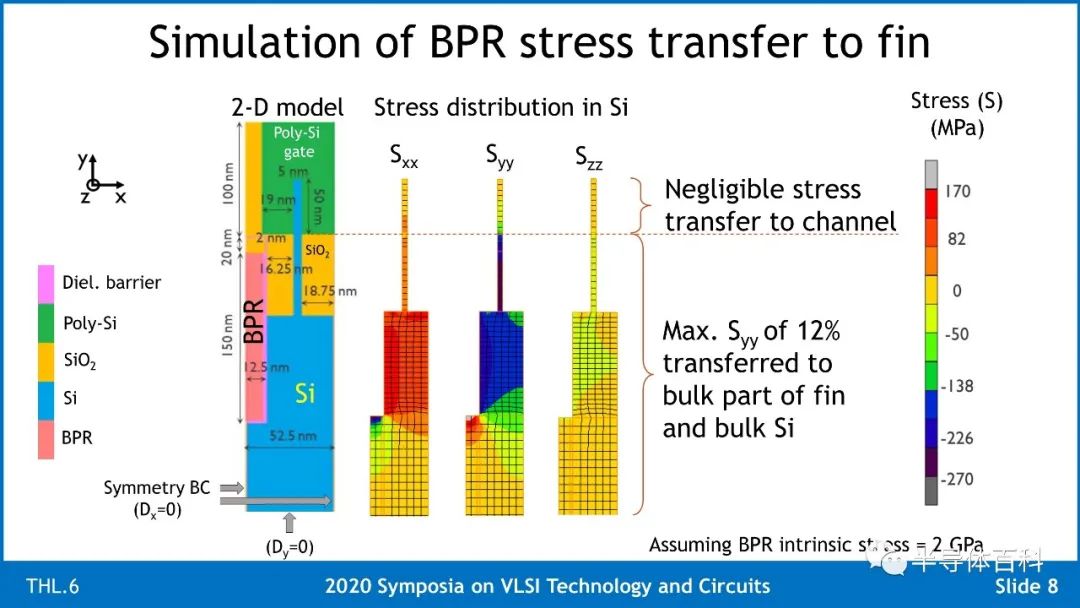

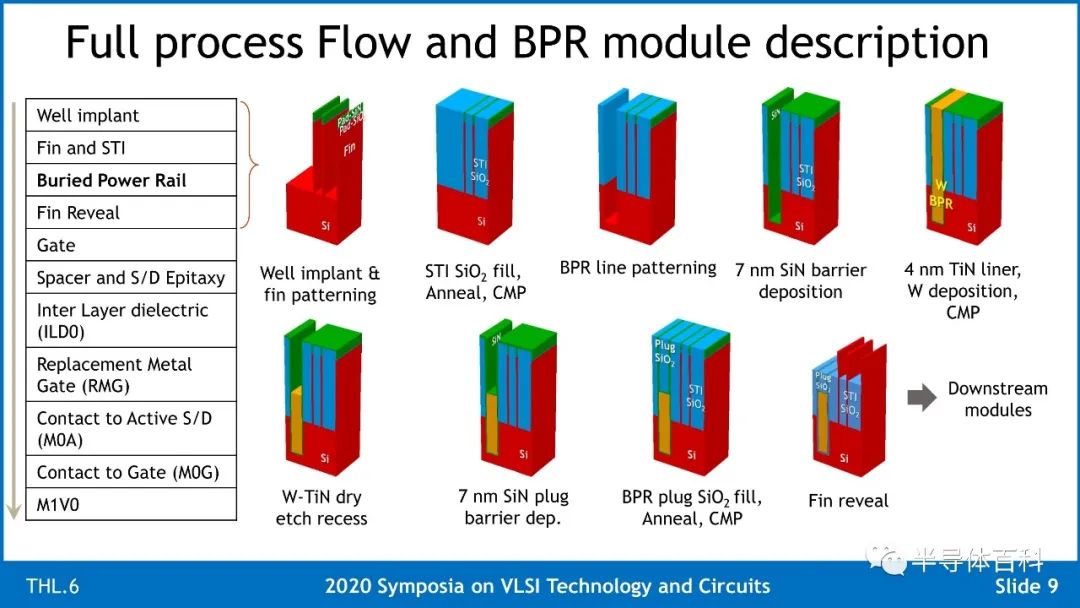

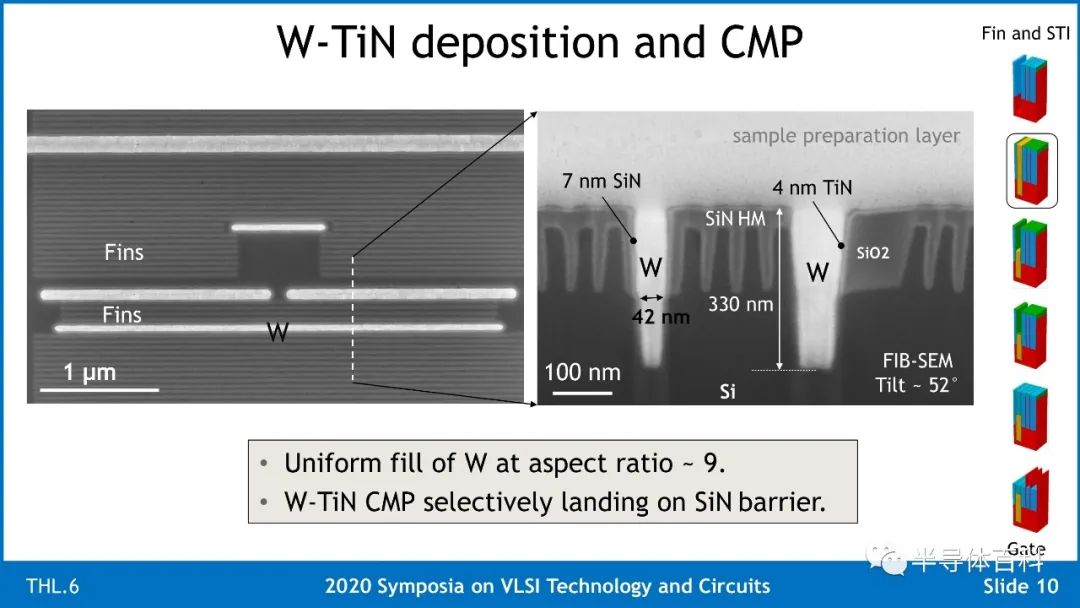

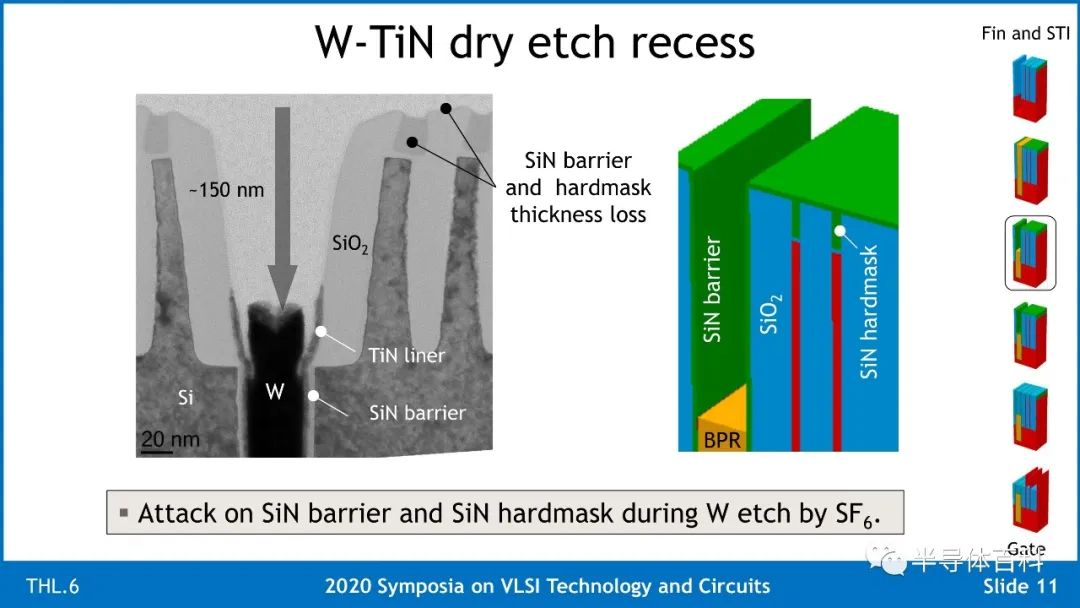

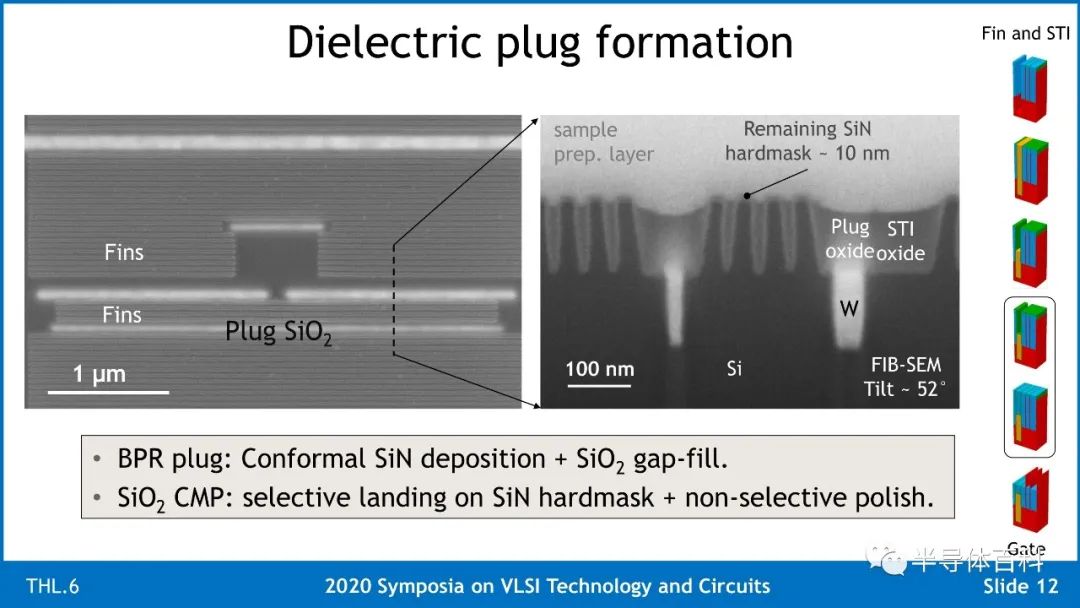

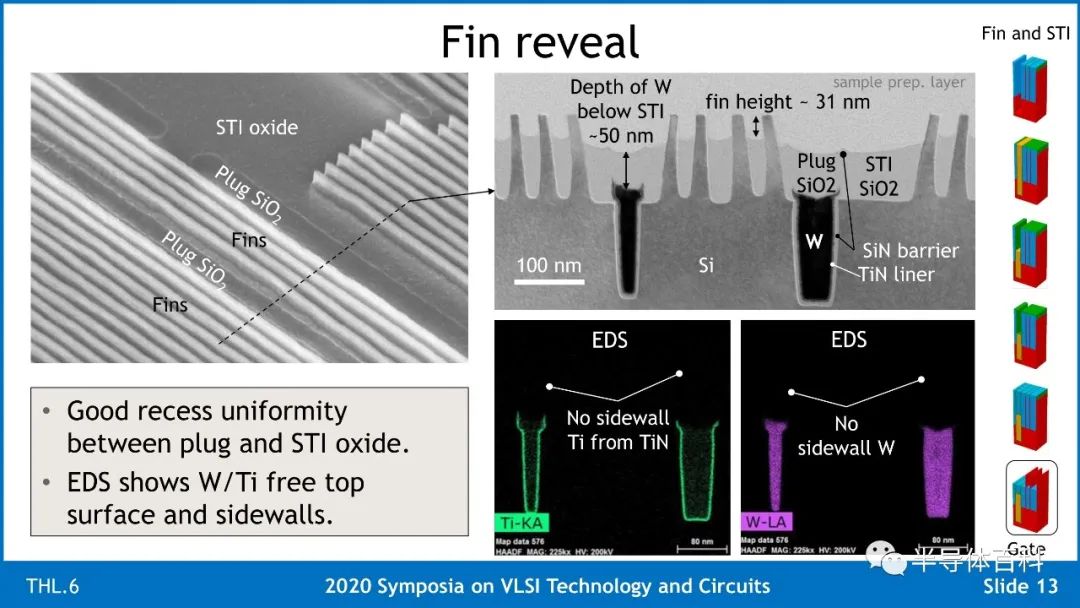

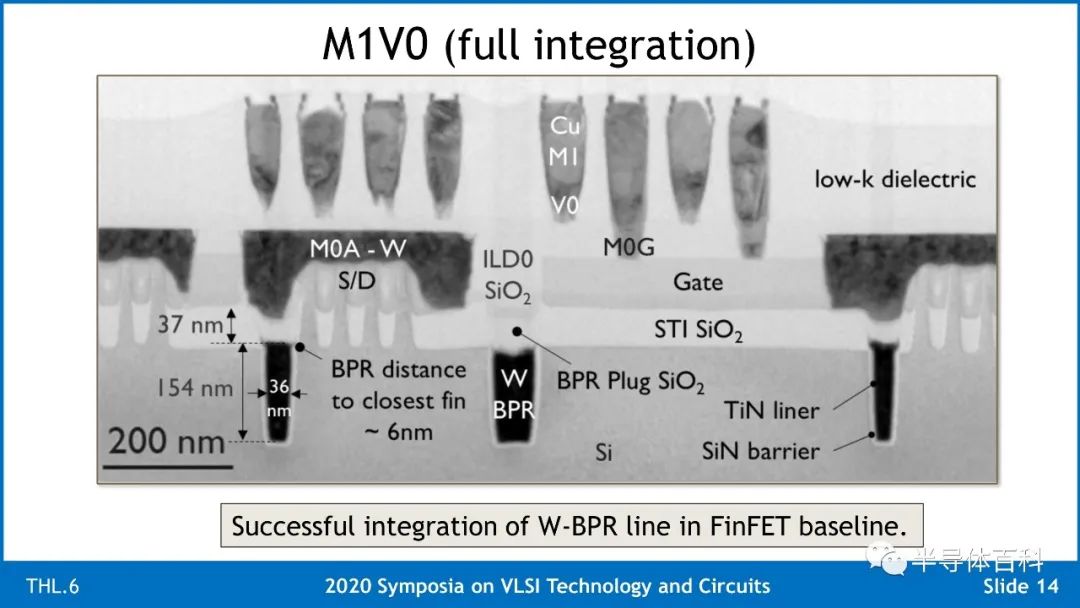

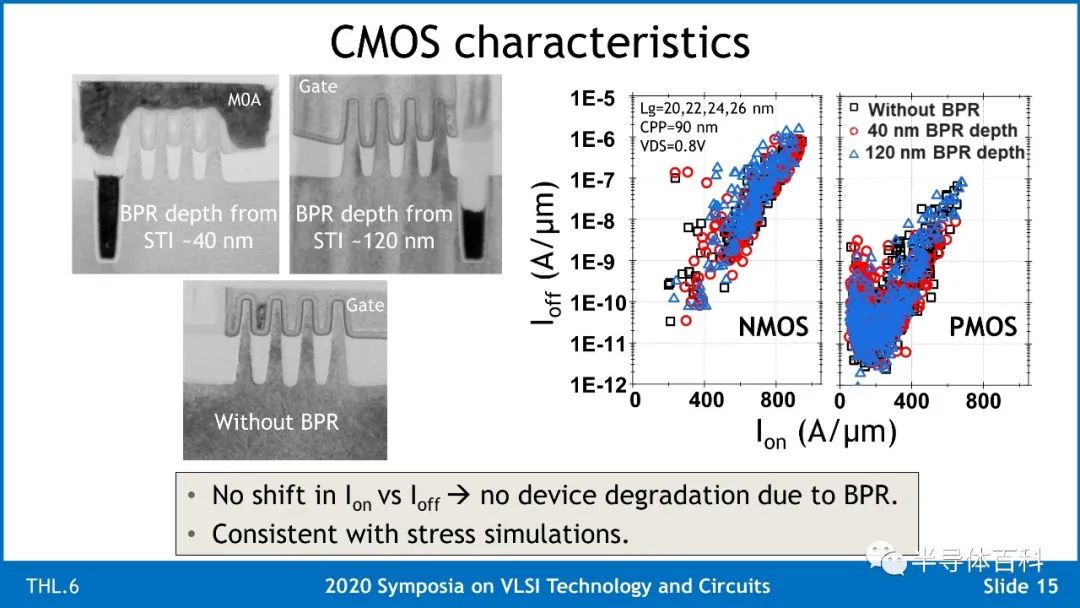

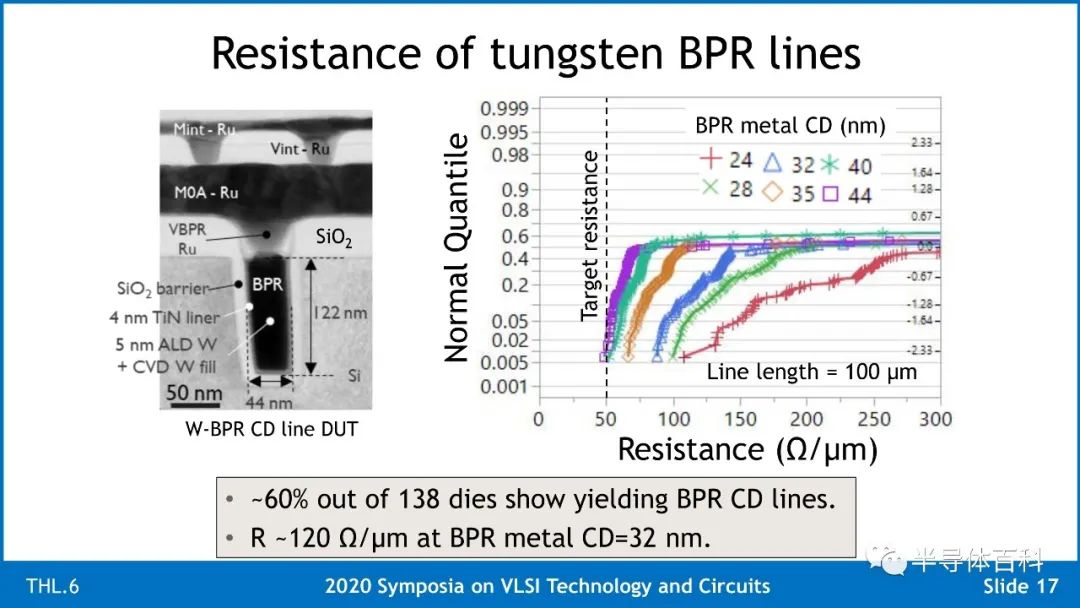

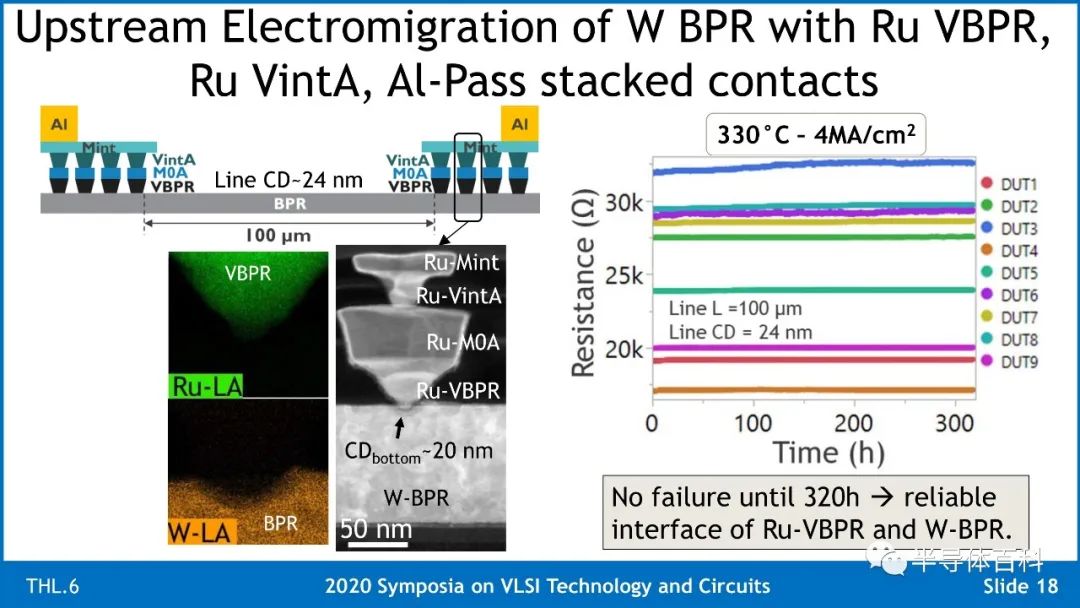

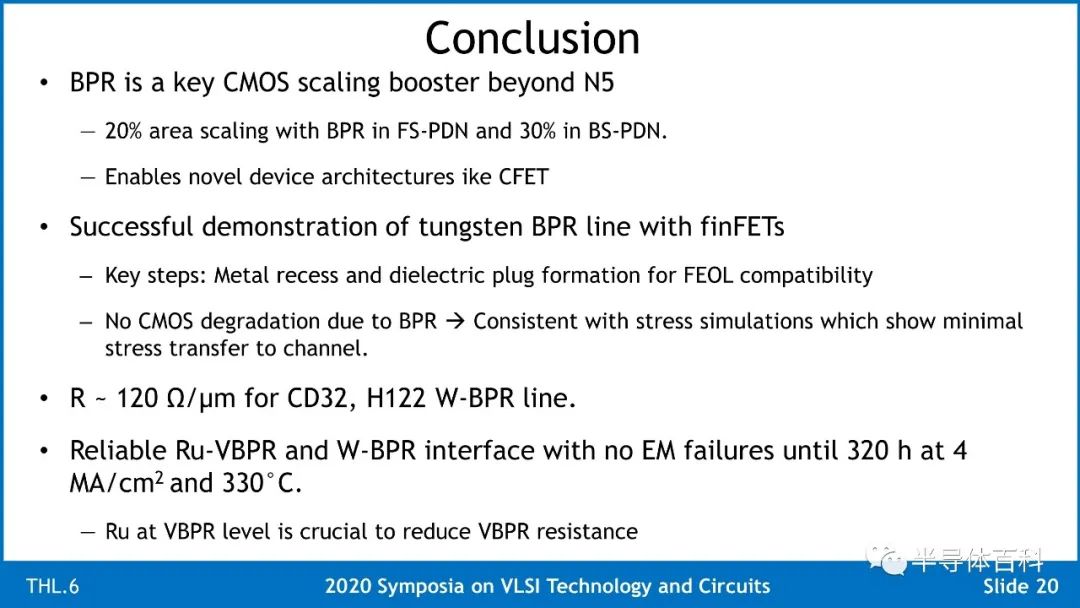

比利時獨立研究機構imec的研究人員報告了在FinFET工藝中添加埋入式電源線(BPR)的實驗成果。該項技術被定位為5納米及以下制程的重要技術。他們采用鎢作為該電源線的材料,并且已經證實該技術對晶體管性能沒有影響。 此外,通過將釕(Ru)用于連接到埋入鎢的布線的通孔,還證實了其在4 MA /cm2和330℃的條件下承受320小時以上的電遷移應力,以此說明釕是該技術最優選的候選材料。

圖1,IMEC現場演示文稿截圖

圖2,BRP的TEM圖,其中鰭節距為45 nm,鰭與BPR之間的最小距離約為6 nm

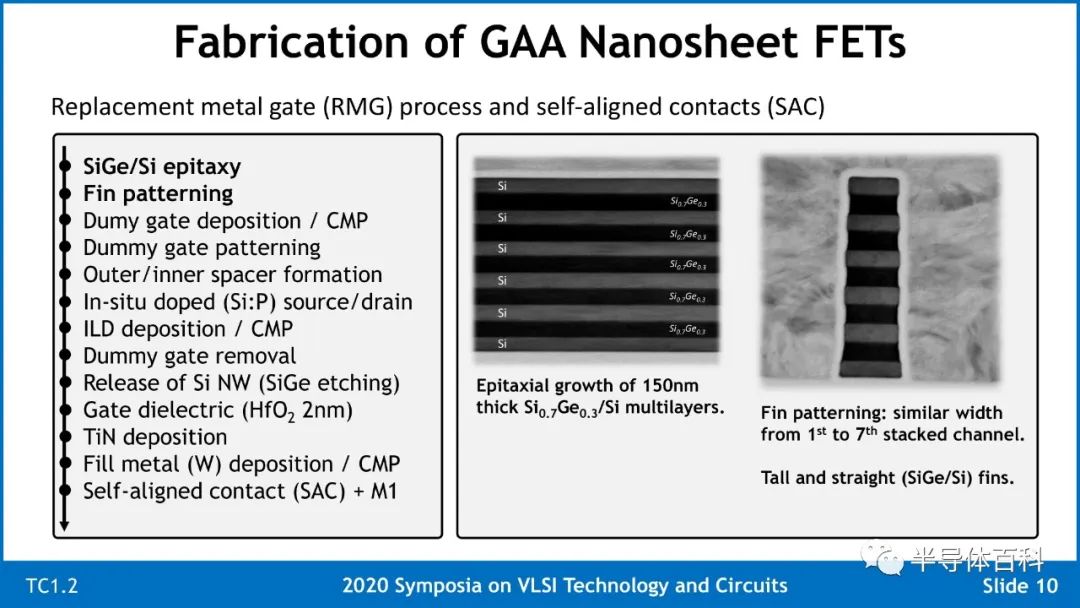

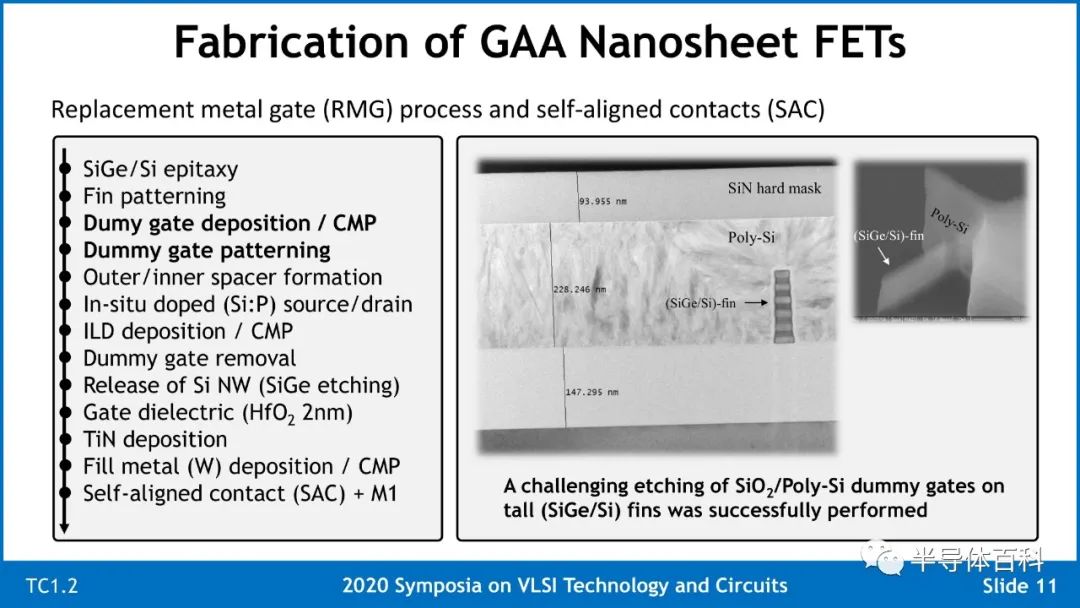

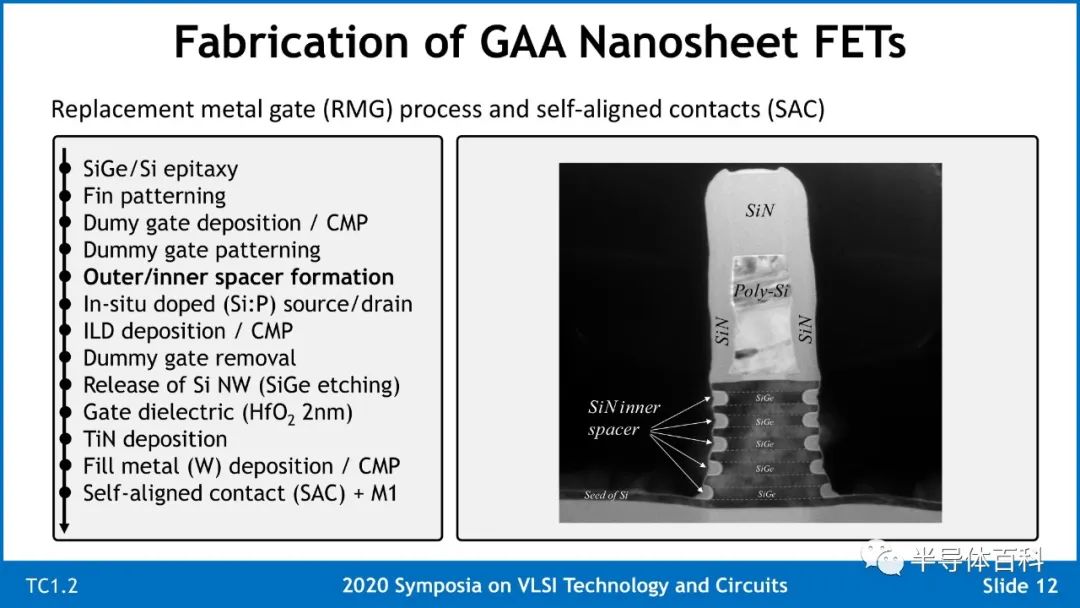

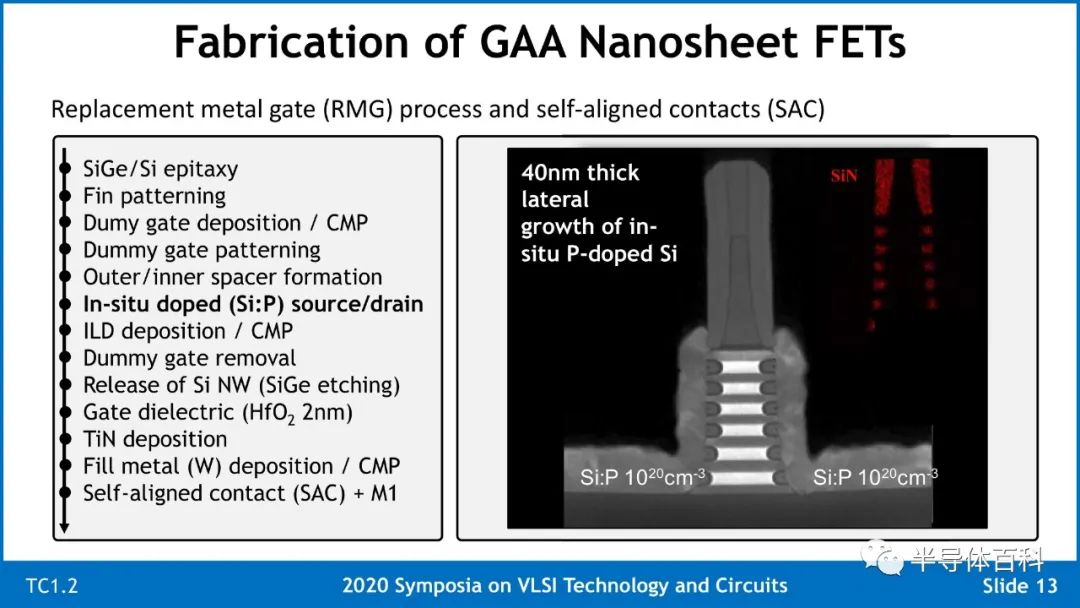

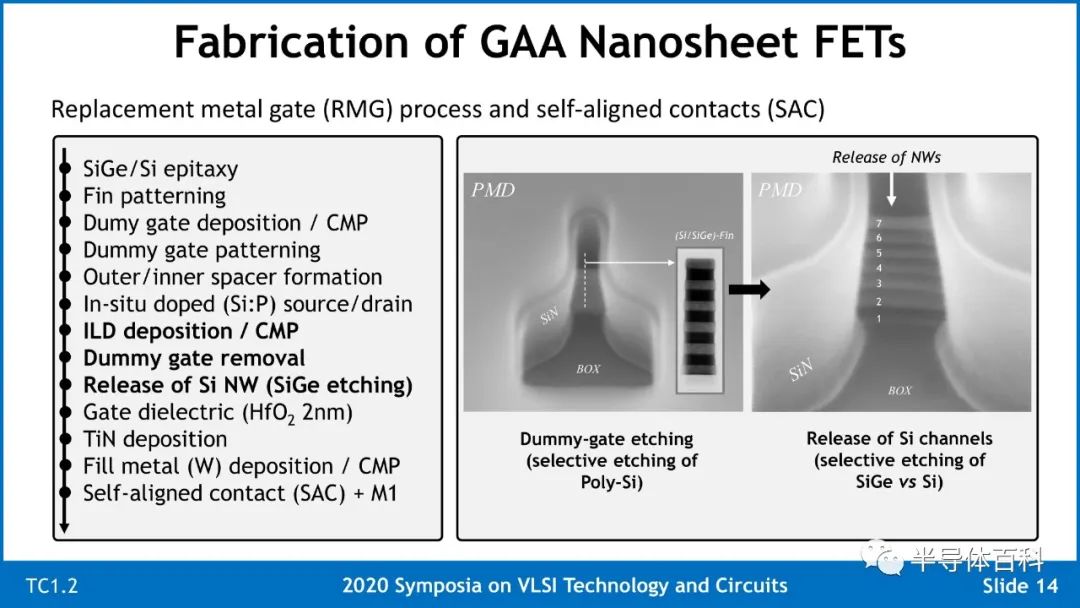

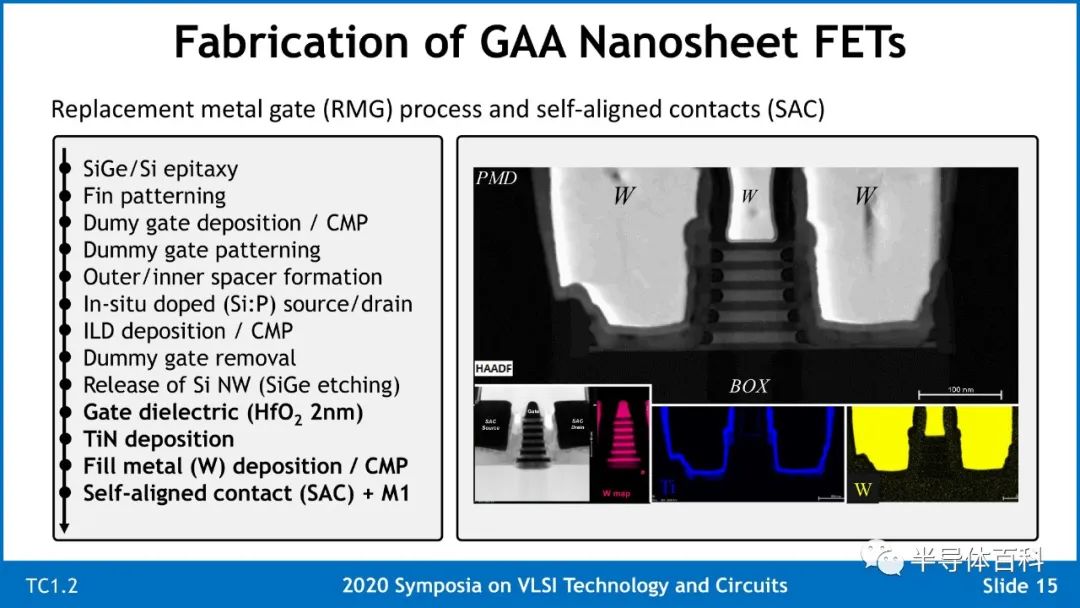

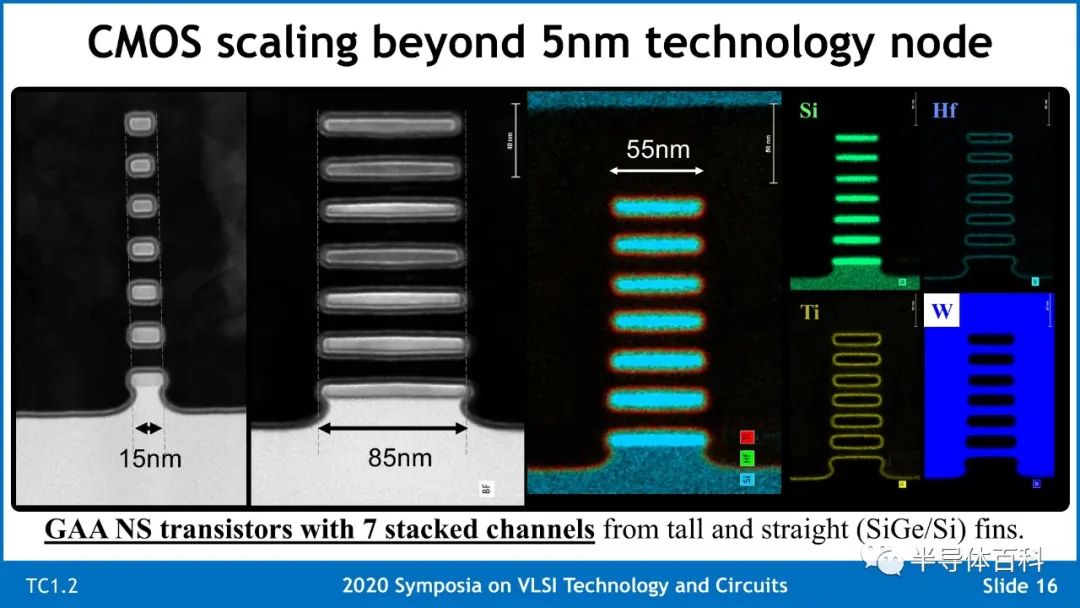

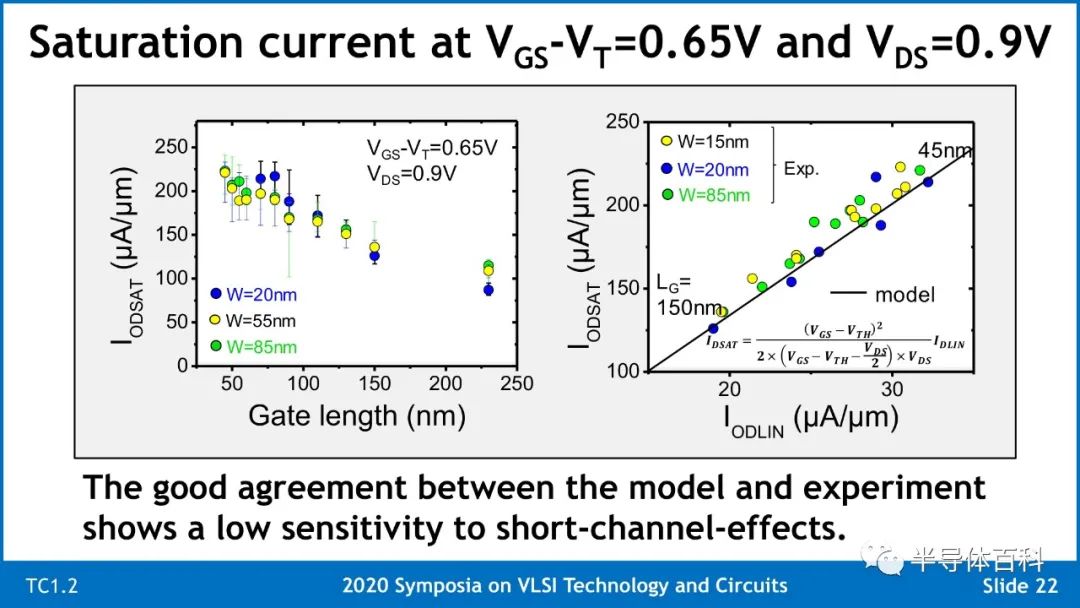

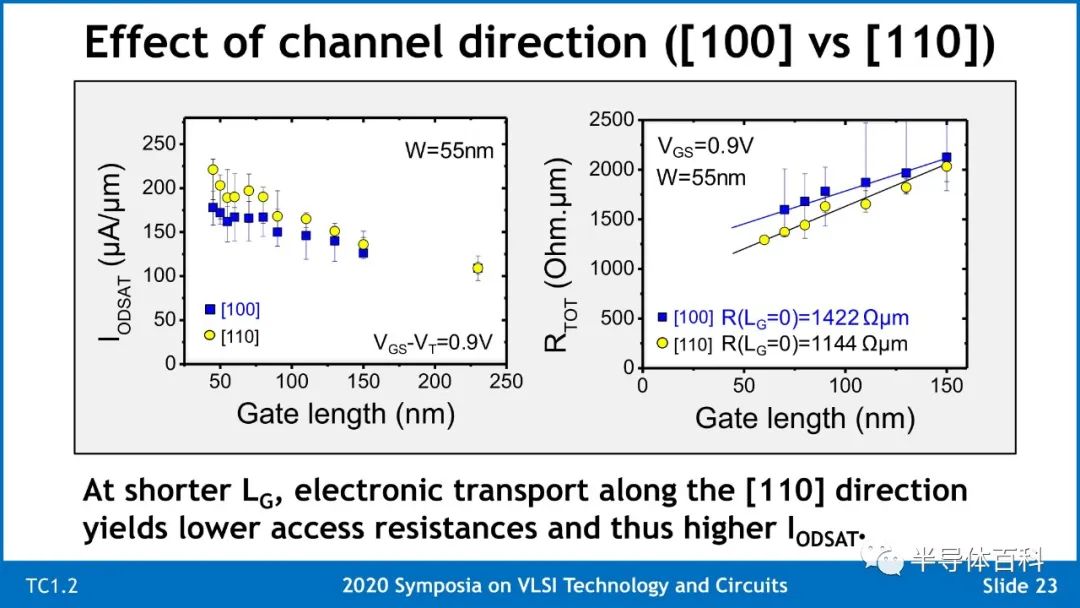

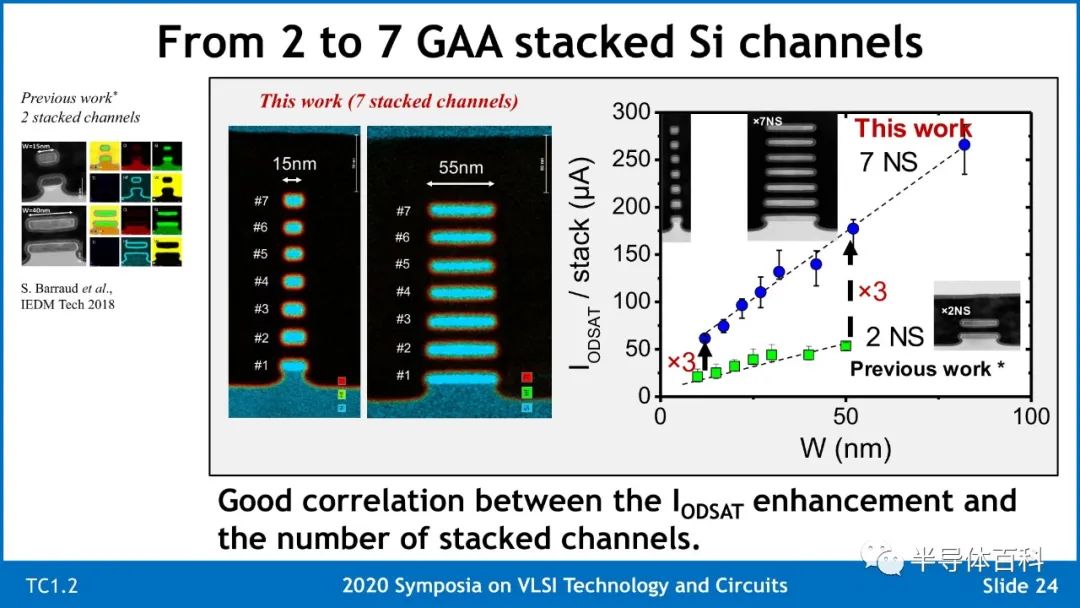

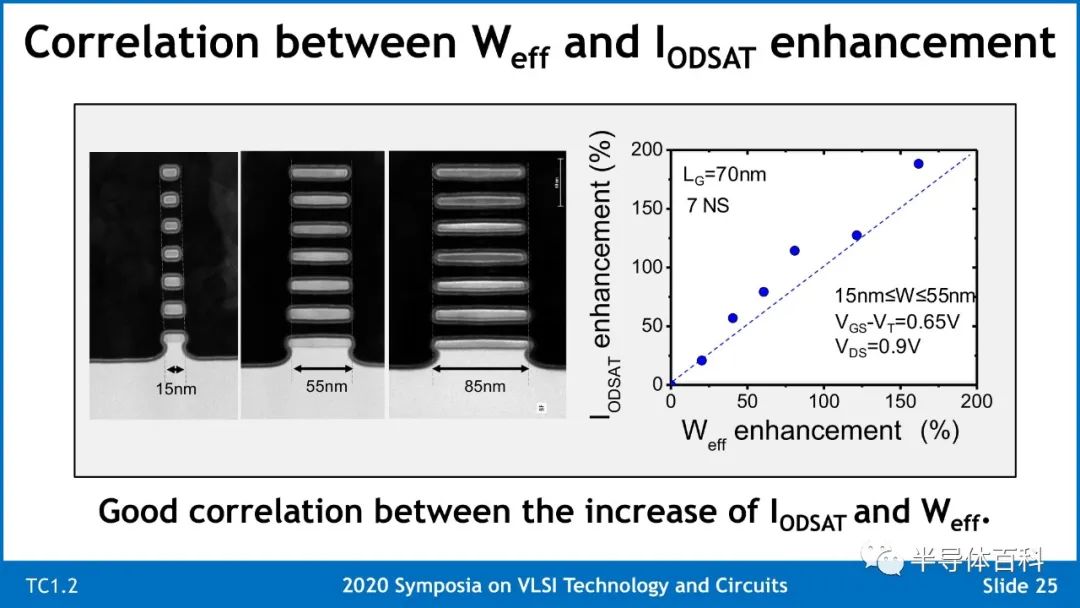

Leti宣布推出7層納米片GAA晶體管

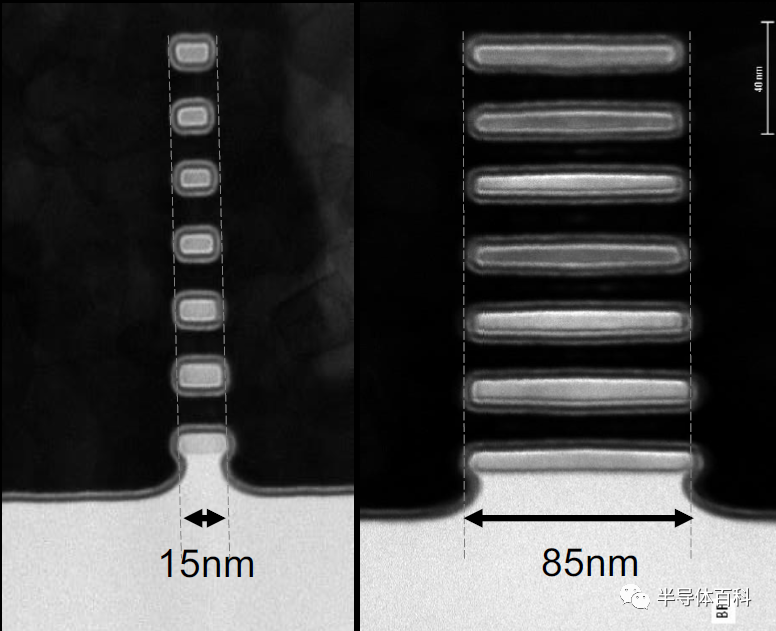

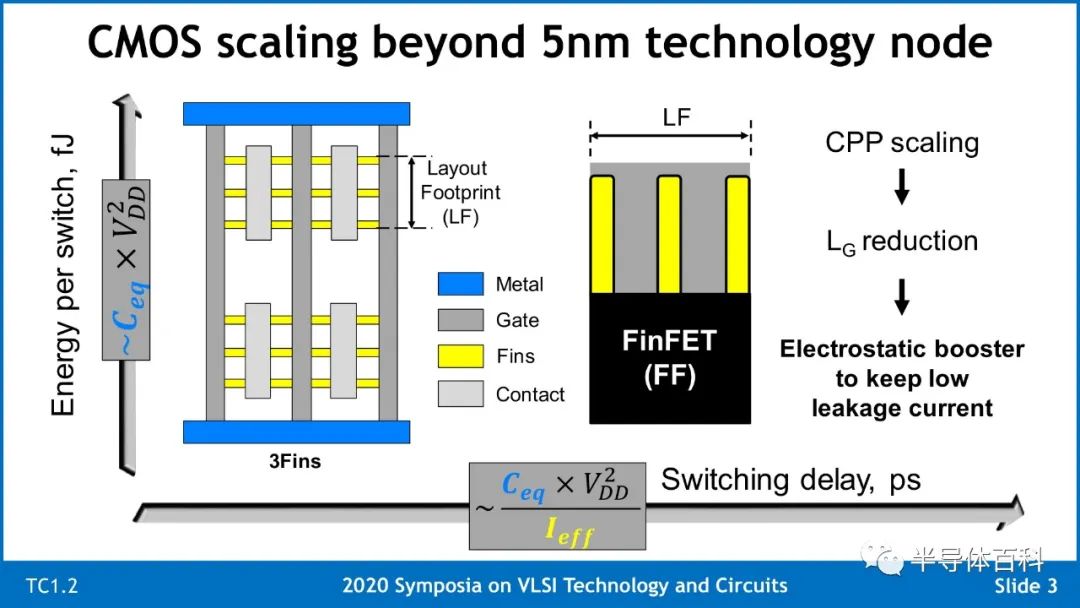

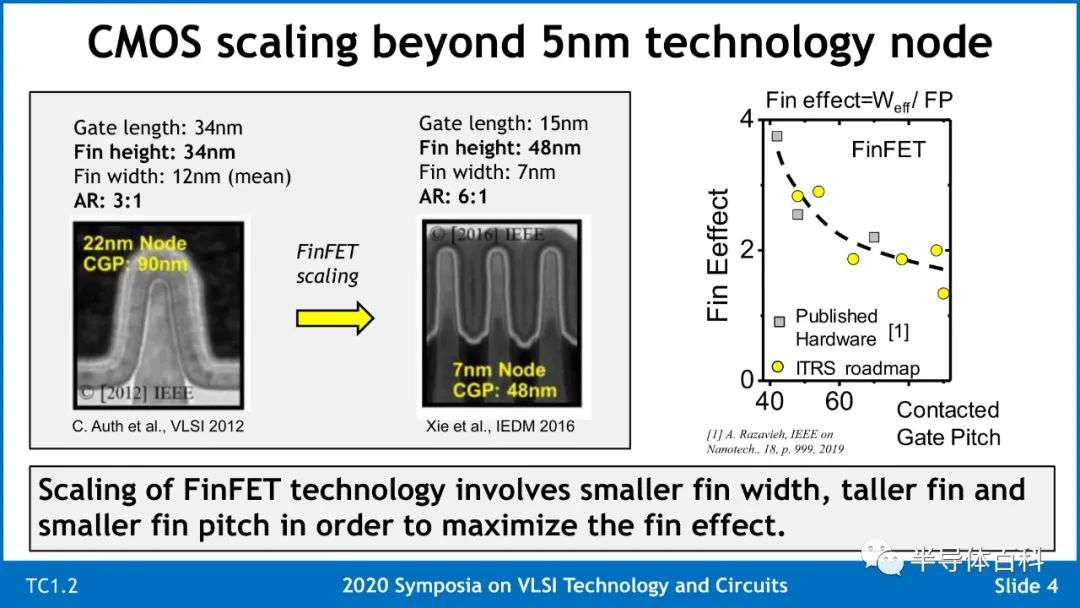

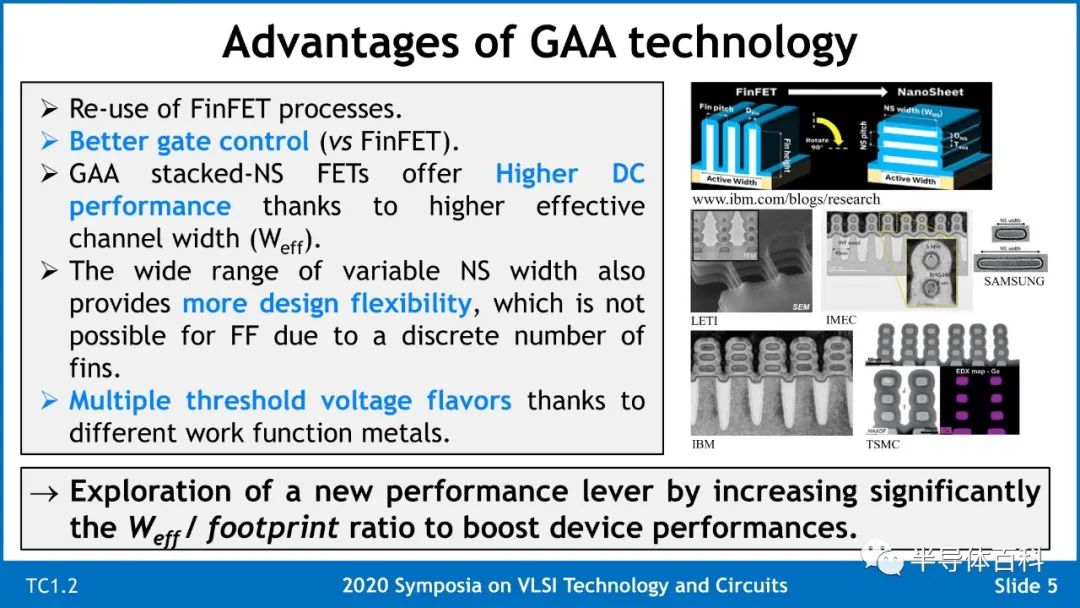

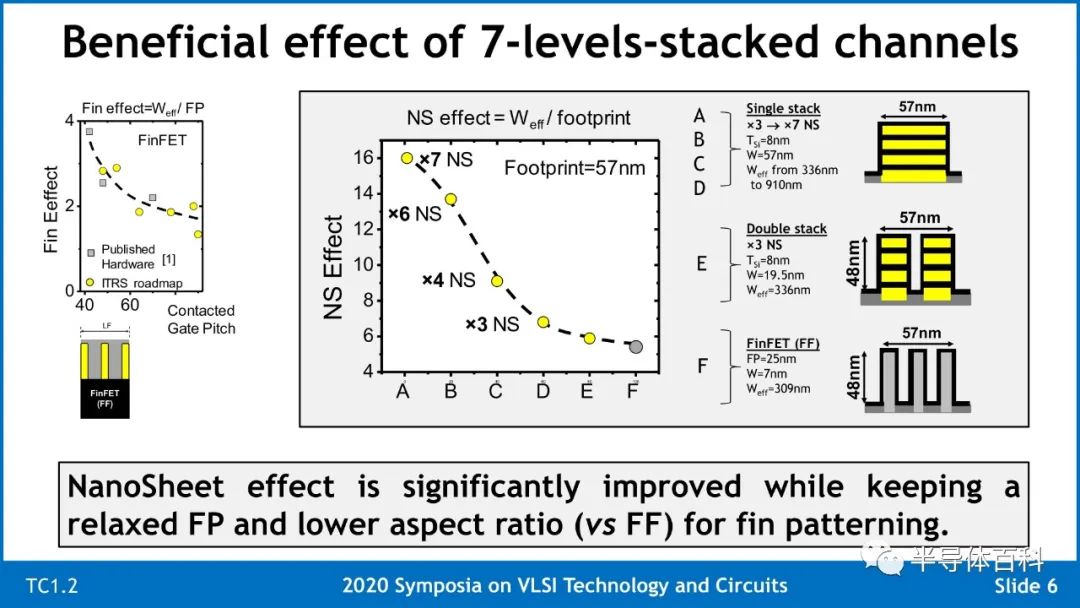

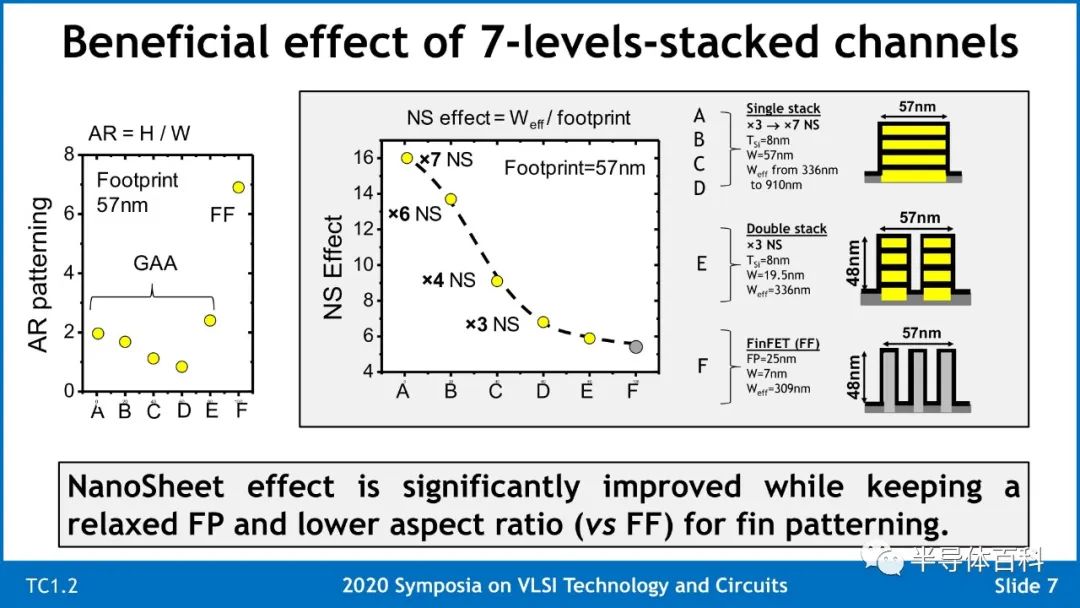

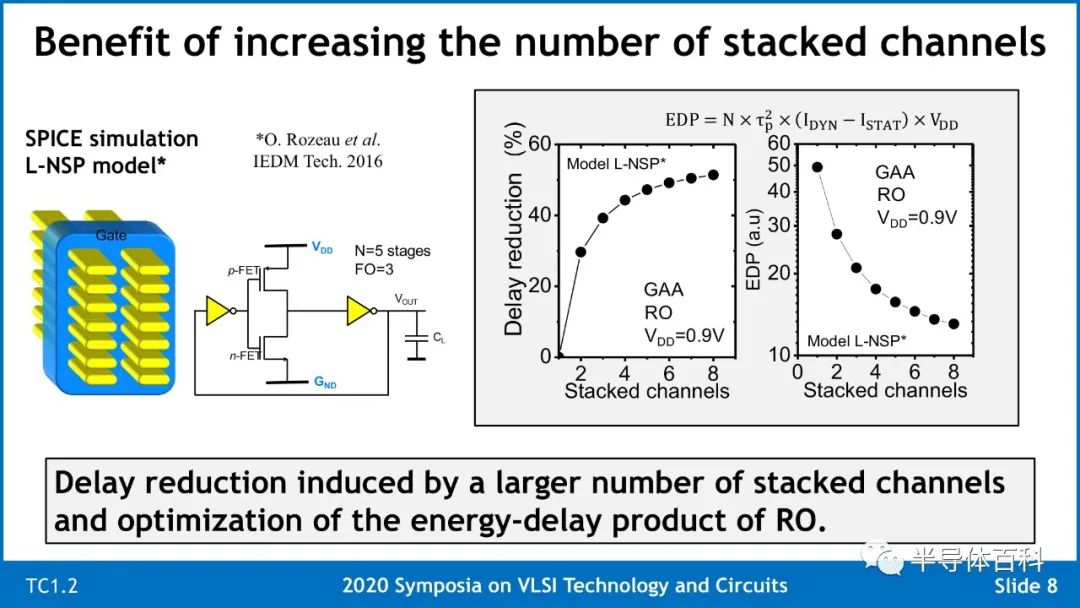

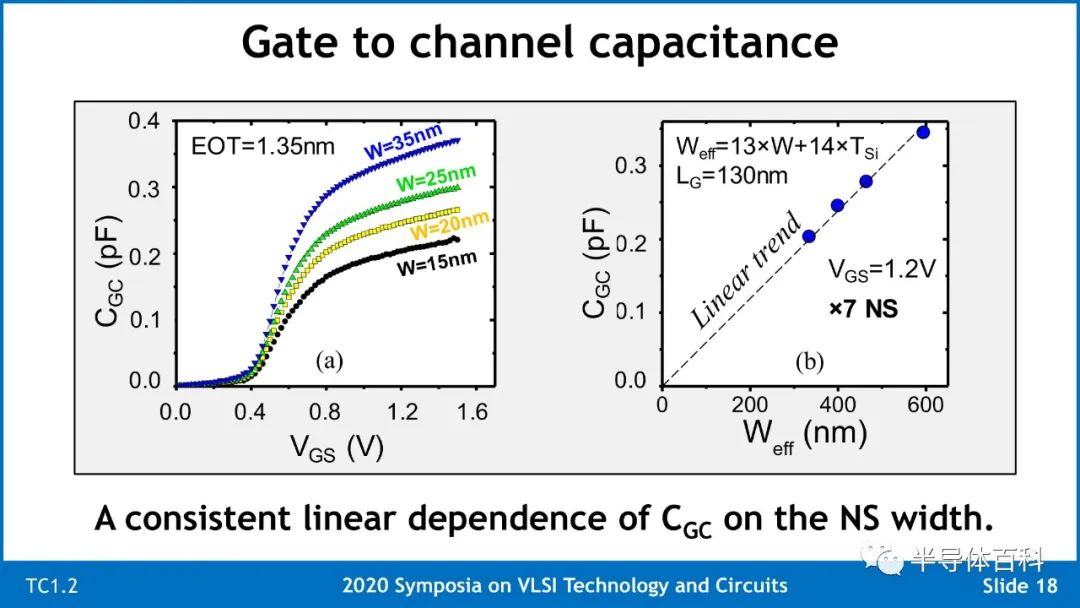

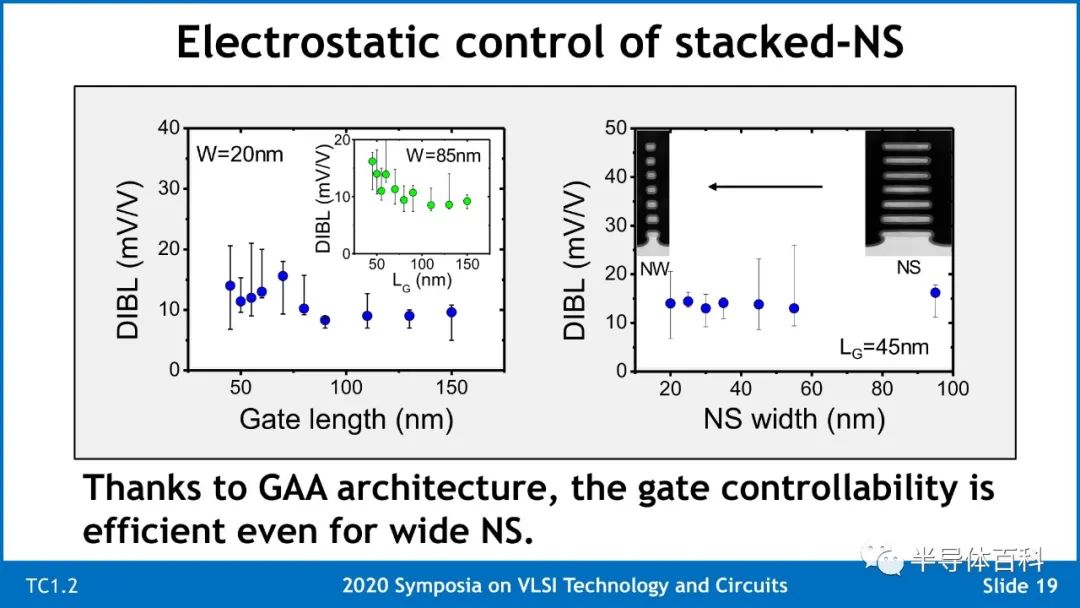

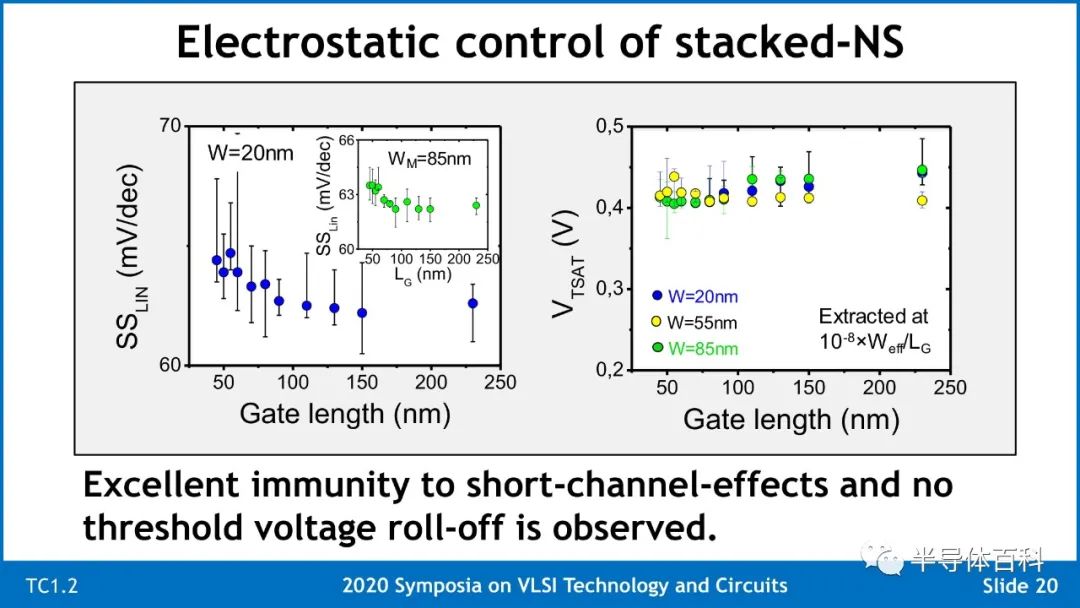

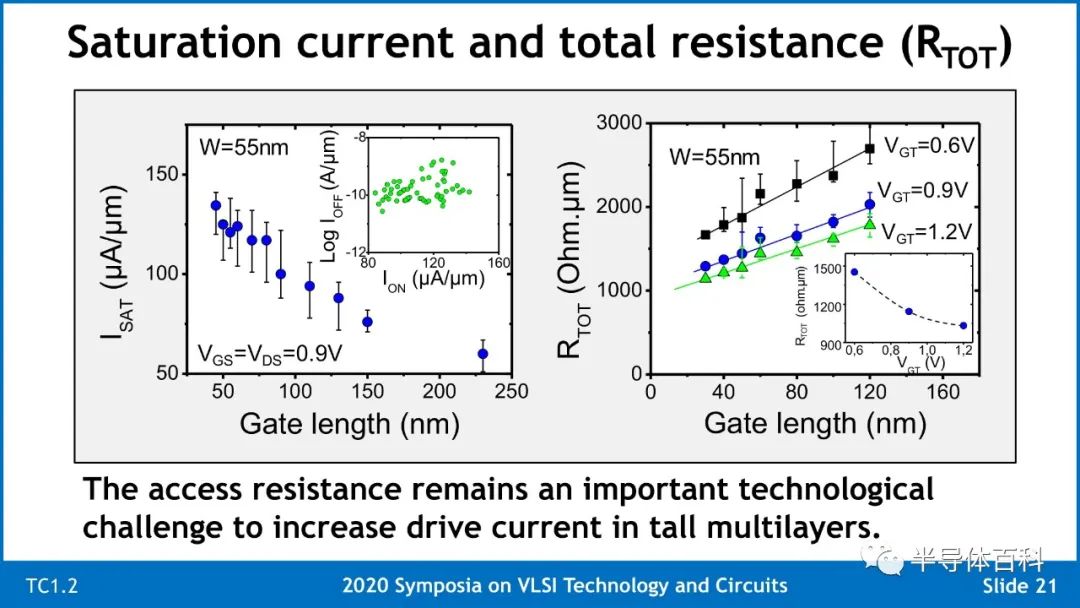

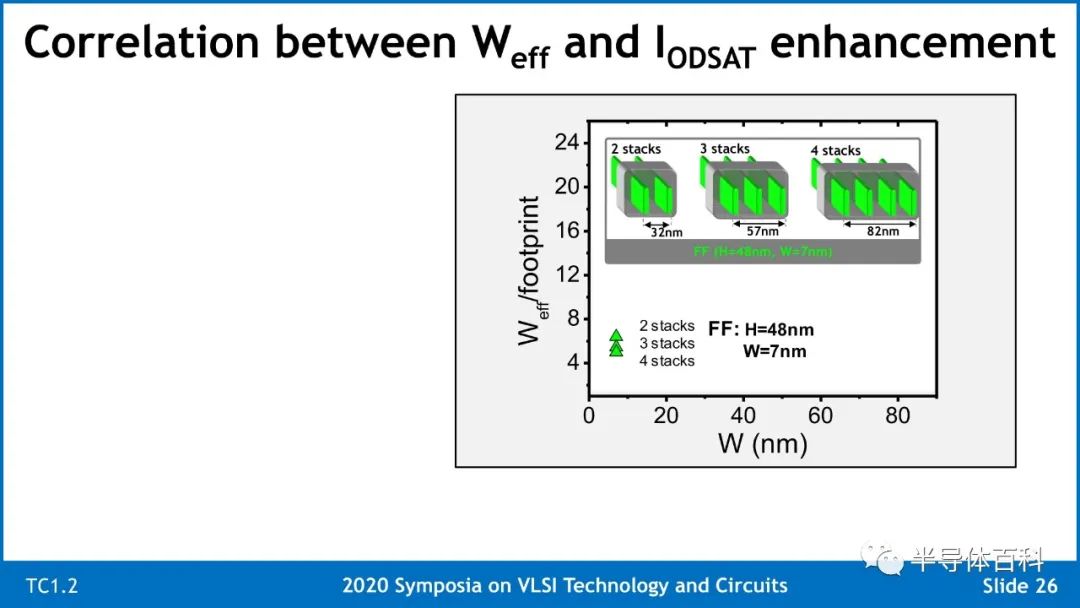

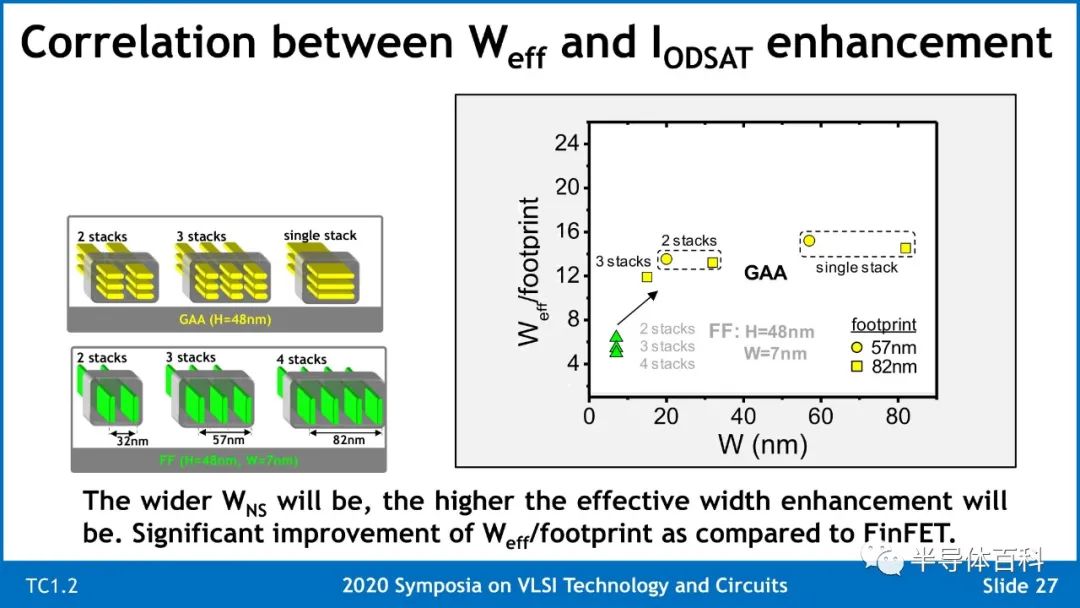

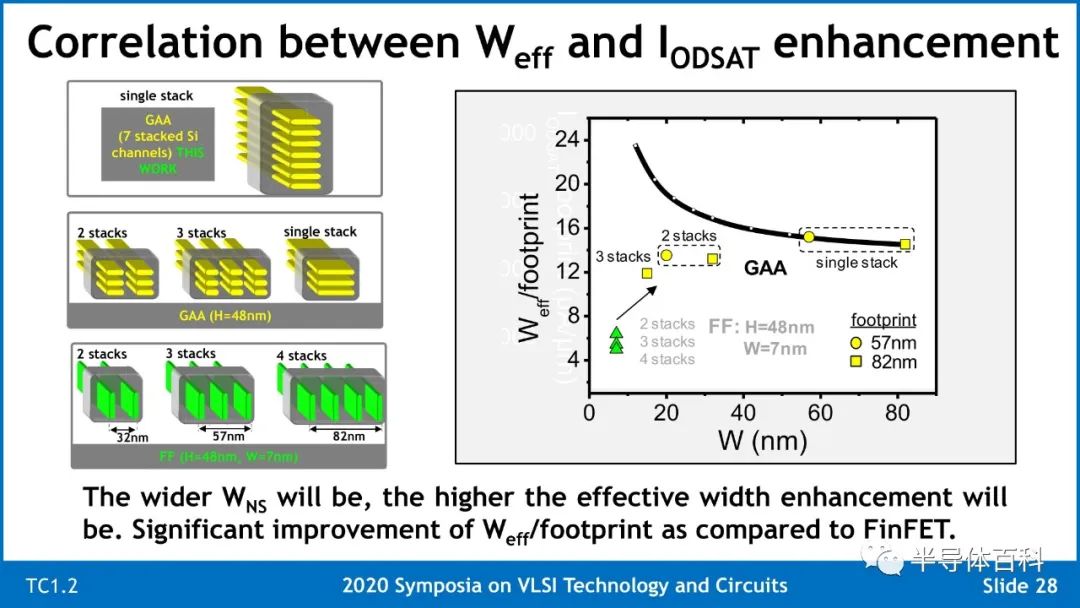

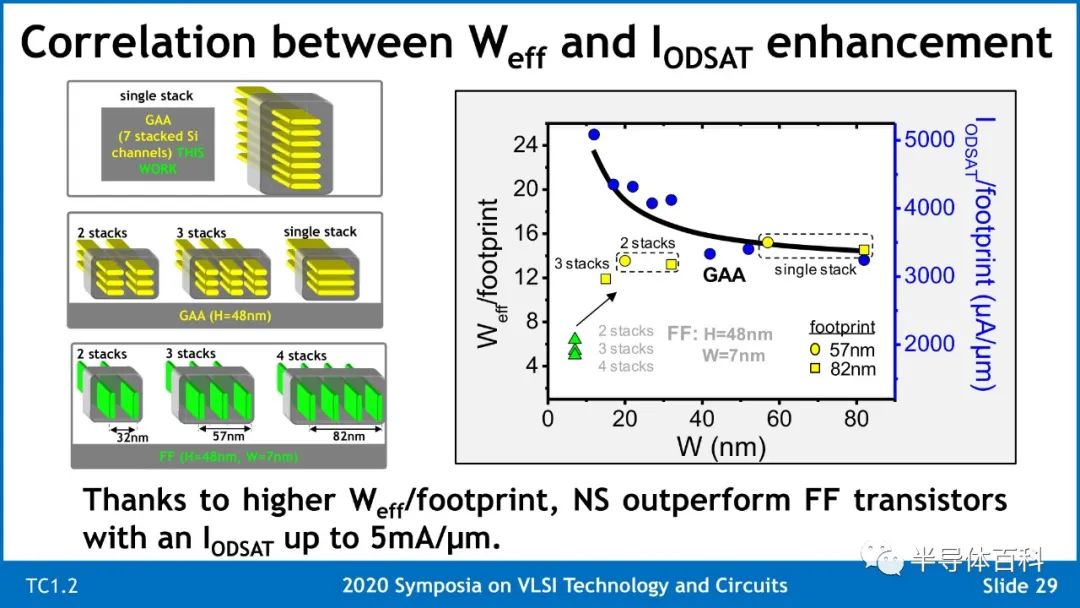

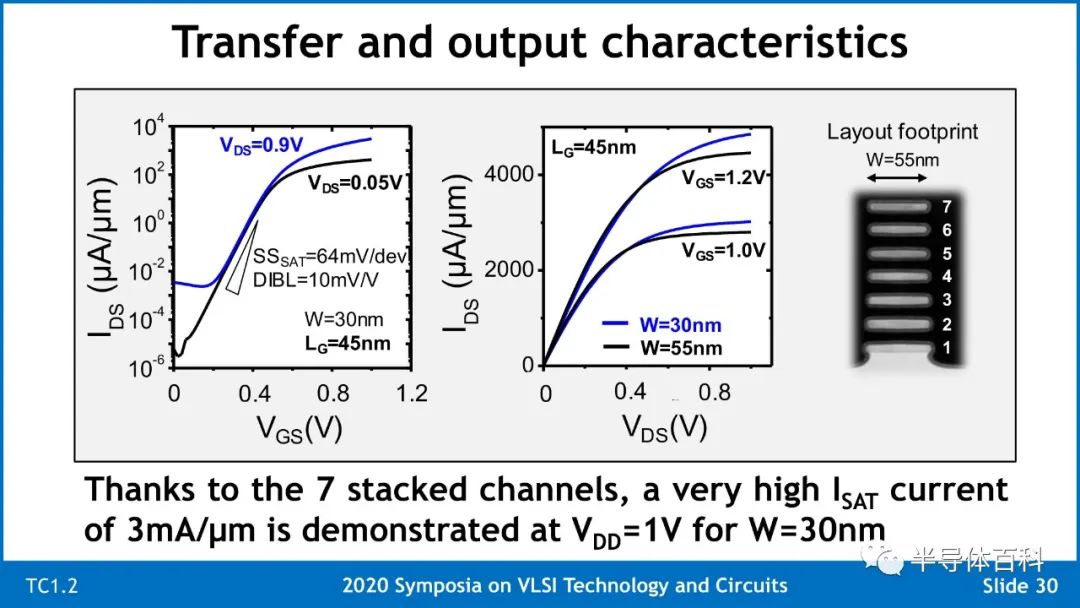

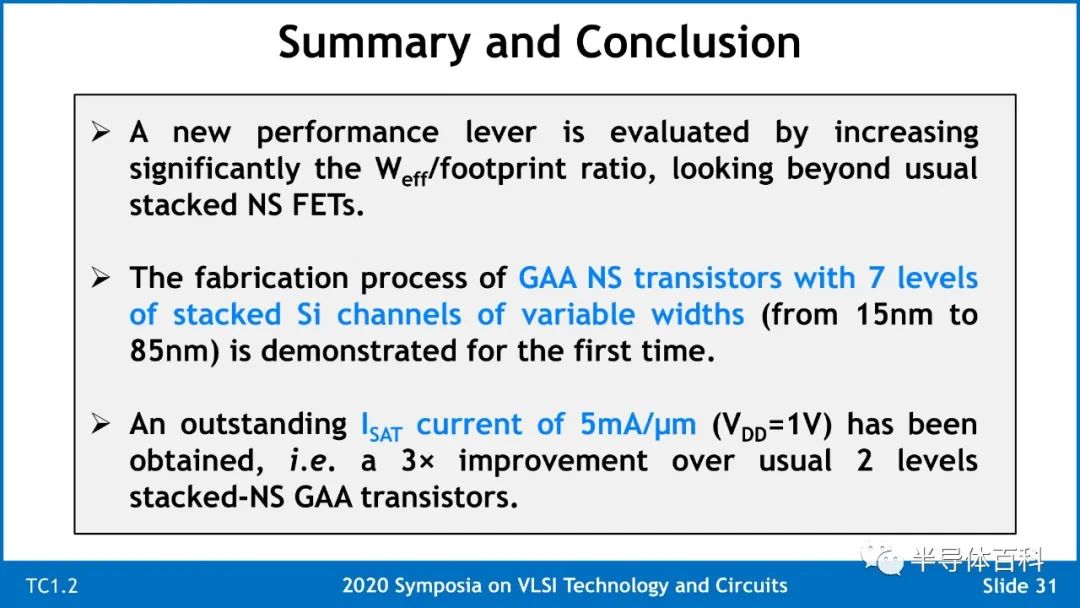

環繞柵(GAA)納米片晶體管的有效溝道寬度大,因此其性能優于FinFET。法國國家電子技術研究所(CEA-LETI-MINATEC)的研究人員討論了在增加每個有效通道寬度以改善器件性能和制造工藝復雜性之間進行權衡的問題。 他們首次制作了具有RMG工藝金屬柵極,Inner spacer和自對準接觸的七層GAA納米片晶體管原型。所制造的晶體管具有出色的溝道電控制能力和極高的電流驅動能力,其飽和電流是兩層堆疊納米片GAA晶體管的三倍(在VDD = 1V時為3mA /μm)。

圖3,7層納米片GAA晶體管的TEM圖

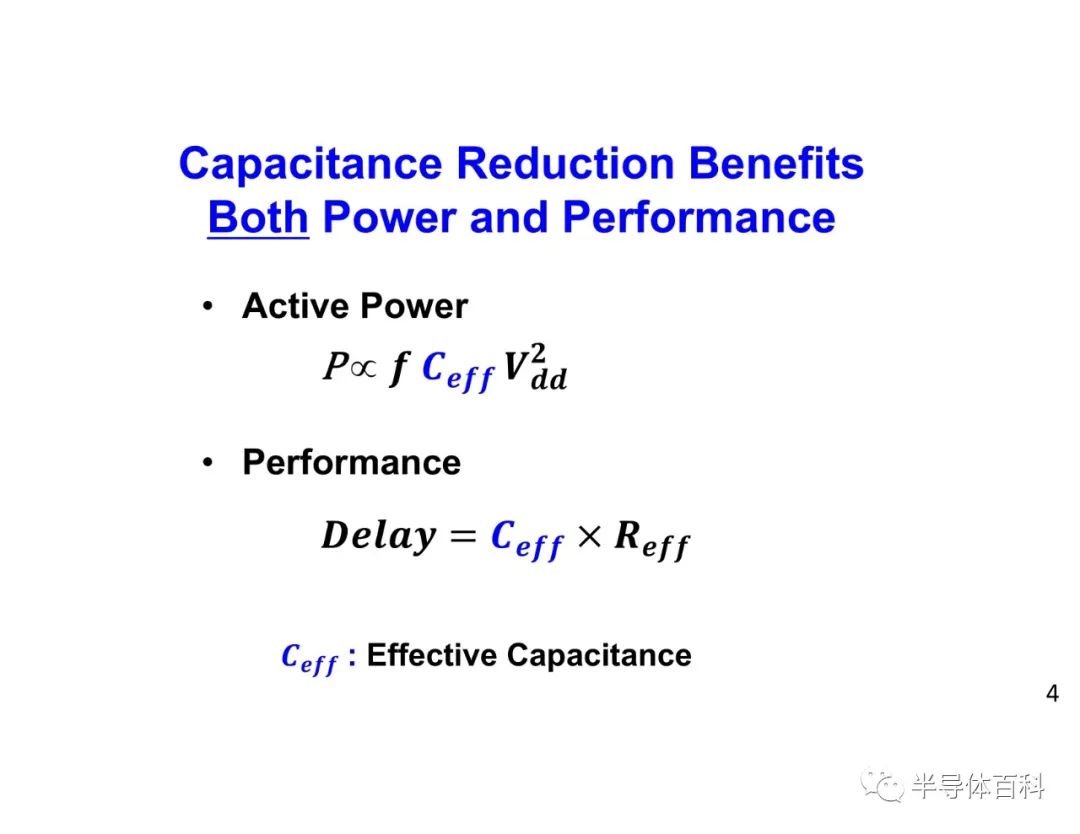

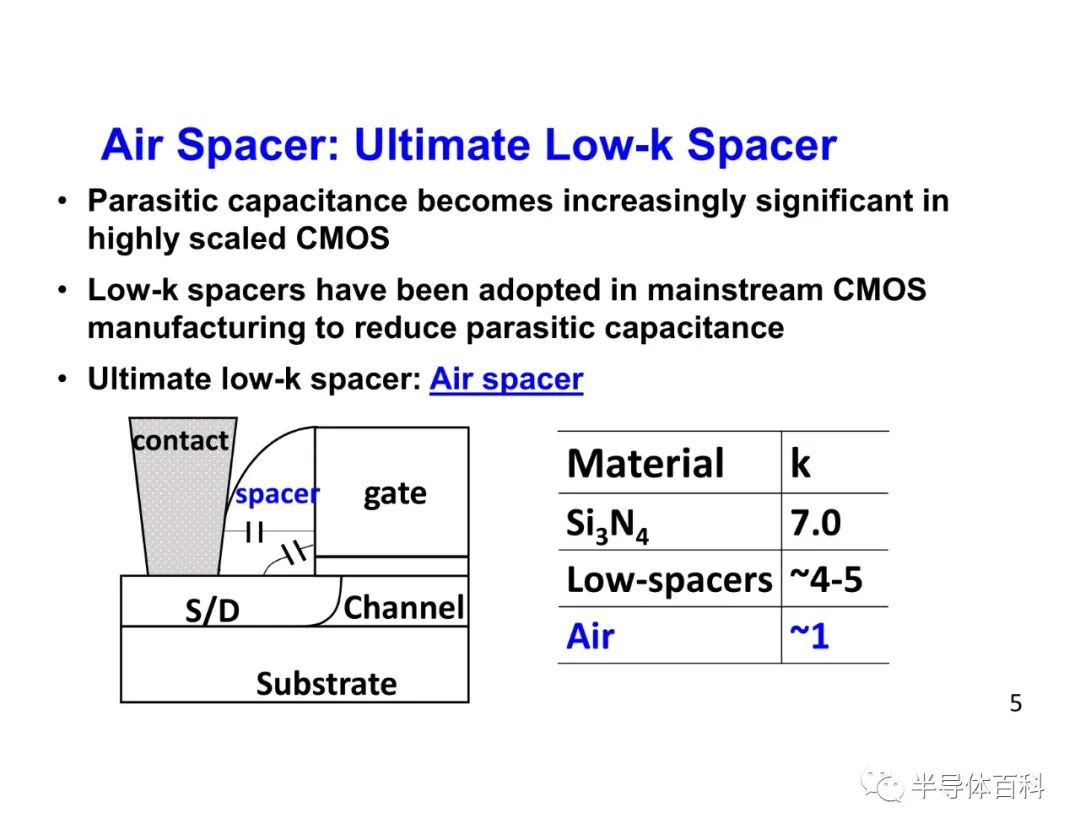

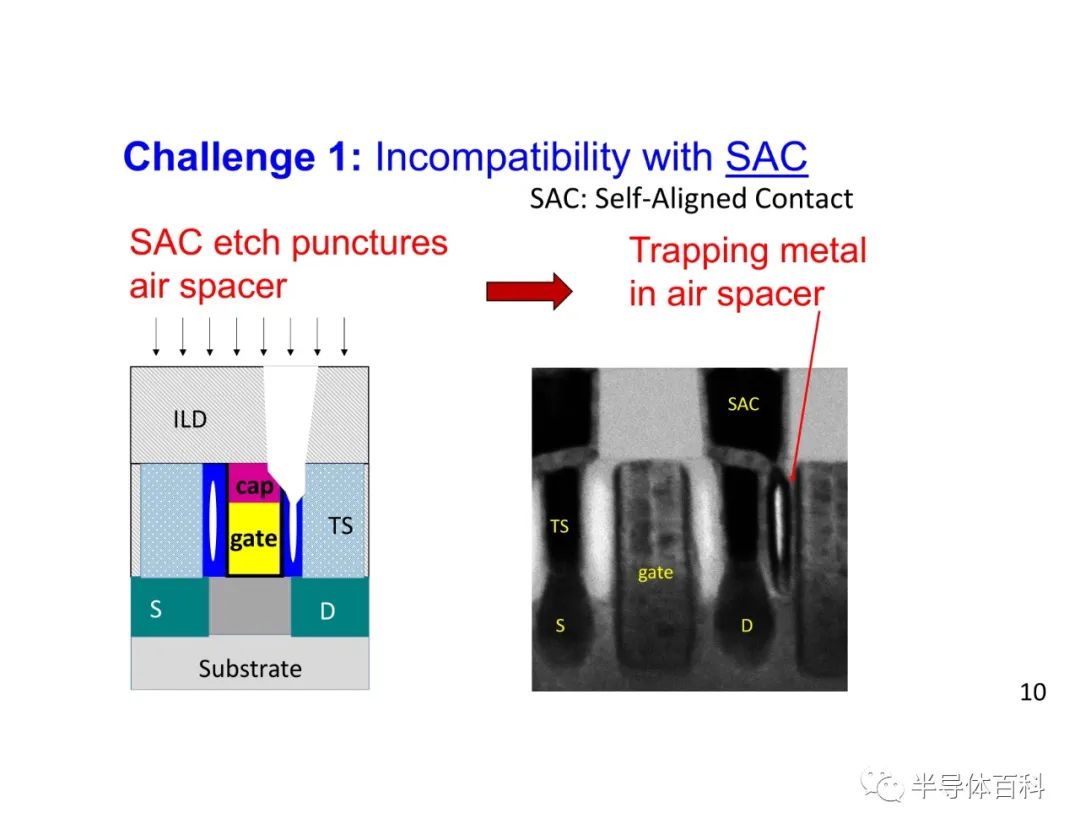

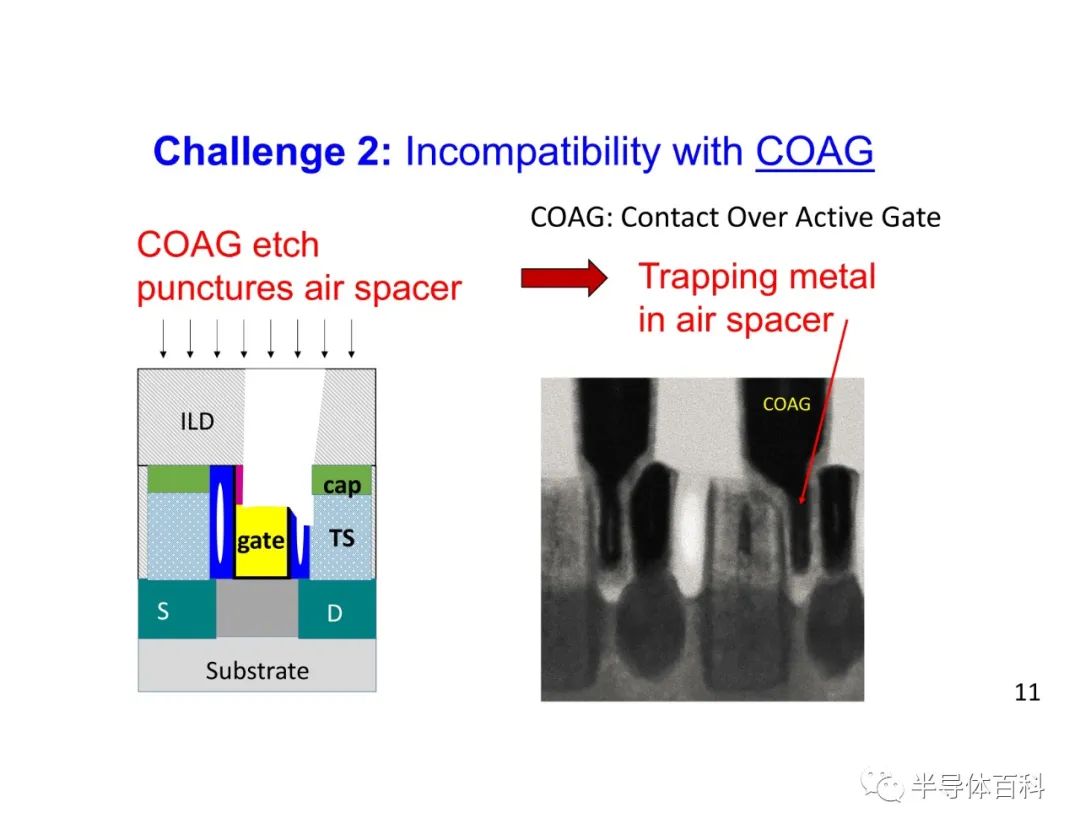

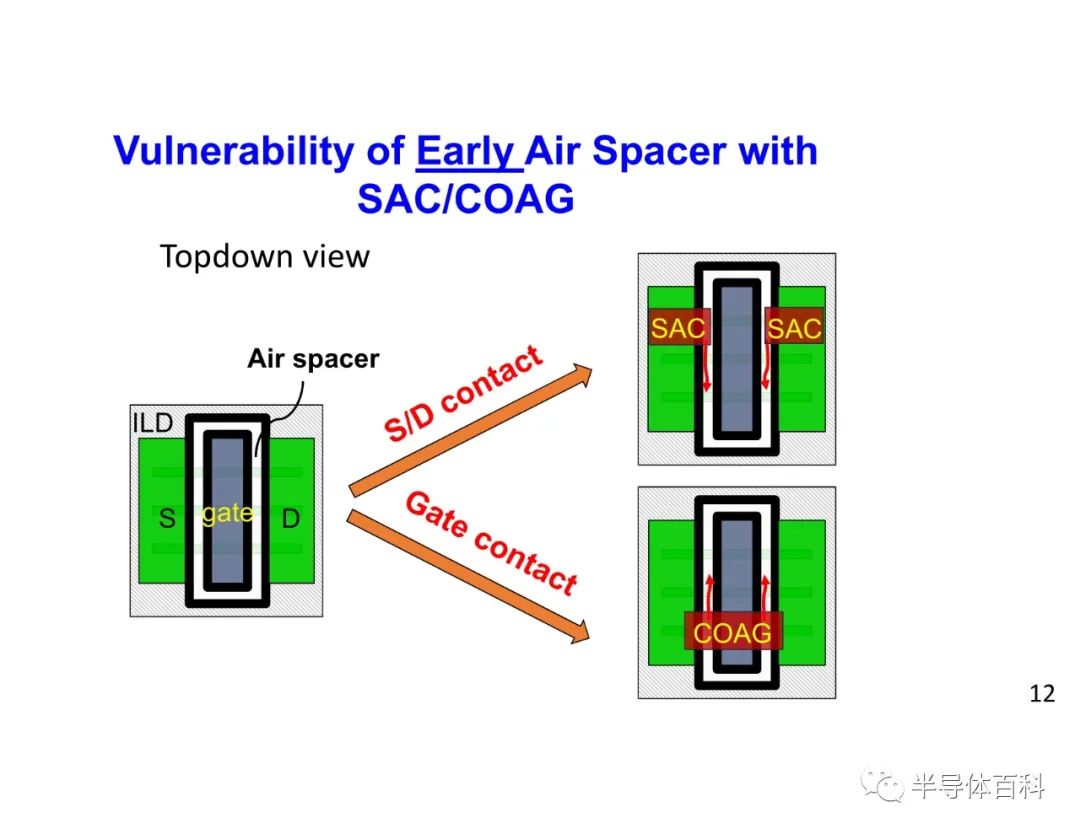

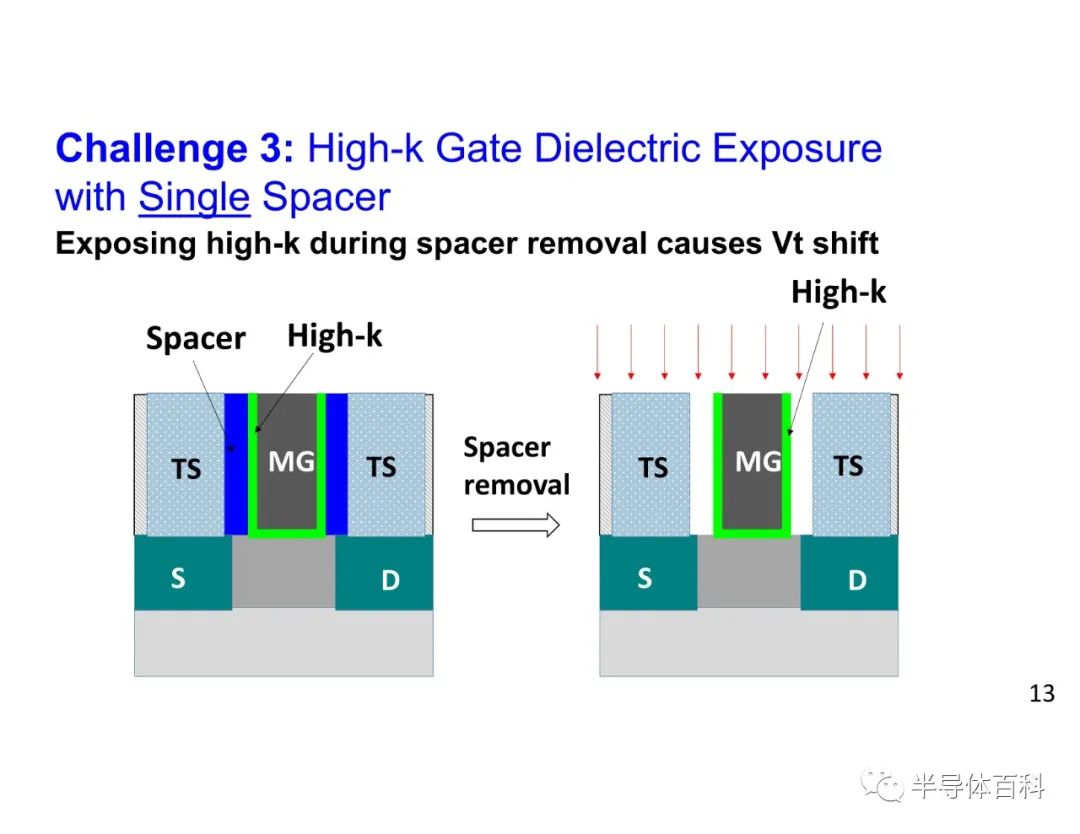

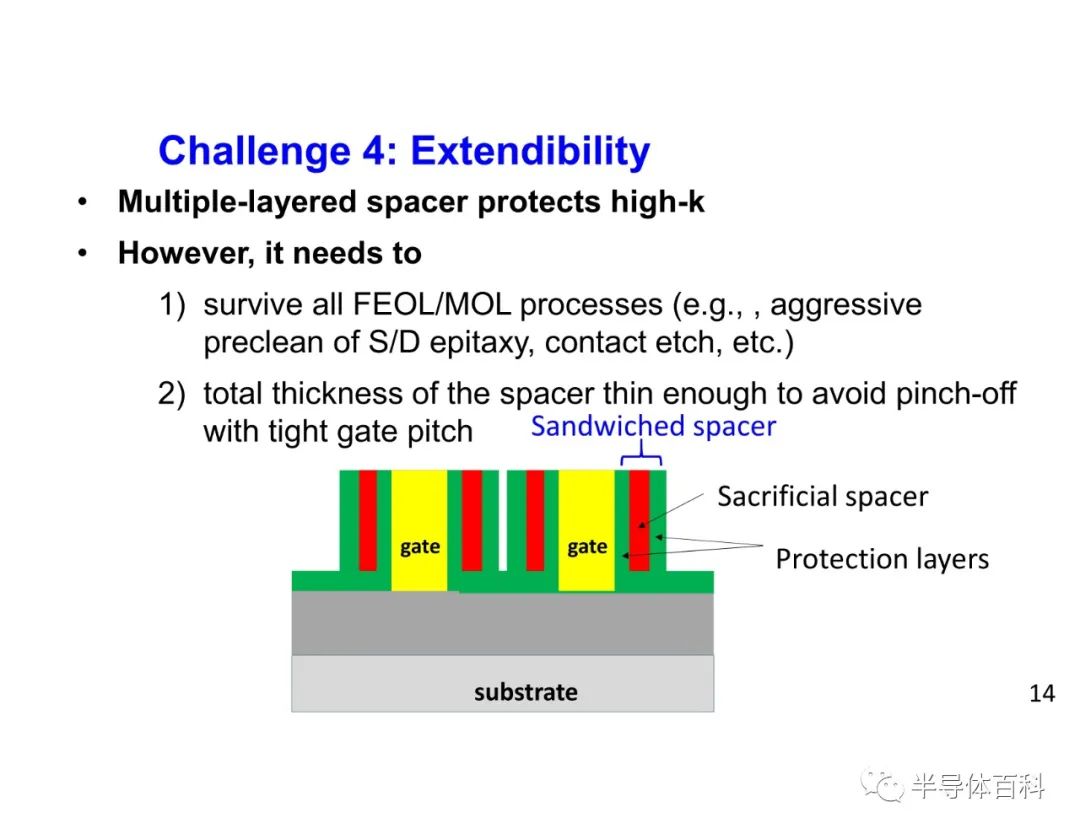

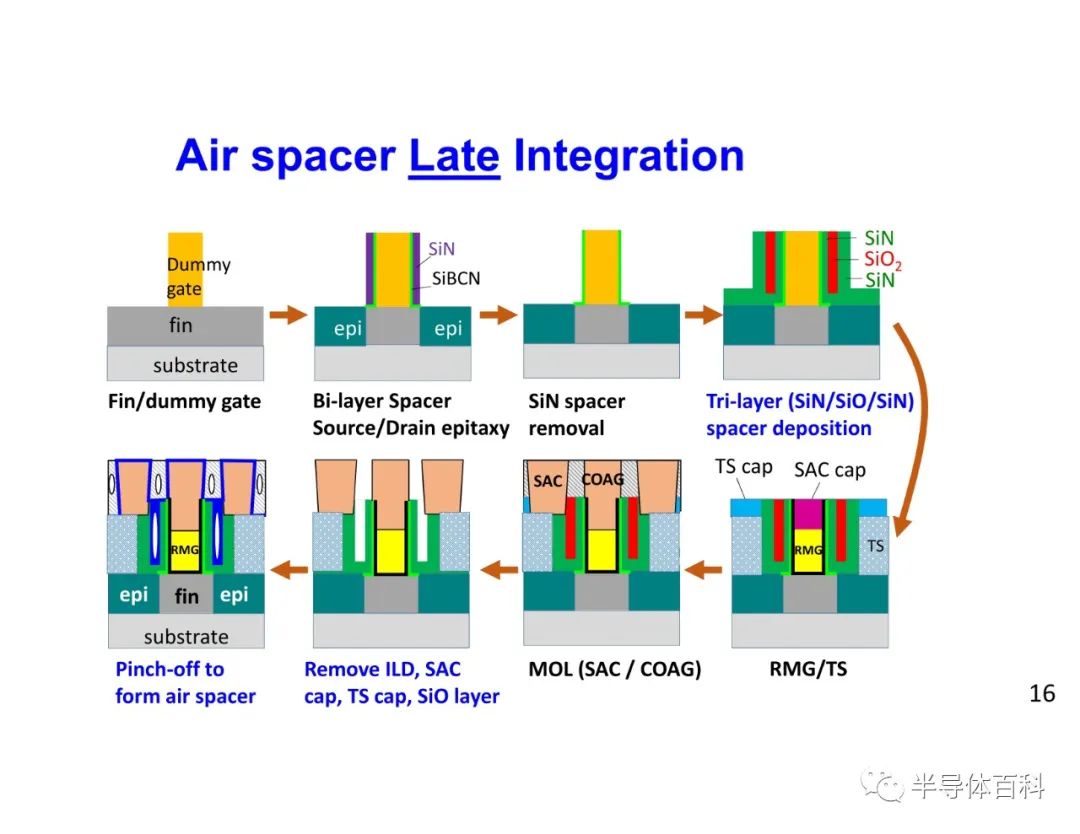

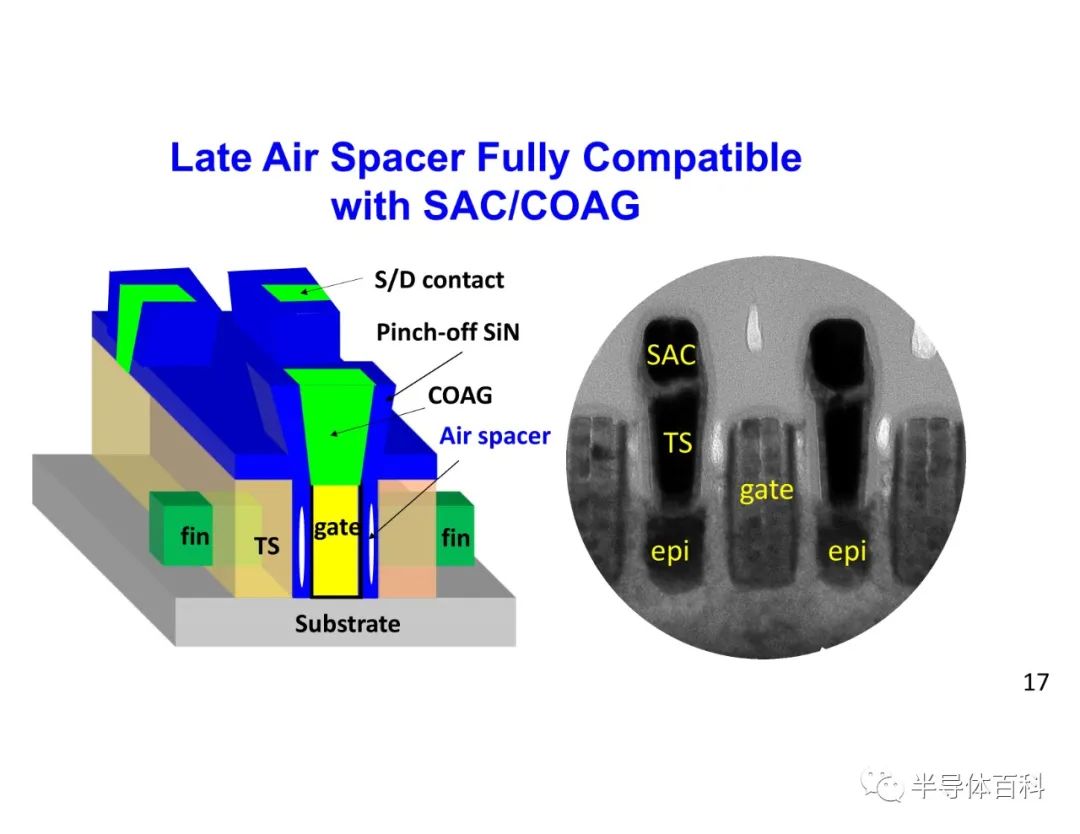

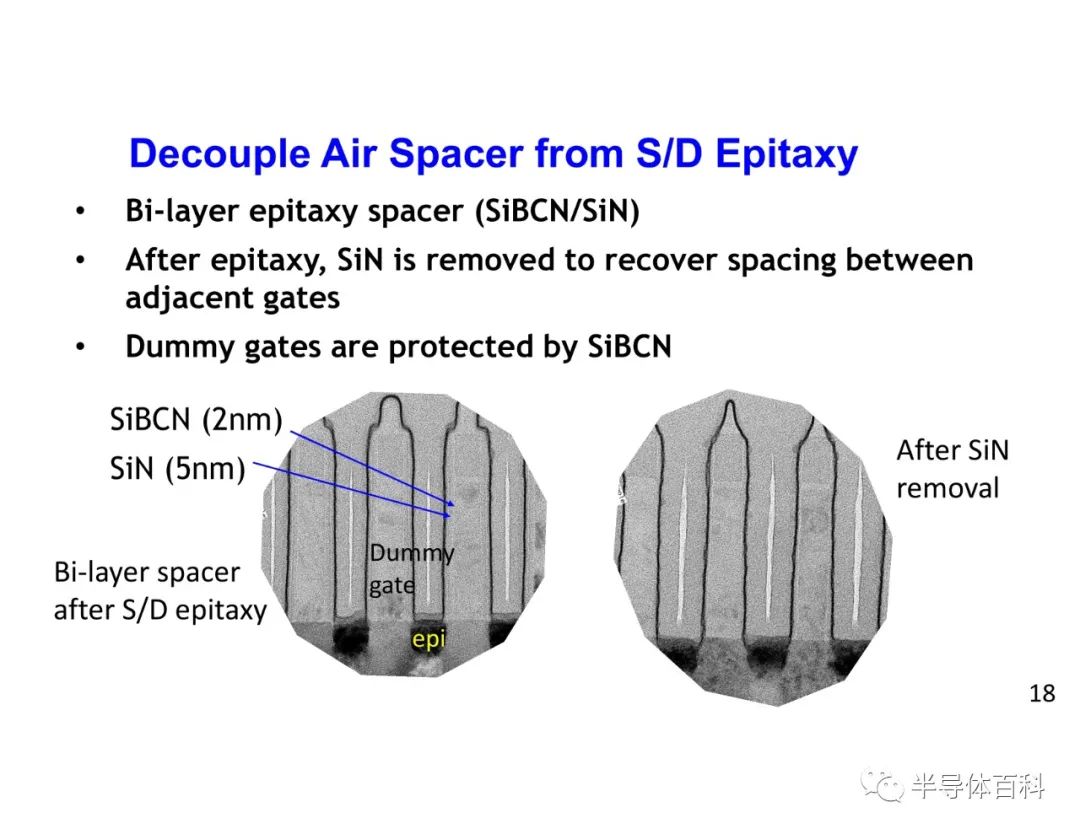

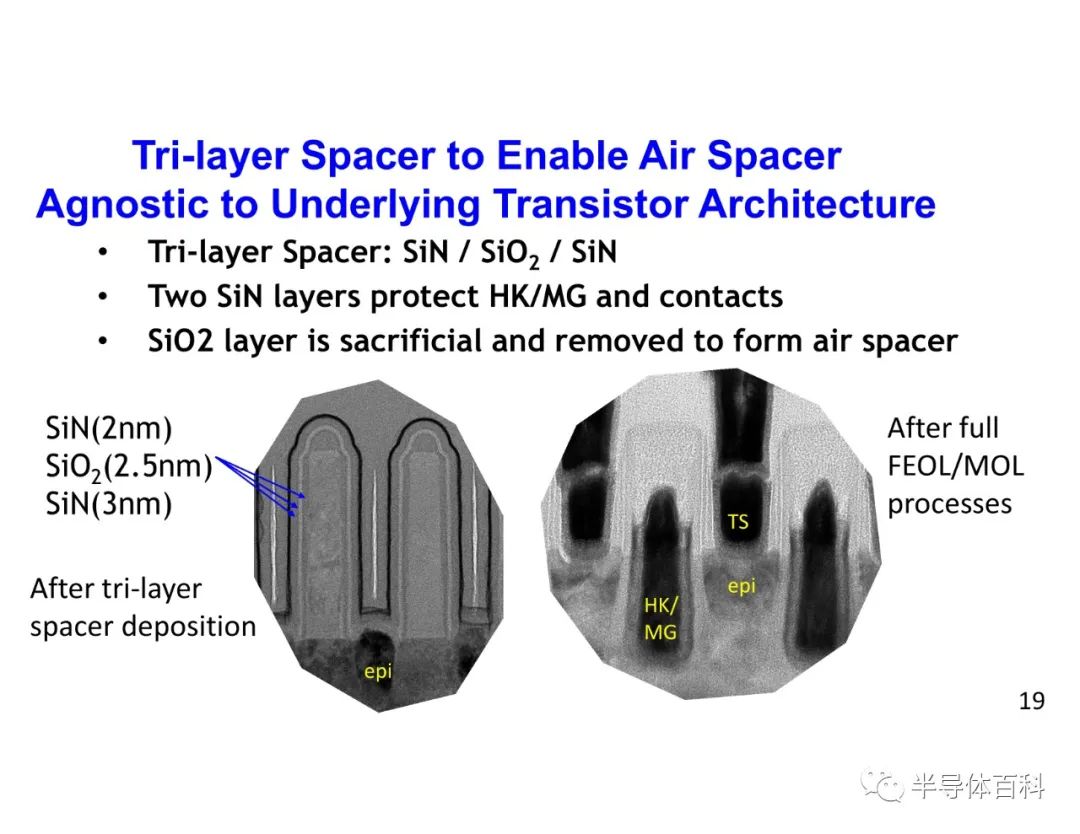

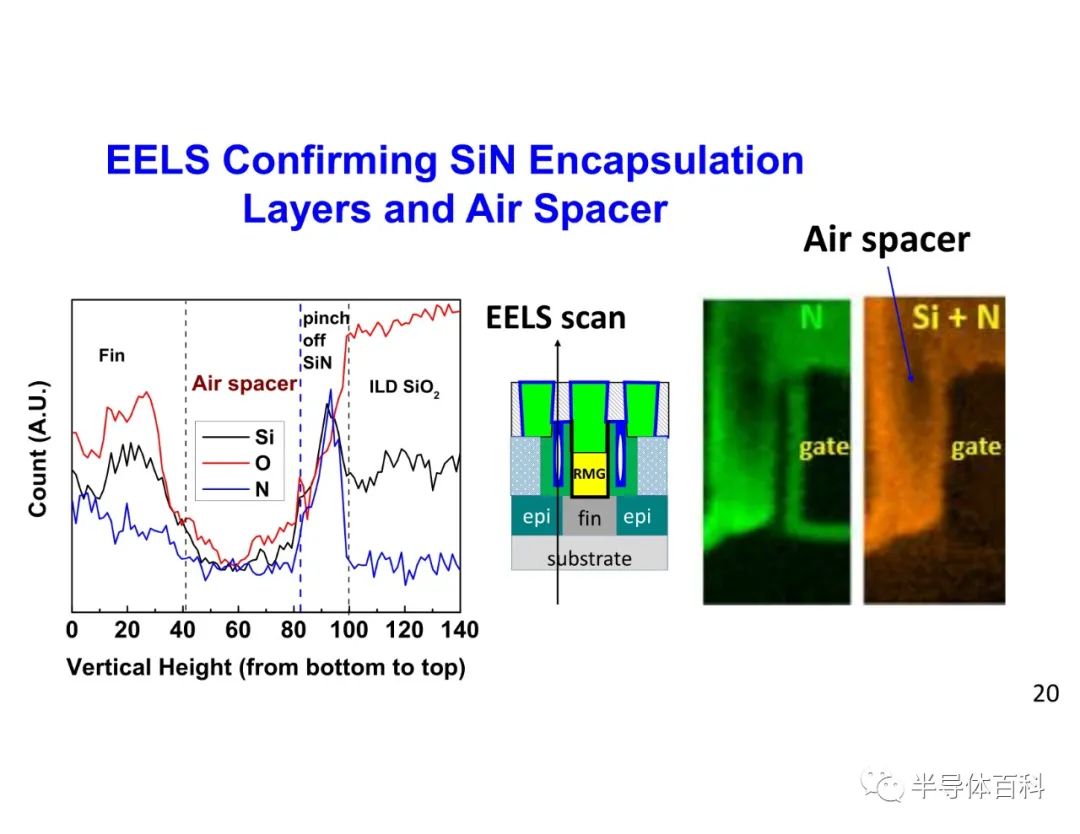

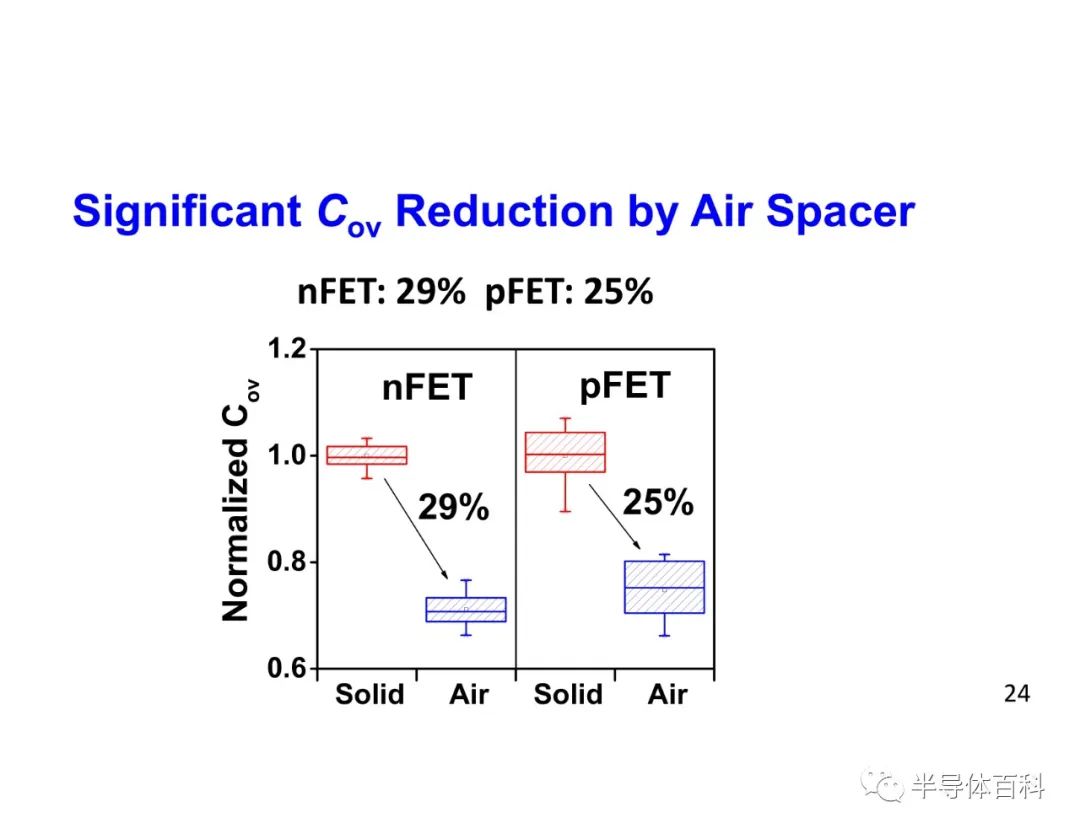

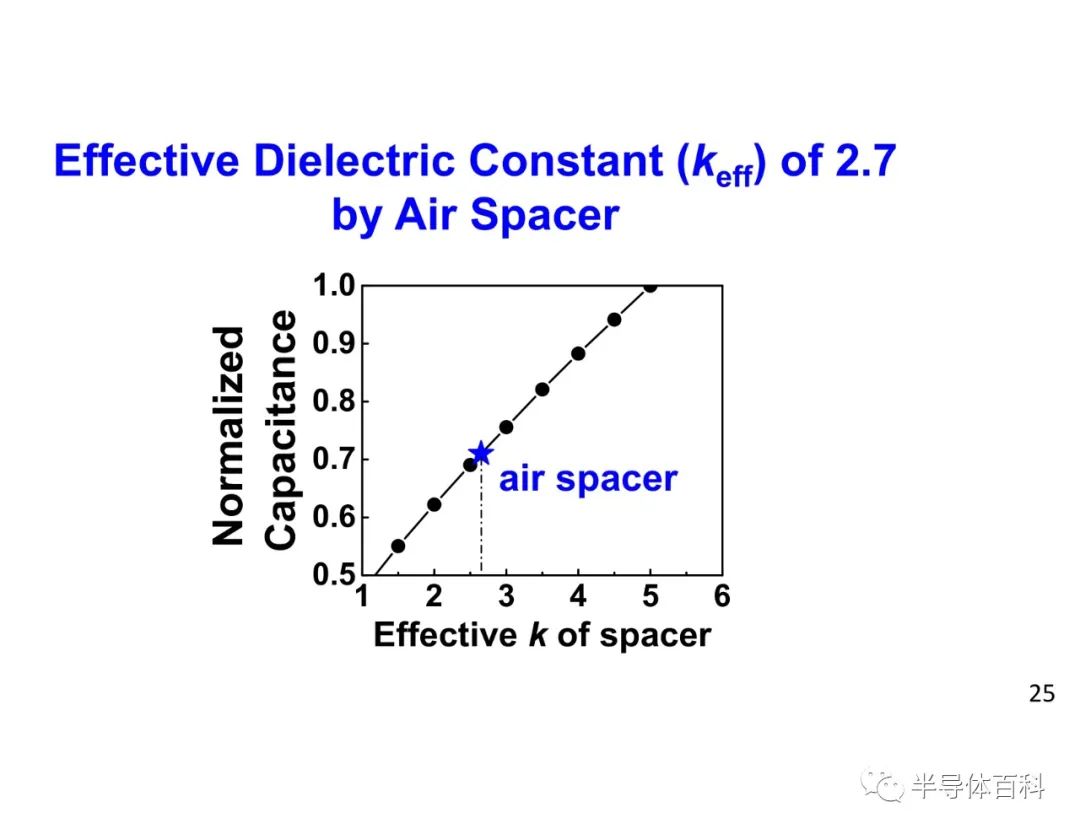

IBM報告了先進CMOS的Air Gap 柵極側墻技術

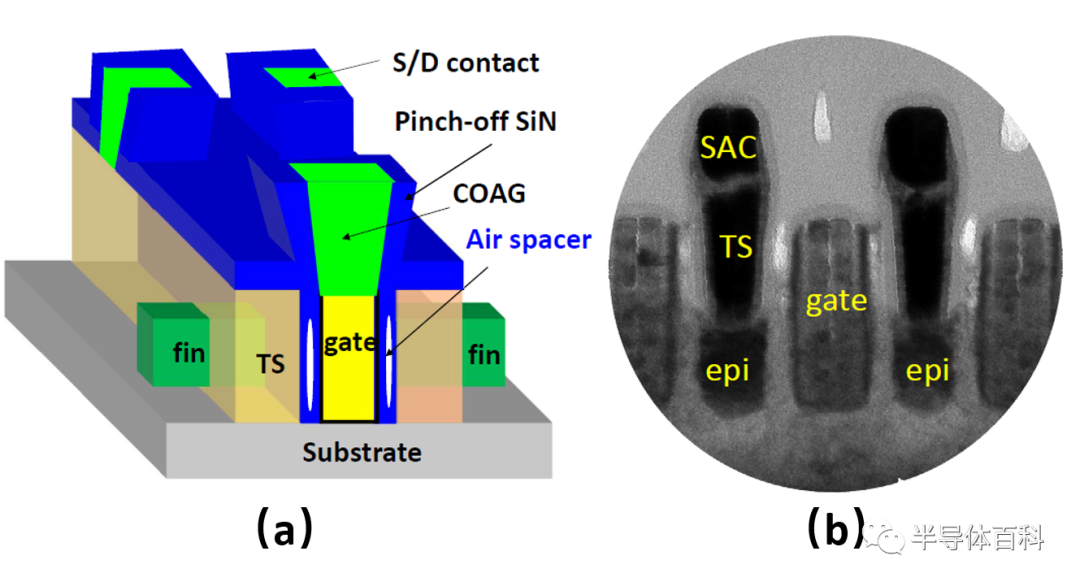

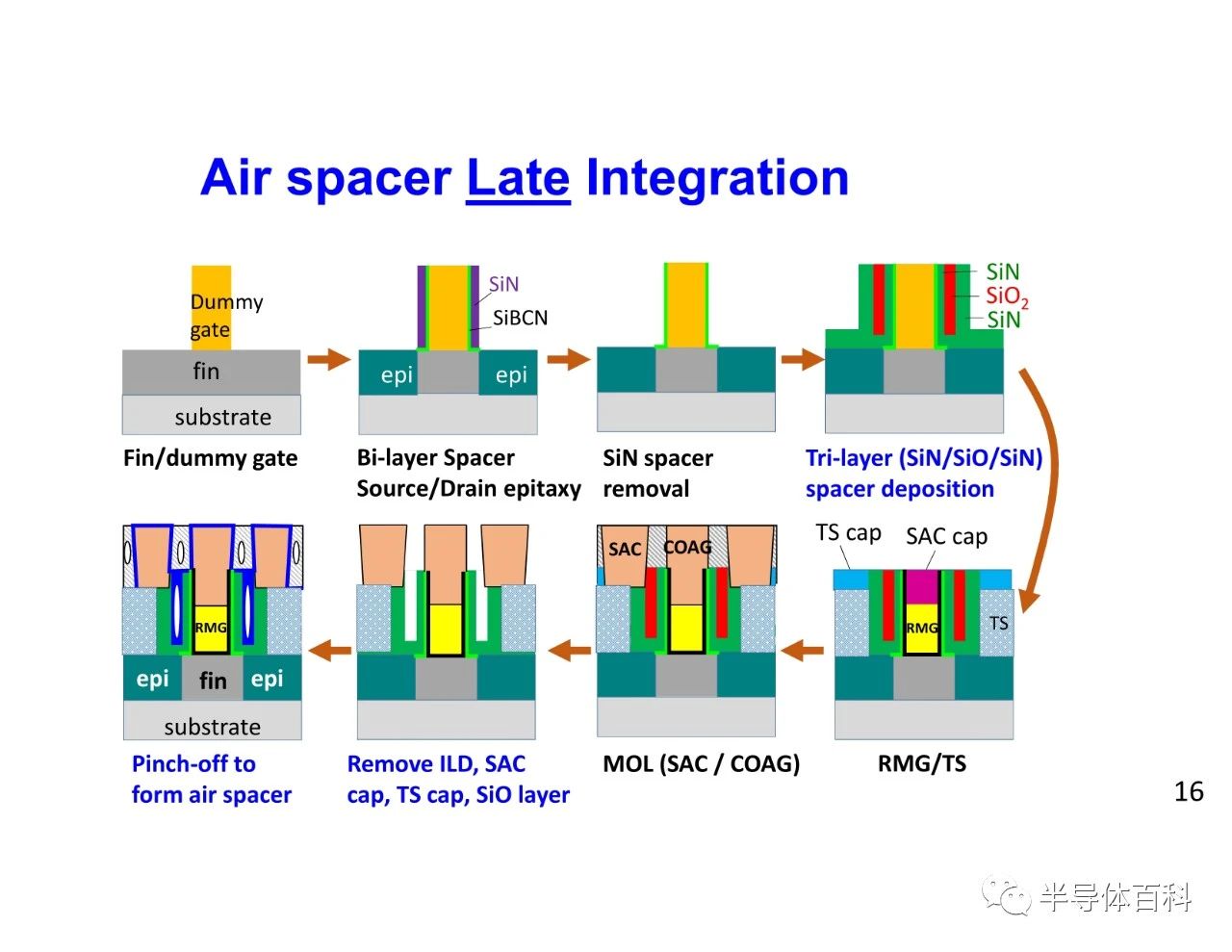

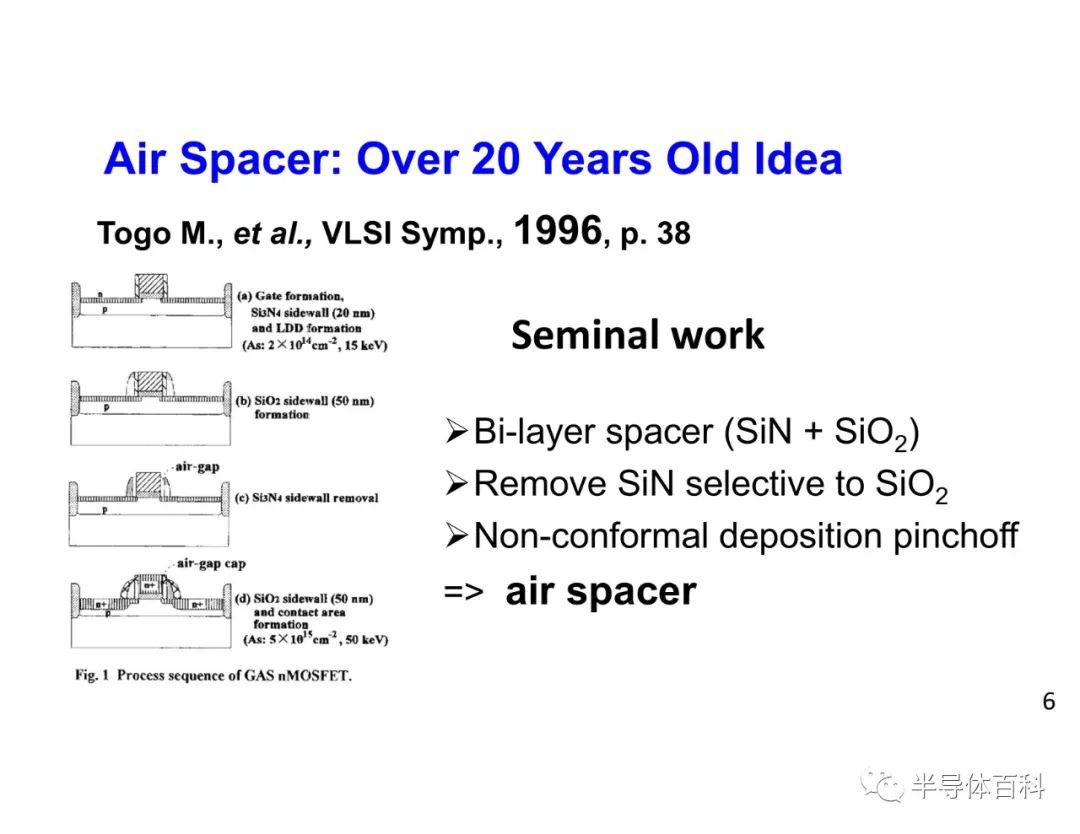

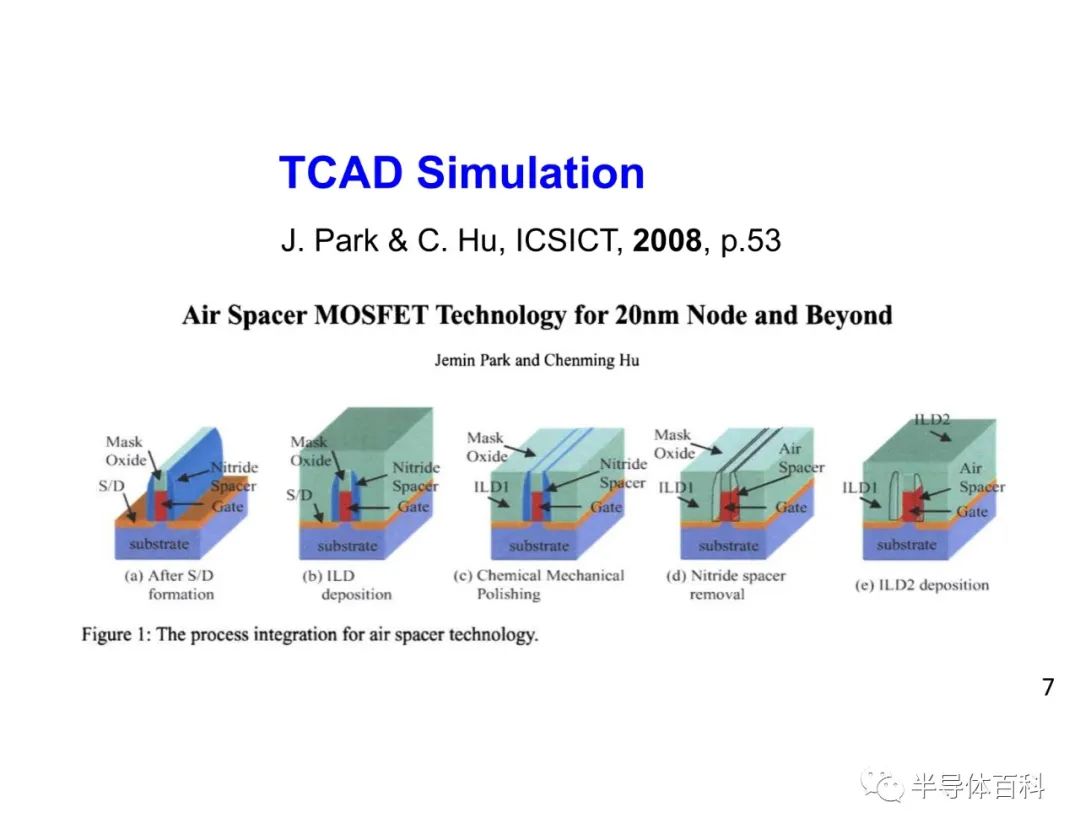

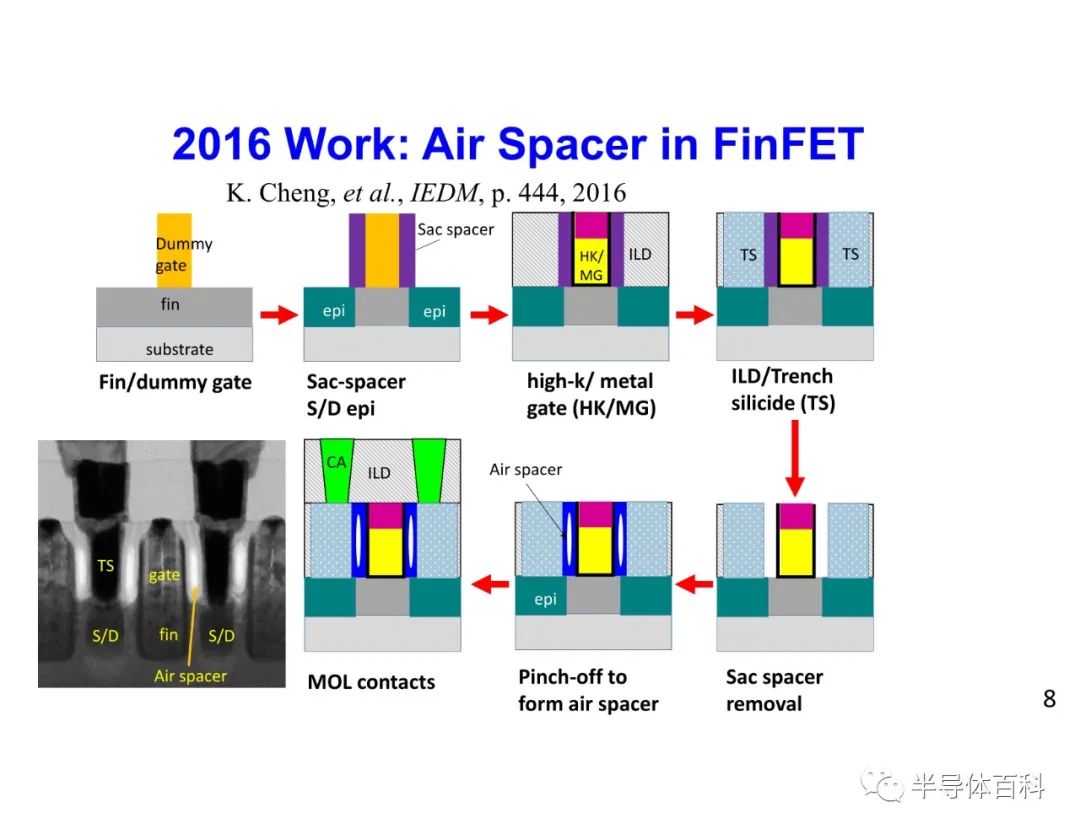

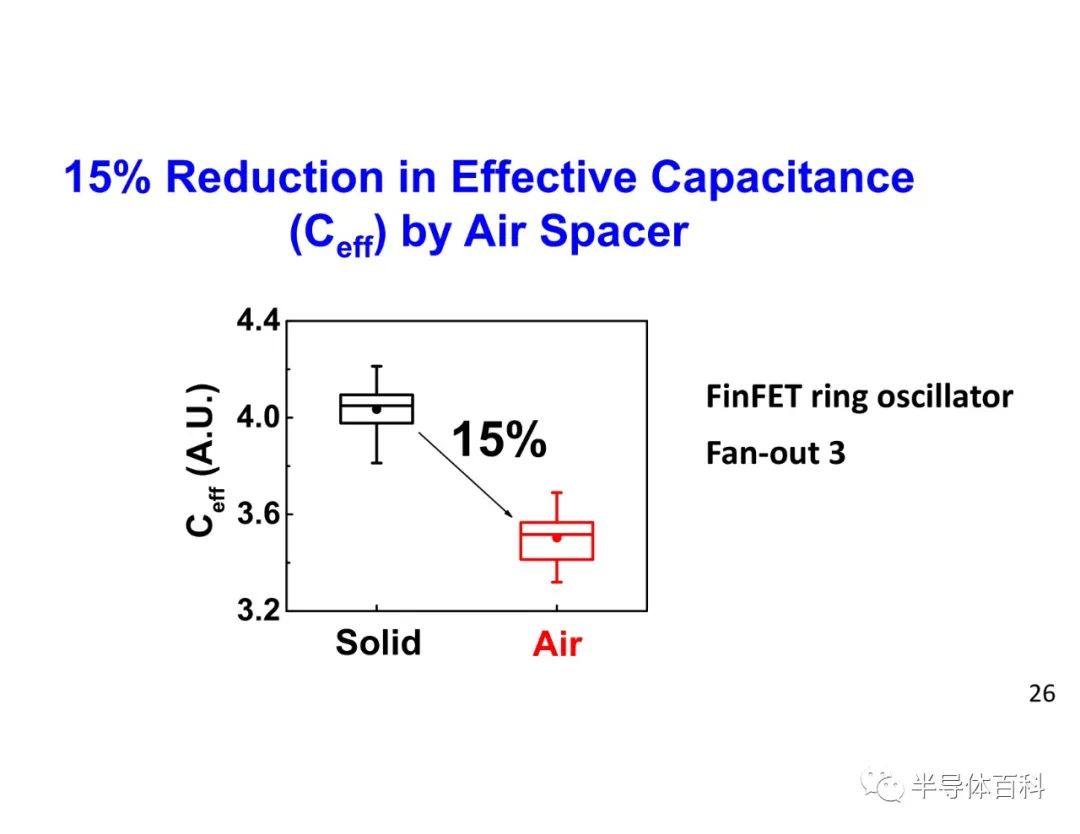

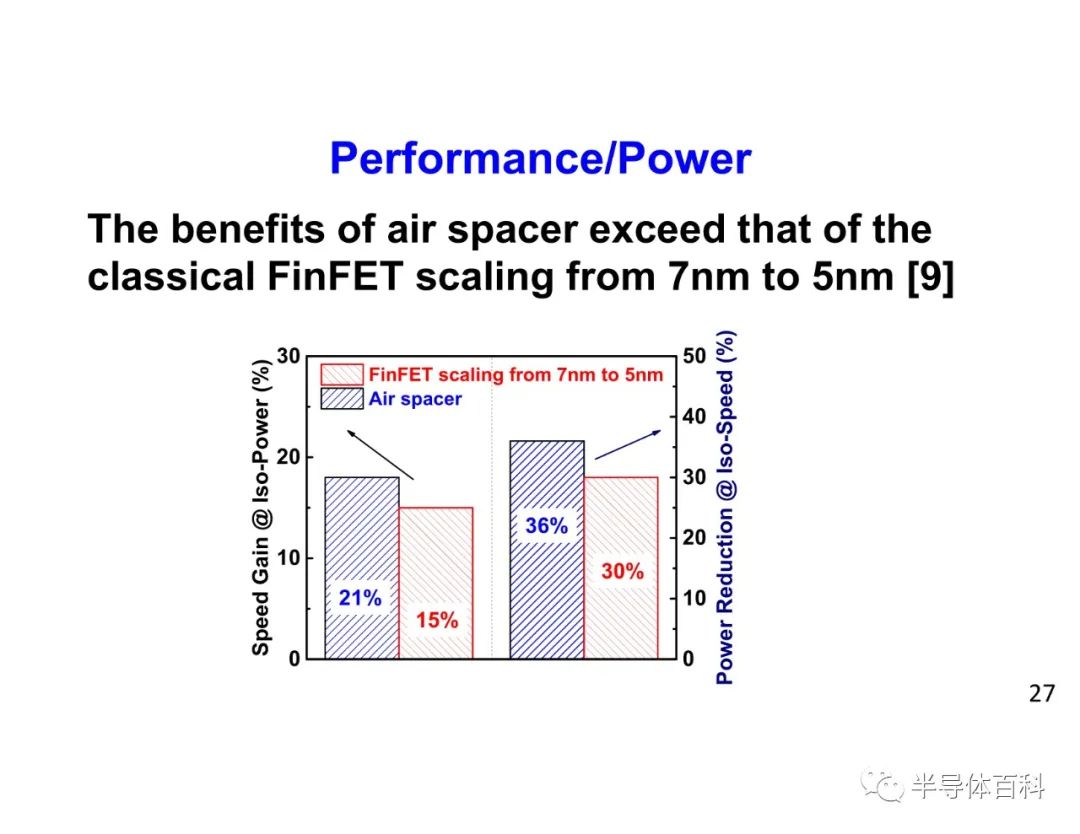

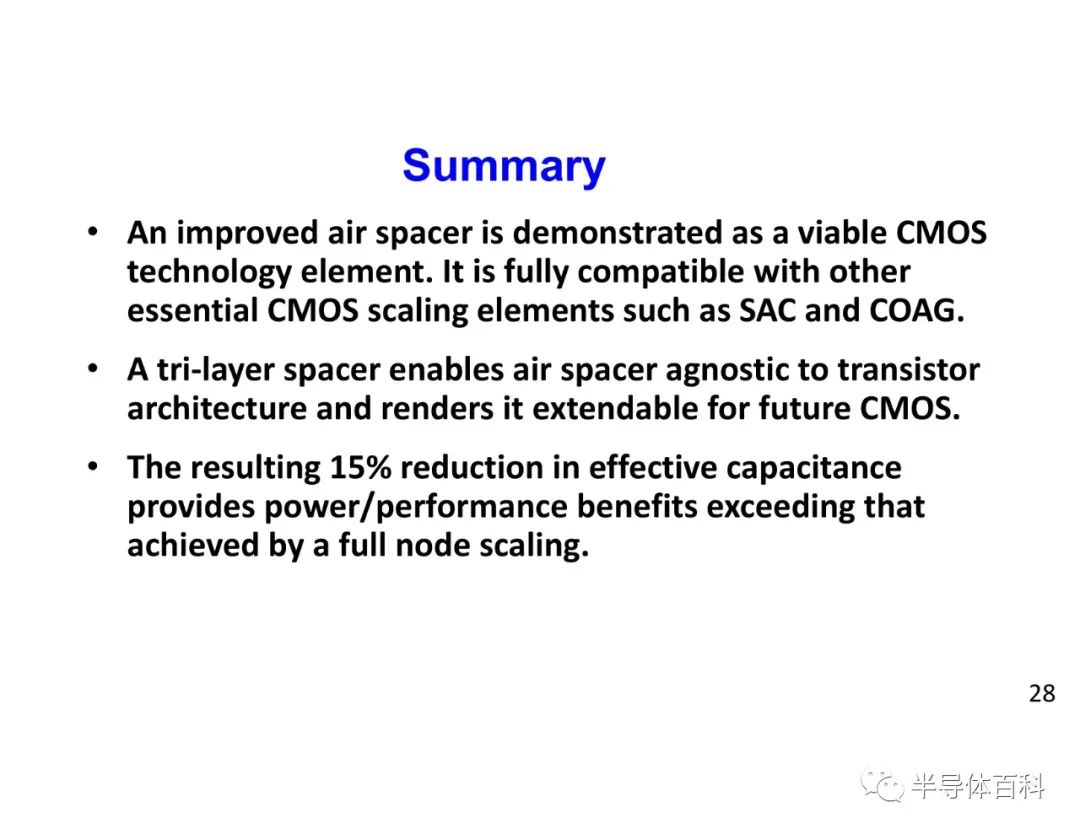

業界早已認識到,將Air Gap用作晶體管的柵極側墻上的絕緣膜間隔物的一部分,是減少寄生電容的有效方法。 IBM研究人員報告了一種改進的Air gap 側墻技術,該技術兼容具有自對準觸點(SAC)技術和COAG技術的FinFET晶體管。在新的集成方法中,Air Gap是在形成MOL接觸(SAC和COAG)之后形成的,并且無論晶體管結構如何,都可以形成Air Gap,這使得該技術應用空間非常廣闊。 在假定該技術降低了15%的有效電容(Ceff)的情況下,演算得出采用該技術的7nm工藝在功率和性能上將優于5nm工藝。

圖4,(a)是3D概念圖,(b)SAC和COAG之后形成的具有Air gap 的FinFET TEM圖。

圖5,后Air Gap Spacer 工藝流程圖,由編者摘自對應演示文稿 以下是對應演示文稿 IMEC

CEA-Leti

IBM

責任編輯:lq

-

晶體管

+關注

關注

77文章

9694瀏覽量

138229 -

IMEC

+關注

關注

0文章

57瀏覽量

22243 -

量子計算

+關注

關注

4文章

1099瀏覽量

34951

原文標題:【2020 VLSI】先進CMOS工藝一覽

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

臺積電產能爆棚:3nm與5nm工藝供不應求

AI芯片驅動臺積電Q3財報亮眼!3nm和5nm營收飆漲,毛利率高達57.8%

消息稱AMD將成為臺積電美國廠5nm第二大客戶

臺積電3nm/5nm工藝前三季度營收破萬億新臺幣

三星將為DeepX量產5nm AI芯片DX-M1

消息稱臺積電3nm/5nm將漲價,終端產品或受影響

三星擬升級美國晶圓廠至2nm制程,與臺積電競爭尖端市場

臺積電升級4nm N4C工藝,優化能效與降低成本

臺積電高雄與寶山晶圓廠擴建,1.4nm(A14)工藝制造增添兩階段

IMEC推出針對N2節點的設計探路PDK

IMEC針對5nm及以下尖端工藝的BPR技術

IMEC針對5nm及以下尖端工藝的BPR技術

評論