RF電路布局要想降低寄生信號,需要RF工程師發揮創造性。記住以下這八條規則,不但有助于加速產品上市進程,而且還可提高工作日程的可預見性。

1

接地通孔應位于接地參考層開關處

流經所布線路的所有電流都有相等的回流。耦合策略固然很多,不過回流通常流經相鄰的接地層或與信號線路并行布置的接地。在參考層繼續時,所有耦合都僅限于傳輸線路,一切都非常正常。不過,如果信號線路從頂層切換至內部或底層時,回流也必須獲得路徑。

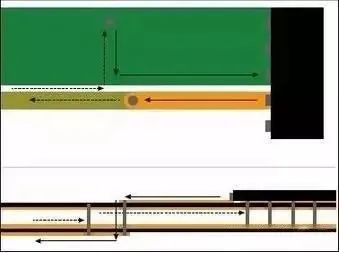

圖1就是一個實例。頂層信號線路電流下面緊挨著就是回流。當它轉移到底層時,回流就通過附近的通孔。不過,如果附近沒有用于回流的通孔時,回流就要通過最近可用的接地通孔。

更遠的距離會產生電流環路,形成電感器。如果這種不必要的電流路徑偏移,碰巧又同另一條線路交叉,那么干擾就會更嚴重。這種電流環路其實相當于形成了一個天線!

圖1:信號電流從器件引腳經過通孔流到較低層。回流在被迫流向最近通孔改變至不同參考層之前位于信號之下。

接地參考是最佳策略,但高速線路有時候可布置在內部層上。接地參考層上下都放置非常困難,半導體廠商可能會受到引腳限制,把電源線安放在高速線路旁邊。參考電流要是需要在非DC耦合的各層或各網之間切換,應緊挨著開關點安放去耦電容。

2

將器件焊盤與頂層接地連接起來

許多器件在器件封裝底部都采用散熱接地焊盤。在RF器件上,這些通常都是電氣接地,而相鄰焊盤點有接地通孔陣列。可將器件焊盤直接連接至接地引腳,并通過頂層接地連接至任何灌銅。如有多個路徑,回流會按路徑阻抗比例拆分。通過焊盤進行接地連接相對于引腳接地而言,路徑更短、阻抗更低。

電路板與器件焊盤之間良好的電氣連接至關重要。裝配時,電路板通孔陣列中的未填充通孔也可能會抽走器件的焊膏,留下空隙。填滿通孔是保證焊接到位的好辦法。

在評測中,還要打開焊接掩模層確認沒有焊接掩模在器件下方的電路板接地上,因為焊接掩模可能會抬高器件或使其搖擺。

3

無參考層間隙

器件周邊到處都是通孔。電源網分解成本地去耦,然后降至電源層,通常提供多個通孔以最大限度減少電感,提高載流容量,同時控制總線可降至內層。所有這些分解最終都會在器件附近完全被鉗住。

每個這些通孔都會在內接地層上產生大于通孔直徑自身的禁入區,提供制造空隙。這些禁入區很容易在回流路徑上造成中斷。一些通孔彼此靠近則會形成接地層溝,頂層CAD視圖看不見,這將導致情況進一步復雜化。

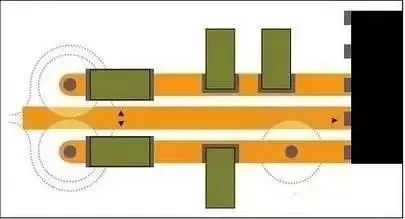

圖2兩個電源層通孔的接地層空隙可產生重疊的禁入區,并在返回路徑上造成中斷。回流只能轉道繞過接地層禁入區,形成現在常見的發射感應路徑問題。

圖2:通孔周圍接地層的禁入區可能重疊,迫使回流遠離信號路徑。即便沒有重疊,禁入區也會在接地層形成鼠咬阻抗中斷。

甚至“友好型”接地通孔也會為相關金屬焊盤帶來電路板制造工藝要求的最小尺寸規格。通孔如果非常靠近信號線路,就會產生好像頂層接地空隙被老鼠咬掉一塊一樣的侵蝕。圖2是鼠咬示意圖。

由于禁入區由CAD軟件自動生成,通孔在系統電路板上的使用又很頻繁,因此先期布局過程幾乎總會出現一些返回路徑中斷問題。

布局評測時要跟蹤每條高速線路,檢查相關回流層以避免中斷。讓所有可在任何區域產生接地層干擾的通孔更靠近頂層接地空隙是一個不錯的方法。

4

保持差分線路的差分性

回流路徑對信號線路性能至關重要,其應視為信號路徑的一部分。與此同時,差分對通常沒有緊密耦合,回流可能流經相鄰層。兩個回流必須通過相等的電氣路徑布線。

即便在差分對的兩條線路不緊密耦合時,鄰近與共享型設計限制也會讓回流處于相同層。要真正保持低寄生信號,需要更好的匹配。差分組件下接地層的斷流器等任何計劃結構都應是對稱的。

同樣,長度是否匹配可能也會產生信號線路中的波形曲線問題。回流不會引起波形曲線問題。一條差分線路的長度匹配情況應在其它差分線路中體現。

5

RF信號線路附近沒有時鐘或控制線路

時鐘和控制線路有時可視為沒什么影響的鄰居,因為其工作速度低,甚至接近DC。不過,其開關特性幾乎接近方波,可在奇數諧波頻率下生成獨特的音調。

方波發射能源的基本頻率雖然不會產生什么影響,但其銳利的邊緣可能會有影響。在數字系統設計中,轉折頻率可估算必須要考慮的最高頻率諧波,計算方式為:Fknee=0.5/Tr,這里的Tr是上升時間。

請注意,是上升時間,而不是信號頻率。不過銳利邊緣的方波也有強大的高階奇數諧波,其可能只在錯誤頻率下下降并耦合在RF線路上,違反嚴格的傳輸掩模要求。

時鐘和控制線路應由內部接地層或頂層接地灌流(ground pour)與RF信號線路隔離。如果不能使用接地隔離信號,那么線路布線應確保直角交叉。因為時鐘或控制線路發射的磁通線路會圍繞干擾源線路的電流形成放射柱形等高線,它們將不會在接收器線路中產生電流。

放慢上升時間不但可降低轉折頻率,而且還有助于減少干擾源的干擾,但時鐘或控制線路也可充當接收器線路。接收器線路仍可作為將寄生信號導入器件的導管。

6

使用接地隔離高速線路

微波傳輸帶與帶線大多數都與相鄰接地層耦合。一些通量線路仍沿水平方向散發,并端接于相鄰跡線。一條高速線路或差分對上的音調在下一條跡線上終結,但信號層上的接地灌流會為通量線路帶來較低阻抗的終點,讓鄰近跡線不受音調干擾。

時鐘分布或合成器設備路由出來、用于承載相同頻率的跡線集群可能相鄰而行,因為干擾源音調已經存在于接收器線路上。不過,分組的線路最終會分散。

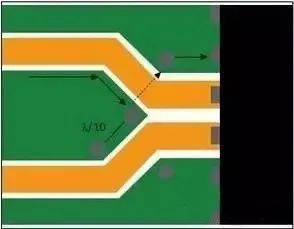

分散時,應在分散線路之間提供接地灌流,并在其開始分散的地方灌入通孔,以便感應回流沿著額定回流路徑流回。在圖3中,接地島末端的通孔可使感應電流流到參考層上。接地灌流上其它通孔之間的間隔不要超過一個波長的十分之一,以確保接地不會成為共振結構。

圖3:差分線路分散處的頂層接地通孔為回流提供流動路徑。

7

不要在噪聲較大的電源層進行RF線路布線

音調進入電源層就會擴散到每個地方。如果雜散音調進入電源、緩沖器、混頻器、衰減器和振蕩器,就會對干擾頻率進行調制。

同樣,當電源到達電路板時,它還沒有徹底被清空而實現對RF電路系統的驅動。應最大限度減少RF線路在電源層的暴露,特別是未過濾的電源層。

鄰近接地的大型電源層可創建高質量嵌入式電容,使寄生信號衰減,并用于數字通信系統與某些RF系統。另一種方法是使用最小化電源層,有時更像是肥大跡線而不能說是層,這樣RF線路更容易徹底避開電源層。

這兩種方法都可行,不過決不能將二者的最差特性湊在一起,也就是既使用小型電源層,又在頂部走線RF線路。

8

讓去耦靠近器件

去耦不僅有助于避免雜散噪聲進入器件,還可幫助消除器件內部生成的音調,避免其耦合到電源層上。去耦電容越靠近工作電路系統,效率就越高。本地去耦受電路板跡線的寄生阻抗干擾較小,較短的跡線支持較小的天線,減少有害音調發射。

電容器安放要結合最高自共振頻率,通常最小值、最小外殼尺寸、最靠近器件,以及越大的電容器,離器件越遠。在RF頻率下,電路板背面的電容器會產生通孔串連接地路徑的寄生電感,損失大量噪聲衰減優勢。

9

總結

通過電路板布局評測,我們可發現可能發射或接收雜散RF音調的結構。要跟蹤每一條線路,有意識地明確其回流路徑,確保它能夠與線路并行,特別是要徹底檢查過渡。

此外,還要將潛在干擾源與接收器隔離。按照一些簡單直觀的規則降低寄生信號,可加速產品發布,降低調試成本。

責任編輯:lq

-

電路板

+關注

關注

140文章

4988瀏覽量

98485 -

RF電路

+關注

關注

1文章

74瀏覽量

17158 -

寄生信號

+關注

關注

0文章

10瀏覽量

8479

原文標題:RF電路寄生信號如何降低,這8條規則收藏好了!

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

合金電阻的寄生電感及其影響

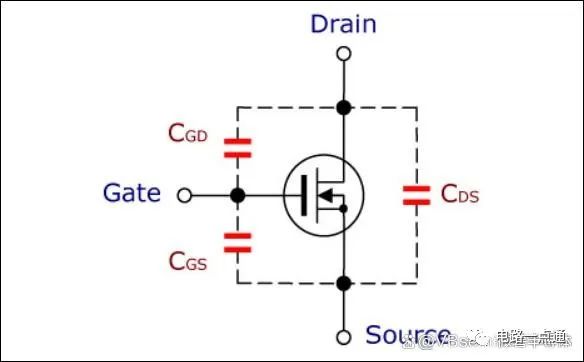

MOS管寄生參數的定義與分類

MOS管寄生參數的影響

深入解析晶振時鐘信號干擾源:寄生電容、雜散電容與分布電容

使用rf studio的時候需要配置偏置模式,這個偏置電路是由內部還是外部提供的?

如何最大程度降低開關電源中的寄生參數

什么是寄生電感?如何計算過孔的寄生電感?

RF電路寄生信號如何降低

RF電路寄生信號如何降低

評論