本文來梳理ADC兩個方面的內容,常見的ADC類型及原理,以及可能容易掉進去的坑。

談談我為什么整理這個文章吧,工程師往往關注點更多在于功能,而忽略了性能。為什么會忽略性能呢?因為可能缺少對于原理的深入探究,那么使用時可能失之毫厘,謬以千里。性能往往不好,穩定性也可能不佳。帽子扣大點說是缺少匠心,其實這也是大學教育非常不足的地方。而我個人的觀點是,即使是工程師也需要一點科學家的素養,希望小伙伴們都盡可能的將一些技術要點的本原深挖,不要浮于表面。這也是國內科技領域現今急需要去發展提升的地方,如果每個技術領域的我輩中人,都能深耕自己的領域,探求技術的本原,又何懼美帝如此猖狂囂張!

我期望我能業余做好一個小小的技術分享傳播者,如果你讀到本文,真心覺得有價值,也請傳播給他人。當然我做這個公眾號也期望有一天能稍稍改善我的生活,但是坦蕩地說,所有文章的技術要點都屬于無私分享。如果達成改善家人生活所愿,則我心歡喜,不成也無妨。做一個快樂的分享者吧!

羅嗦了一通廢話,但這是公眾號,不管受眾多少,傳播技術的同時,也期望能傳播一些技術觀以共勉!

ADC類型

積分型ADC

優點:

積分型ADC分辨率高,位數可做到12位甚至更高

線性度非常好。本質上,輸入端與一個集成的參考電壓相比較來決定輸出端,所以線性度將取決于比較器的精度。

電路實現拓撲簡單,用于實現這些設備的元件相對較少,因此電路相對簡單且生產成本較低。

缺點:

主要缺點是轉換速度慢。N位ADC,輸出可能需要長達2個N的時鐘周期來轉換單個采樣點

轉換原理都是基于對電壓積分并將積分后電壓與另一電壓比較以控制計數,計數輸出即為ADC輸出。積分對象要么是基于參考電壓,要么是基于參考電壓和輸入電壓。

主要用于傳感器應用和諸如電壓表和電流表等設備,在這些設備中,精度比速度更重要。換句話說積分型ADC采樣速度比較低,但精度非常高

積分型ADC有不同的種類,常見的有單、雙斜率積分等。增加一個“斜率”,以犧牲轉換時間為代價而增加精度。

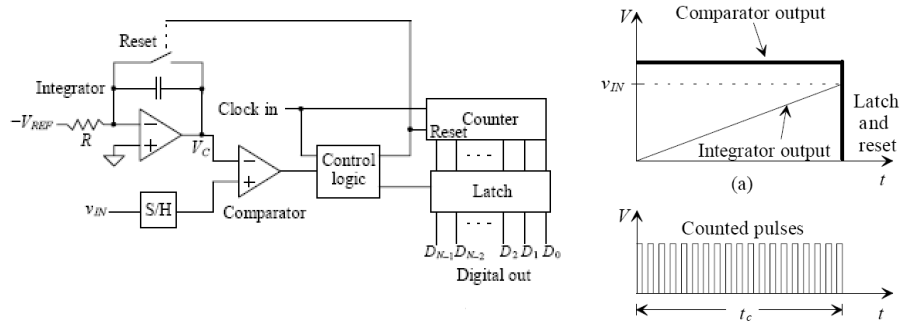

單斜率積分ADC

比較器將輸入電壓與集成基準電壓的值進行比較(請注意,由于已連接至運算放大器的反相輸入,因此我們將設為負)。同時計算時鐘周期數。當積分器輸出等于時,比較器輸出邏輯“ 0”,觸發計數器和積分器復位,鎖存器保持數字輸出。

這就是轉換時間,知道為啥說這種積分型ADC慢了吧。來看下最差的情況吧,假設輸入電壓,假定,假定是20位ADC,那么!

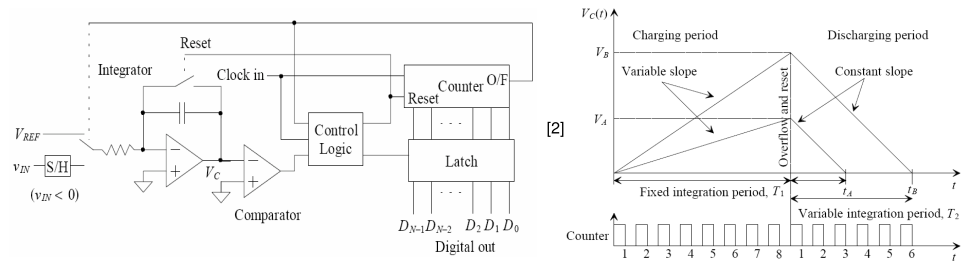

雙斜率積分ADC

雙斜率ADC與單斜率ADC的不同之處在于,現在將與地進行比較,并集成了兩個電壓和。剛開始時,負輸入連接到積分器,使斜升直到計數器溢出。由于在反相輸入會切換到一個負值進行積分,因此積分器輸出將始終為正且大于零,因此計數器將繼續運行直到溢出為止,這需要2N個時鐘周期(= T1)。

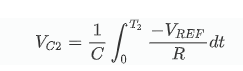

在T2時刻,將等于與之和,且為0,也即:

則

因此,即為ADC轉換的原理,雙斜率比單斜率ADC更慢,由于執行了兩次積分, 與積分器斜率相關的誤差將被抵消,從而從原理上提高了精度。

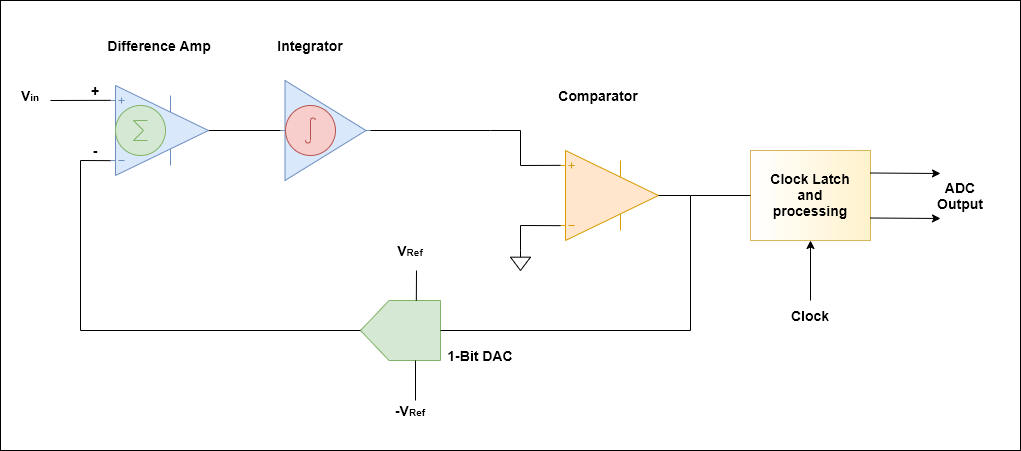

Sigma-Delta Σ-? ADC

從輸入端開始,差動放大器產生的輸出為Vin與1位DAC輸出之間的差。1位DAC的輸出可以是以下兩個值之一:或。在此拓撲結構中,可將積分器視為取前一個值和當前輸入值的移動平均值。

因此,假設剛開始時比較器正向段固定在高于0V的很小一值,比較器反轉。其值將為高或1。然后,DAC輸出將為。在下迭代中,將從的當前值中減去該值。由于先前的值為0V,因此積分器輸出現在將為– Vref。此時,比較器輸出將為0,而DAC輸出將為。

在下一個采樣中,由于前一個值為,積分器輸出將為0,并且差動放大器實際上將減去,從而將加到 .比較器輸出將為1。

此過程繼續迭代進行,因此,對于0V輸入,比較器輸出將為101010…的穩定流。記住邏輯1表示,邏輯0表示,那么如對N個樣本進行采樣并取平均值,則很容易看出平均值為0V。比較器之后的處理塊將簡單地將其輸出為單個值0000…,假設參考值為(~)或2 x。

現在,假設為1V,這是一個5V ADC。為±2.5V。按照與之前相同的步驟進行迭代操作,輸出將為:1011101…輸出為1.07V。

概括起來:

Σ-? ADC 對所處理信號進行過采樣(這個概念見模數采樣知多少),并對待處理信號進行低通濾波。通常,在過濾器之后使用Flash ADC轉換的比特數小于所需的比特數。所產生的信號連同由FLASH離散電平產生的誤差,被反饋回并從輸入中做差然后輸入到濾波器。這個負反饋的可對噪聲形成抑制作用,使它不出現在期望的信號頻率。ADC之后的數字濾波器(利用抽取濾波器)可降低采樣率,濾除不想要的噪聲信號并提高輸出分辨率(故稱為sigma-delta調制,也稱為delta-sigma調制)。

Flash ADC也稱直接比較型

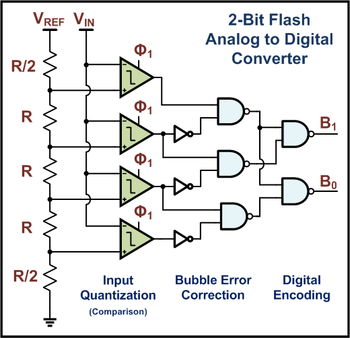

FLASH ADC的原理可能是最容易理解的。下圖是一個兩位ADC的示意圖,由許多比較器組成,每個比較器都被提供了比上一個基準值高一個位值的基準電壓。因此,對于一個8位ADC,需要256個這樣的比較器。對于10位,則需要1024。

FLASH ADC(直接比較型)速度很快。它直接轉換輸入,而不需要任何采樣或繁重的后期處理。問題是,它需要很多比較器,而且很多比較器占用了芯片上的大量硅空間。因此,只有在需要其他ADC實現方法無法達到的極高速度時才使用Fash ADC。

二分法在硬件中體現

實際應用中,還有一個變種比較常用,半 FLASH ADC。它使用兩步的過程來減少實際轉換鏈中所需的轉換器數量:

首先,將輸入信號與恰好位于半的電平集進行比較。如果它更低,那么最高有效的位MSB,被設置為0,輸入被饋送到一個比較器鏈與參考電壓設置為,以轉換得到其余的位。

如果輸入信號高于,則將MSB設置為1,從輸入信號中減去。比較器鏈再次用于獲取剩余的位。所以,本質上,半步FLASH ADC,以犧牲一個額外的比較,來節省一半比較器。這種思路還可以繼續推演擴展,比如4分 FLASH ADC等等。

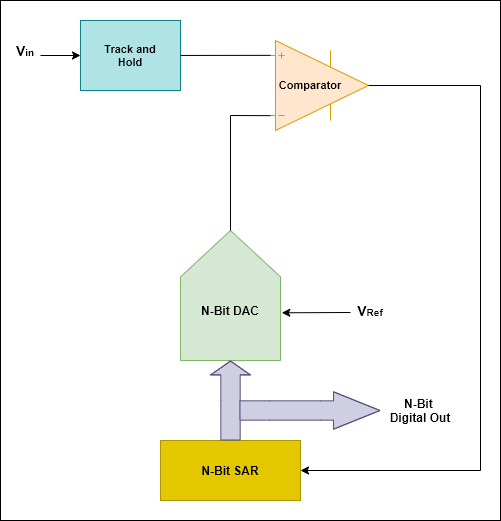

逐次逼近寄存器SAR

逐次逼近寄存器(Successive Approximation Register):逐次逼近ADC使用比較器逐次縮小包含輸入電壓的范圍。在每個連續的步驟中,轉換器將輸入電壓與內部數字與模擬轉換器的輸出進行比較,后者可能表示所選電壓范圍的中點。在這個過程的每一步,近似都被存儲在一個逐次逼近寄存器(SAR)中。例如,假設輸入電壓為6.3 V,初始范圍為0到16v。對于第一步,輸入6.3 V與8v (0-16V范圍的中點)進行比較。比較器報告輸入電壓小于8v,因此SAR被更新為將范圍縮小到0 - 8v。

第二步,將輸入電壓與4v (0 - 8v的中點)進行比較,比較器報告輸入電壓高于4v,因此更新SAR以反映輸入電壓在4 - 8v范圍內。第三步,輸入電壓與6v比較(4v與8v的一半);比較器報告輸入電壓大于6伏,搜索范圍變為6 - 8伏。繼續這些步驟,直到達到預期的解決方案為止。

其拓撲結構如下,

為了直觀,看看前文的動圖:

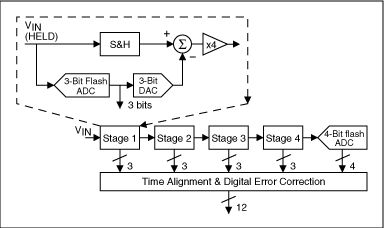

Pipelined ADC

流水線ADC(也稱為子例程量化器)使用兩個或多個流水線。首先,進行粗略的轉換。第二步,用數模轉換器(DAC)確定輸入信號的差異。然后將這個差異轉換為更細的值,并在最后一步中合并結果。這可以被認為是后續逼近ADC的一種改進,其中反饋參考信號由整個范圍的比特(例如,4比特)的中間轉換組成,而不僅僅是下一個最重要的比特。結合逐次逼近法和flash adc的優點,該類型具有速度快、分辨率高、模具尺寸小等優點。

在這個原理圖中,模擬輸入VIN首先被采樣并由采樣保持器(S&H)保持穩定,而第一階段的flash ADC將其量化為三位。然后將3位輸出饋給3位DAC(精確到12位),然后從輸入中減去模擬輸出。這個“剩余量”擴大4倍并被送入下一階段(第二階段)。這個增加的剩余量繼續通過下級流水線,每一階段提供3位,直到它到達4位flash ADC,將解析最后的4LSB位。

因為每個階段的位是在不同的時間點確定的,所以相同樣本對應的所有位在被饋送到數字錯誤校正邏輯之前都與移位寄存器進行了時間對齊。請注意,當一個流水完成對輸入樣本的處理,確定本流水采集位并將殘差傳遞到下一個流水時,它便可以開始處理從每個流水中嵌入的采樣保持器接收到的下一個樣本。這種流水線操作是高吞吐量的原因,這也是流水的概念。

總結一下

熟悉各類ADC的意義,因為如前文所說,嵌入式設備免不了需要采集物理世界的模擬信號。信號各具特點,有的頻率高,有的噪聲多,有的需要精度高但速度可能不要很快等等。這里整理幾種常見ADC(當然還有其他種類比如電荷平衡原理ADC、分時ADC、FM ADC、時間拉伸ADC、增量編碼ADC、Wilkinson ADC等等)的原理及特點,了解各類ADC的基本特點,有助于進行器件選型、系統設計。

責任編輯:xj

原文標題:常見類型ADC選型必知!

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

寄存器

+關注

關注

31文章

5359瀏覽量

120808 -

adc

+關注

關注

98文章

6525瀏覽量

545226 -

積分器

+關注

關注

4文章

100瀏覽量

28478

原文標題:常見類型ADC選型必知!

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

常見電子開關類型及特點

不同類型傳感器的優缺點 常見傳感器類型及其應用

ADC高速采樣電路設計詳解之STM32踩坑

常見的ADC類型及原理,以及可能容易掉進去的坑

常見的ADC類型及原理,以及可能容易掉進去的坑

評論