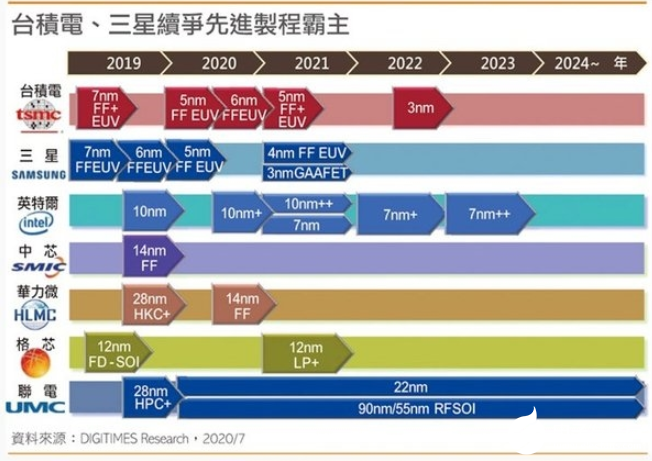

從蘋果在2020年9月的iPad Pro上率先采用5nm工藝的A14 Bionic,隨后華為、高通、三星也相繼推出5nm工藝的旗艦級SoC。

WikiChips分析后估計,臺積電5nm的柵極間距為48nm、金屬間距30nm、鰭片間距25-26nm,單元高度約為180nm。

從而推算出臺積電5nm的晶體管密度為1.713億個每平方毫米,比初代7nm每平方毫米9120萬個增加88%,臺積電官方宣傳的數字是84%。

第一款出貨的5nm芯片,是蘋果2020年10月份發布并上市的A14仿生芯片,這款SoC的晶體管數量達到118億個,比A13多大約40%。

而且使6核CPU性能提升40%,4核圖形GPU性能提升30%,功耗降低30%。

第二款華為麒麟9000則集成153億個晶體管,8核CPU、24核GPU和NPU AI處理器,官方稱CPU性能提升25%,GPU提升50%。

按照摩爾定律,芯片的晶體管數量每隔18-24個月翻一番,性能提升一倍。

但隨著半導體技術逐漸接近物理瓶頸,晶體管尺寸的微縮越來越難。

從7nm推進到5nm的手機芯片的表現似乎并不盡人意,不僅在性能提升有限,功耗也面臨“翻車”。特別是很多用戶并不買5nm芯片的賬,認為5nm手機芯片表現并沒有達到預期。

外媒9to5Mac首先指出,部分iPhone 12用戶在使用手機時遇到高耗電問題,待機一夜電量下降20%至40%,哪怕有沒有開啟更多的后臺程序,結果不變。

工藝、IC設計與功耗的平衡

為什么5nm芯片翻車?主要原因是制造工藝不成熟。

在多數人眼中,芯片設計和制造工藝是互相獨立的,但事實并非如此。制造工藝和IC設計不匹配時,便會造成一些問題,包括功耗、性能等。

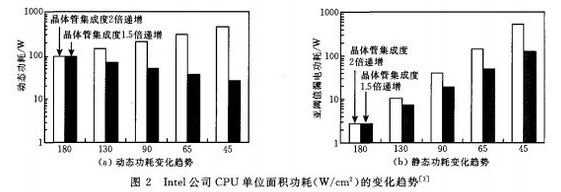

集成電路的功耗可以分為動態功耗和靜態功耗。動態功耗通常指電路狀態變化時產生的功耗,計算方法與普通電路的P=UI物理公式相同,動態功耗受到電壓和電流的影響。

靜態功耗即每個MOS管泄露電流產生的功耗,盡管每個MOS管產生的漏電流很小,但一顆集成上億甚至上百億晶體管的芯片,累計的芯片態功耗就會比較大。

在芯片工藝制程發展過程中,當工藝制程還不太先進時的動態功耗占比大,業界通過放棄最初的5V固定電壓的設計模式,采用等比降壓減慢功耗的增長速度。

減小電壓意味著晶體管的開關會變慢,更加注重性能的廠商即便采用更先進的工藝,也依然保持5V供電電壓,導致功耗增大。

由于對性能需求不同,也就產生了高性能和高能效兩種產品。諸如桌面、服務器等高性能CPU、GPU,便采用5V供電電壓,確保響應速度和性能。

也有廠商選擇降低功耗,雖然會損失一部分性能,無需像高性能產品那般面對高功耗帶來的一系列問題。

但對于普通用戶來說,設備發熱嚴重和高功耗會直接影響使用體驗,芯片散熱差嚴重時會導致芯片異常甚至失效。

所以半導體行業一直將低功耗設計視為芯片行業需要解決的問題之一,如何平衡先進節點下芯片的性能、功耗與面積(PPA)也是芯片設計與制造的挑戰。

理論芯片制程越先進,使用更低的供電電壓產生更低的動態功耗,但工藝尺寸進一步減小后,芯片的典雅來到0.13V以后便難以繼續下降,也導致了近幾年工藝尺寸減小時,動態功耗無法進一步下降。

靜態功耗方面,場效應管的溝道寄生電阻隨節點進步變小,在電流不變的情況下,單個場效應管的功率也變小。但另一方面,單位面積內晶體管數目倍速增長又提升靜態功耗,因此最終單位面積內的靜態功耗可能保持不變。

廠商為追求更低的成本,用更小面積的芯片承載更多的晶體管,看似是達成制程越先進、芯片性能越好、功耗越低。

但實際情況更復雜,有的廠商通過增加核心、也有通過設計更復雜的電路,無論是增加核心還是設計更復雜的電路,都需要面對功耗激增的問題,兩者之間又需要尋找新方法進行平衡。

晶體管結構的升級

國際商業戰略IBS公司主席兼CEO就曾表示,傳統Bulk CMOS工藝技術將在20nm走到盡頭,必須用創新的思路和方法尋找新的替代工藝。

胡正明教授在2020年提出全耗盡型絕緣體上硅(FD-SOI)工藝;目前行業廣泛采用鰭式場效應晶體管(FinFET)則是1999年發明。

FinFET工藝很好的平衡了20nm至5nm之間的芯片性能與功耗,類似于魚鰭式的架構控制電路的連接和斷開,改善電路控制并減少漏電流,晶體管的溝道也隨之大幅度縮短,靜態功耗隨之降低。

Moortec首席技術官曾接受外媒體采訪時稱:當制造工藝升級到16nm或14nm時,處理器速度的到很大的提高,而且漏電流也下降得比較快,以至于我們在使用處理器時能夠用有限的電量做更多的事情。

但從7nm升級到5nm的過程中,漏電情況幾乎與28nm水平相同,以至于廠商需要重新平衡功耗和性能之間的關系。

Cadence的數字和簽準組高級產品管理總監Kam Kittrell也曾表示,很多人都沒有弄清能夠消耗如此多電能的東西,他們需要提前獲取工作負載的信息才能優化動態功耗。

長期以來,我們一直專注于靜態功耗,以至于一旦切換到FinFET節點時,動態功耗就成為大問題。另外多核心的出現也有可能使系統過載,因此必須有更智能的解決方案。”

IC設計公司、制造公司在5nm節點上面臨相同的問題,也是這幾款5nm芯片集體“翻車”的根本。

不成熟的IC設計或制造工藝,都會影響性能與功耗的最大化折中。雖然不排除IC設計公司為追求更好的性能,犧牲功耗。

在FinFET工藝之后,環繞式閘極電晶體(GAA)也開始提上議程,臺積電原本計劃在5nm節點上應用該技術,但考慮到綜合性能和成本之后,選擇繼續使用FinFET工藝。

讓GAA的應用推遲至3nm節點上(4nm節點為5nm改良版),外界對于功耗、性能的平衡并不了解。

高昂的晶圓設計和制造成本

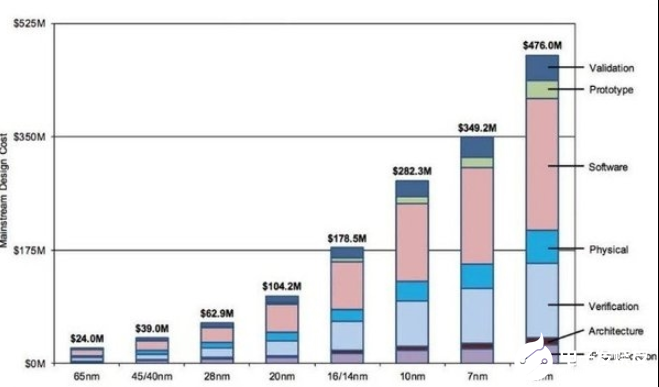

除了功耗和性能之間的平衡外,越先進工藝的晶圓設計費用和制造成本更高。

根據市場研究機構給出的數據顯示,65nm工藝的設計成本需要2400萬美元,28nm工藝則需要6290萬美元,7nm和5nm分別達到3.49億與4.76億美元。

此外,三星也曾對外稱其3nm GAA的成本可能會超過5億美元,預期在2022年大規模,講采用比FinFET更先進的GAAFET 3nm制程芯片。

編輯點評:隨著5nm工藝“翻車”,外界對先進制程的懷疑態度又增一分,首先是先進工藝的性能提升已經難以滿足“摩爾定律”的延續。

高昂的設計成本和制造費用,同樣制約著先進制程的未來,目前采用5nm工藝的都是頂級IC設計公司。

對于半導體越來越接近物理極限,摩爾定律還能持續多久?

責編AJX

-

芯片

+關注

關注

456文章

51062瀏覽量

425810 -

摩爾定律

+關注

關注

4文章

636瀏覽量

79153 -

5nm

+關注

關注

1文章

342瀏覽量

26106

發布評論請先 登錄

相關推薦

石墨烯互連技術:延續摩爾定律的新希望

摩爾定律是什么 影響了我們哪些方面

先進封裝成為AI時代的核心技術發展與創新

SiP封裝產品錫膏植球工藝

后摩爾定律時代,提升集成芯片系統化能力的有效途徑有哪些?

晶圓廠與封測廠攜手,共筑先進封裝新未來

高算力AI芯片主張“超越摩爾”,Chiplet與先進封裝技術迎百家爭鳴時代

“自我實現的預言”摩爾定律,如何繼續引領創新

封裝技術會成為摩爾定律的未來嗎?

半導體先進封裝Wafer技術的深度解析

半導體行業能否走出低谷,中國影響幾何?

摩爾定律的終結:芯片產業的下一個勝者法則是什么?

先進工藝的提升能否延續摩爾定律?

先進工藝的提升能否延續摩爾定律?

評論