本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處。

適用于板卡型號:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

實驗Vivado工程目錄為“pl_read_write_ps_ddr/vivado”。

實驗vitis工程目錄為“pl_read_write_ps_ddr /vitis”。

PL和PS的高效交互是zynq soc開發的重中之重,我們常常需要將PL端的大量數據實時送到PS端處理,或者將PS端處理結果實時送到PL端處理,常規我們會想到使用DMA的方式來進行,但是各種協議非常麻煩,靈活性也比較差,本節課程講解如何直接通過AXI總線來讀寫PS端ddr的數據,這里面涉及到AXI4協議,vivado的FPGA調試等。

FPGA工程師工作內容

以下為FPGA工程師負責內容。

1. ZYNQ的HP端口使用

zynq 7000 SOC的HP口是 High-Performance Ports的縮寫,如下圖所示,一共有4個HP口,HP口是AXI Slave設備,我們可以通過這4個HP接口實現高帶寬的數據交互。

2. 硬件環境搭建

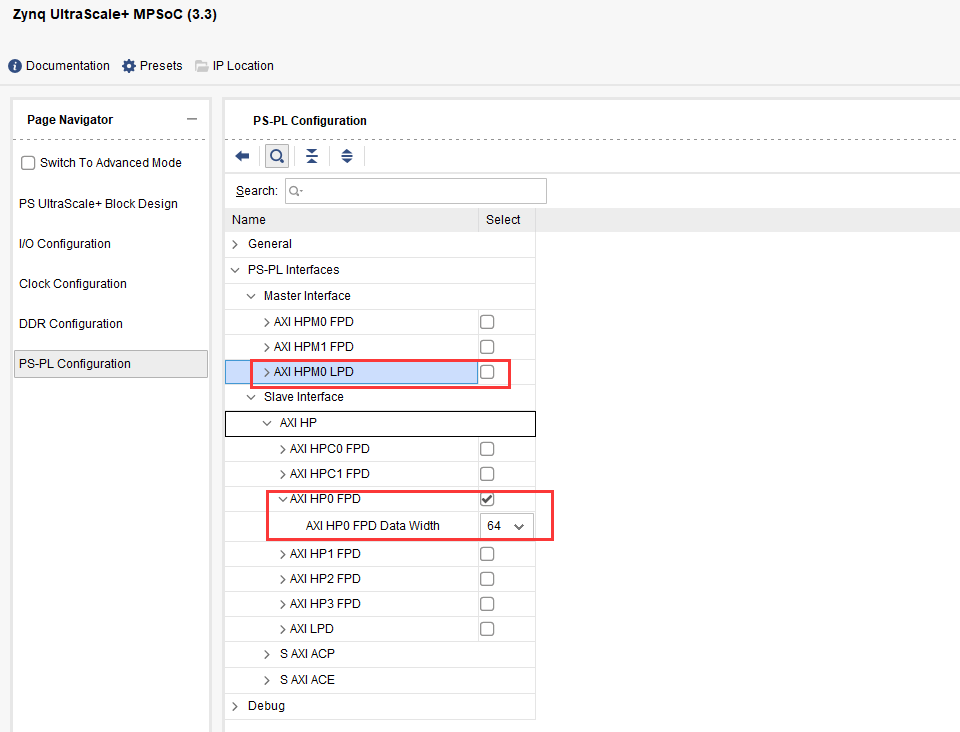

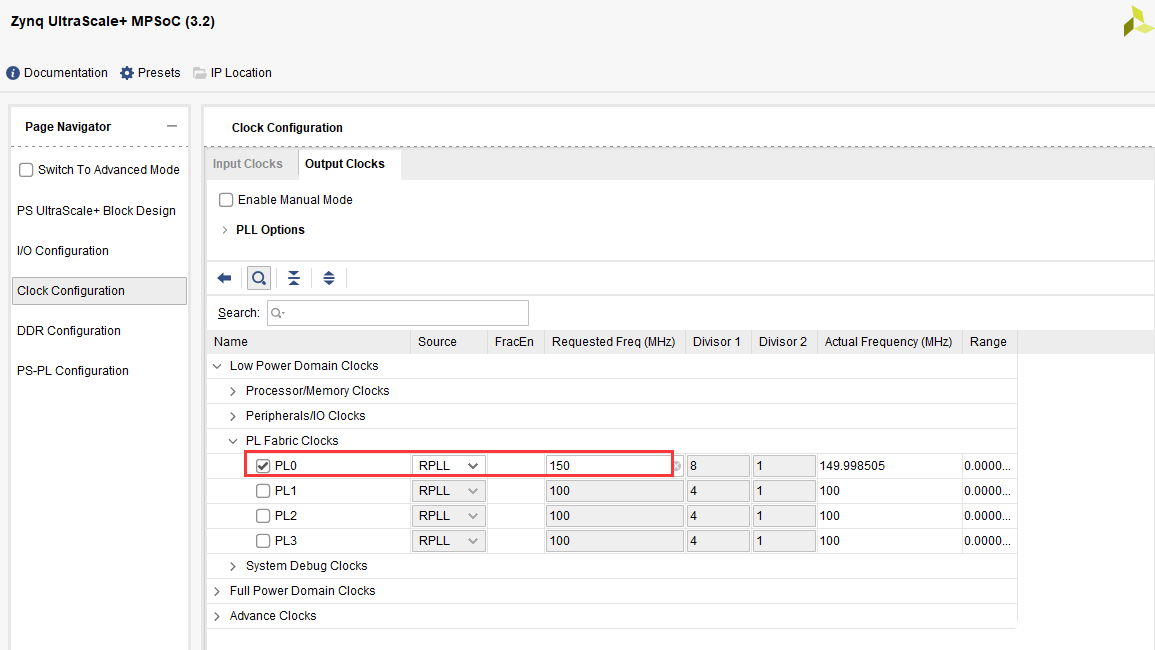

1)基于“ps_hello”工程,在vivado的界面中HP的配置如下圖(HP0~HP3),這里面有使能控制,數據位寬選擇,可選擇32bit、64bit或128bit的位寬。我們的實驗啟用HP0配置為64bit位寬,使用的時鐘是150Mhz,HP的帶寬是150Mhz * 64bit,對于視頻處理,ADC數據采集等應用都有足夠的帶寬。不需要AXI HPM0 LPD,取消選擇。

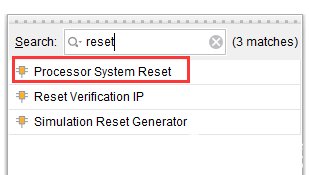

2)添加復位模塊,用于復位

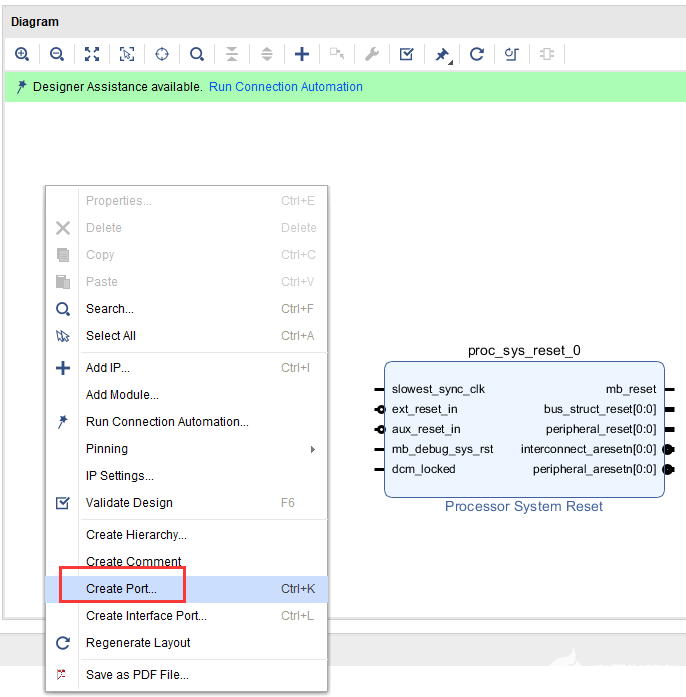

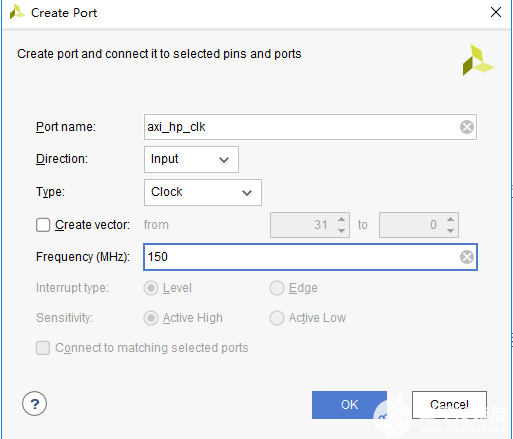

3)在空白處右鍵選擇”Creat Port”

配置如圖

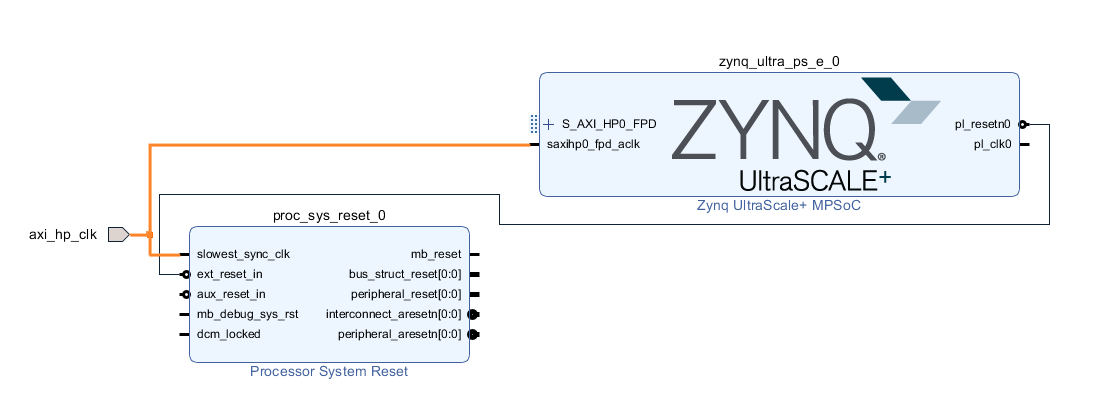

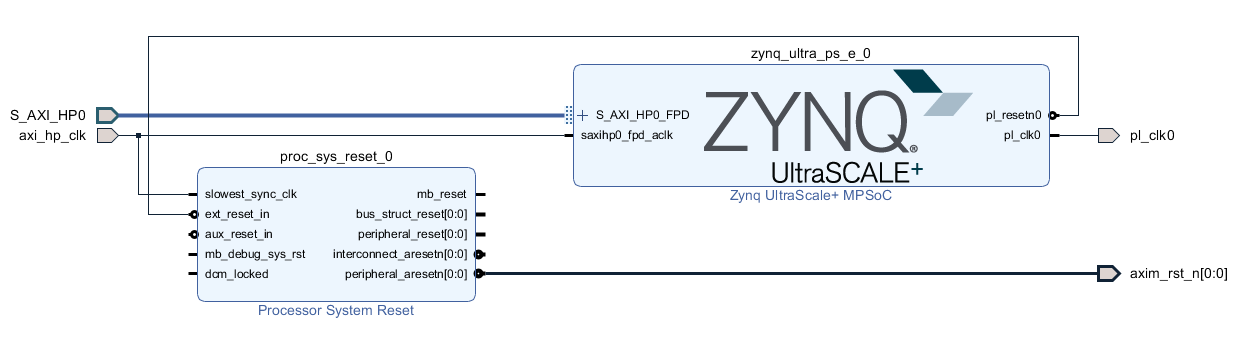

4)連接時鐘和復位

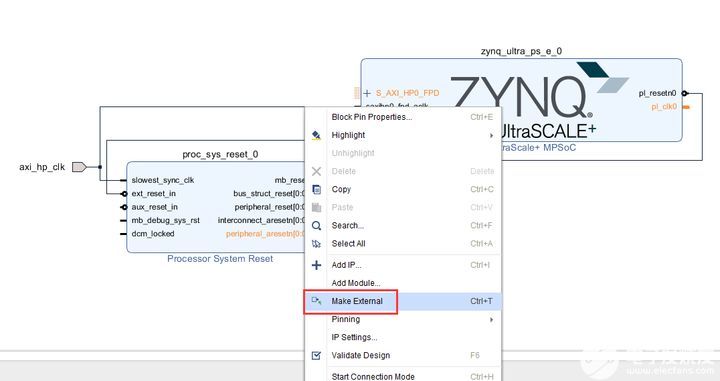

5)選中引腳,點擊Make External,將信號導出

并修改引腳名稱如下圖

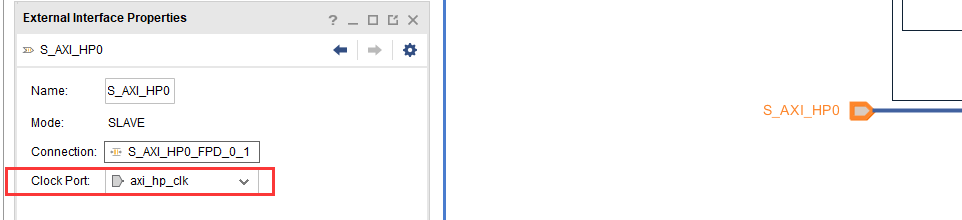

并選擇總線同步時鐘為axi_hp_clk

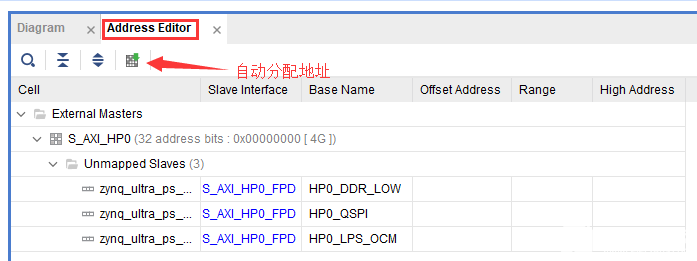

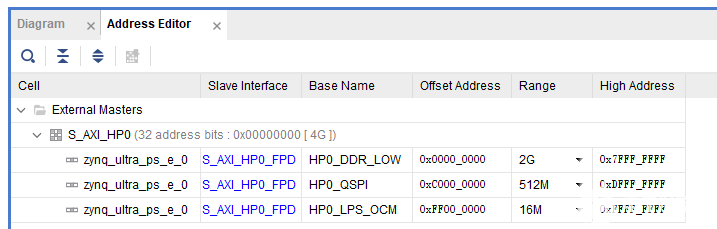

6)點開Address Editor,如果發現地址沒有分配,點擊自動分配地址按鈕

分配后的結果,可以看到訪問DDR, QSPI, OCM的地址空間

保存設計,重新Generate Ouput Product

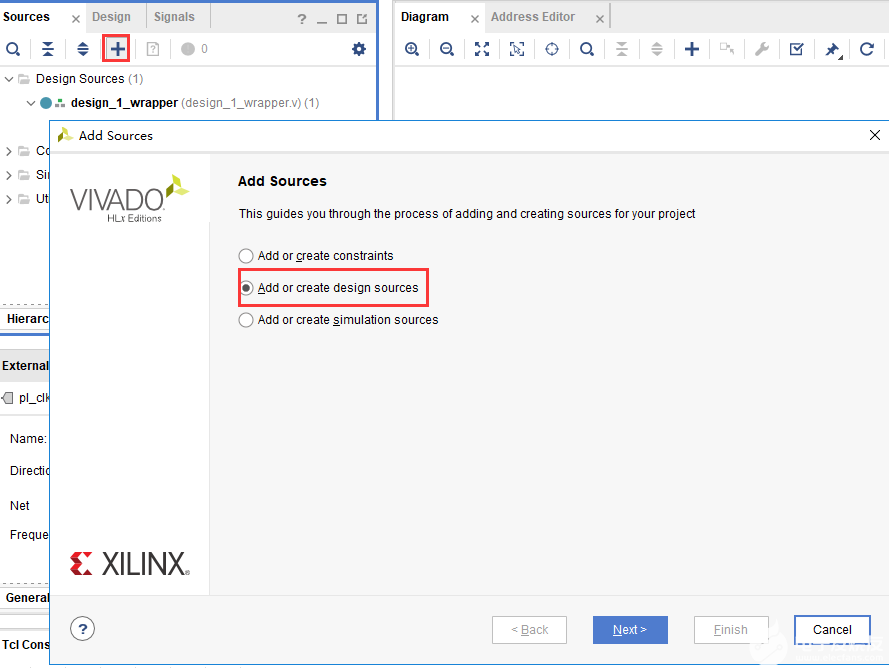

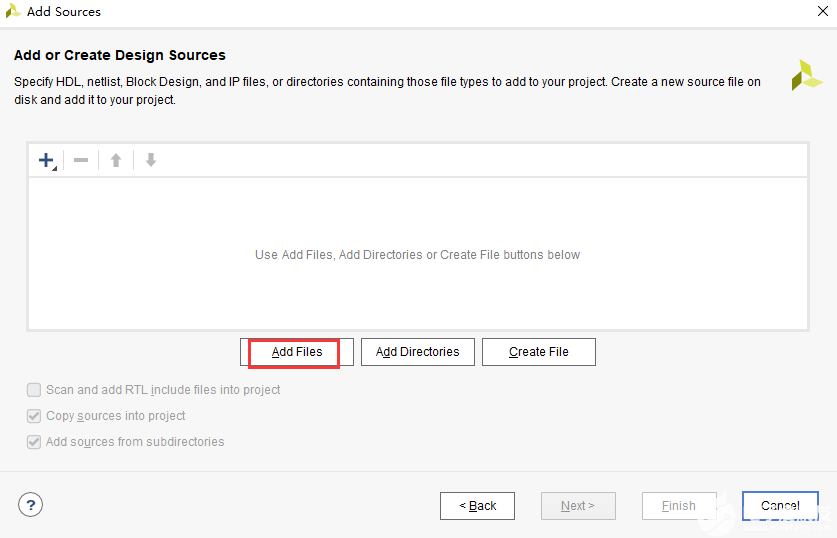

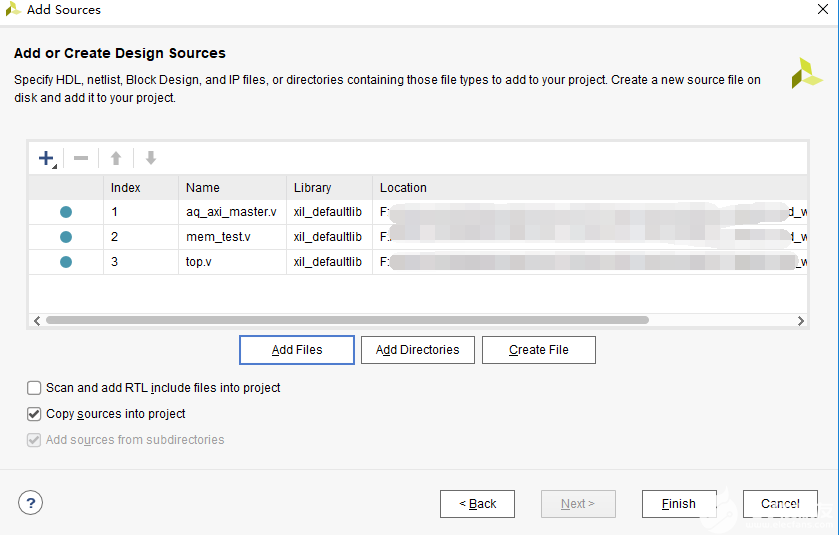

7)添加hdl文件

點擊Finish

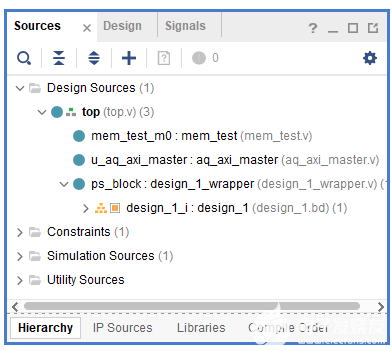

HDL層級關系更新結果

3. PL端AXI Master

AXI4相對復雜,但SOC開發者必須掌握,對于zynq的開發者,筆者建議能夠在一些已有的模板代碼基礎上修改。AXI協議的具體內容可參考Xilinx UG761 AXI Reference Guide。在這里我們簡單了解一下。

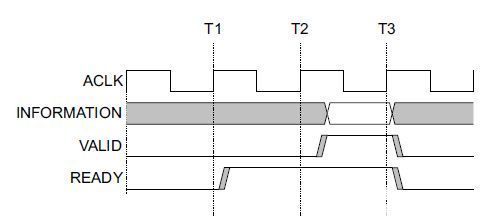

AXI4所采用的是一種READY,VALID握手通信機制,即主從模塊進行數據通信前,先根據操作對各所用到的數據、地址通道進行握手。主要操作包括傳輸發送者A等到傳輸接受者B的READY信號后,A將數據與VALID信號同時發送給B,這是一種典型的握手機制。

AXI總線分為五個通道:

-

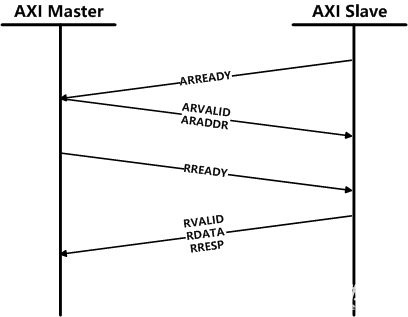

讀地址通道,包含ARVALID, ARADDR, ARREADY信號;

-

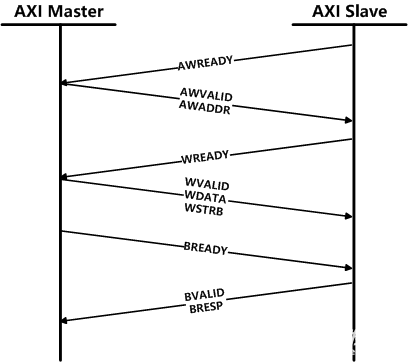

寫地址通道,包含AWVALID,AWADDR, AWREADY信號;

-

讀數據通道,包含RVALID, RDATA, RREADY, RRESP信號;

-

寫數據通道,包含WVALID, WDATA,WSTRB, WREADY信號;

-

寫應答通道,包含BVALID, BRESP, BREADY信號;

-

系統通道,包含:ACLK,ARESETN信號;

其中ACLK為axi總線時鐘,ARESETN是axi總線復位信號,低電平有效;讀寫數據與讀寫地址類信號寬度都為32bit;READY與VALID是對應的通道握手信號;WSTRB信號為1的bit對應WDATA有效數據字節,WSTRB寬度是32bit/8=4bit;BRESP與RRESP分別為寫回應信號,讀回應信號,寬度都為2bit,‘h0代表成功,其他為錯誤。

讀操作順序為主與從進行讀地址通道握手并傳輸地址內容,然后在讀數據通道握手并傳輸所讀內容以及讀取操作的回應,時鐘上升沿有效。如圖所示:

寫操作順序為主與從進行寫地址通道握手并傳輸地址內容,然后在寫數據通道握手并傳輸所讀內容,最后再寫回應通道握手,并傳輸寫回應數據,時鐘上升沿有效。如圖所示:

在我們不擅長寫FPGA的一些代碼時我們往往要借鑒別人的代碼或者使用IP core。在這里筆者從github上找到一個AXI master的代碼,地址是https://github.com/aquaxis/IPCORE/tree/master/aq_axi_vdma。這個工程是一個自己寫的VDMA,里面包含了大量可參考的代碼。筆者這里主要使用了aq_axi_master.v這個代碼用于AXI master讀寫操作。借鑒別人代碼有時會節省很多時間,但如果不能理解的去借鑒,出現問題了很難解決。具體可以參考aq_axi_master.v代碼,有部分修改。

4. ddr讀寫數據的檢驗

有了AXI Master讀寫接口以后比較編寫了一個簡單的驗證模塊,這個驗證模塊是用來驗證ddr ip的,通過寫入數據,然后讀取出來比較。這里要注意的是PS端DDR的起始地址和大小,還有地址的單位是byte還是word,AXI總線的地址單位是byte,測試模塊的地址單位是word(這里的word不一定是4byte)。文件名mem_test.v。

5. Vivado軟件的調試技巧

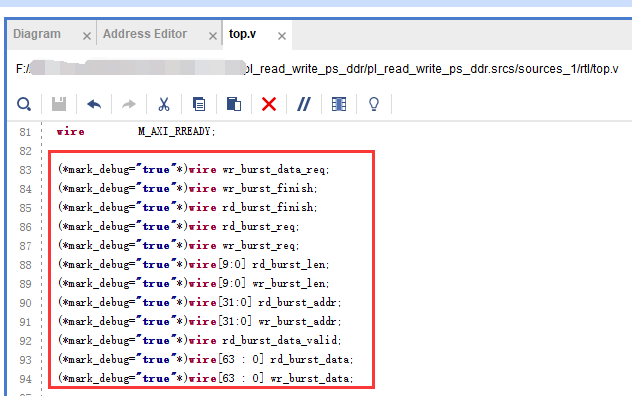

AXI讀寫驗證模塊只有一個error信號用于指示錯誤,如果有數據錯誤我們希望能更精確的信息,altera的quartus II軟件中有signal tap工具,xilinx 的ISE中有chipscope工具,這些都是嵌入式邏輯分析儀,對我們調試有很大幫助,在vivado軟件中調試更加方便。在插入調試信號時有些信息可能會被優化掉,或者信號名稱改變了就不容易識別,這個時候我們可以在程序代碼里加入*mark_debug="true"*這樣的屬性,如下圖的信號:

具體的添加方法在”PL的“Hello World”LED實驗”中已經講過,可參考。

并在XDC文件里綁定error信號到PL端LED燈上。

6. Vitis工程開發

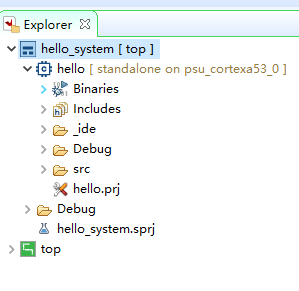

以hello world為模板新建vitis工程如下

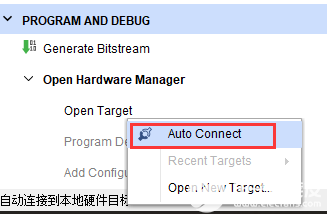

通過vitis下載程序后,系統會復位并且下載FPGA的bit文件。然后回到vivado界面點擊Program and Debug欄自動連接目標如下圖所示:

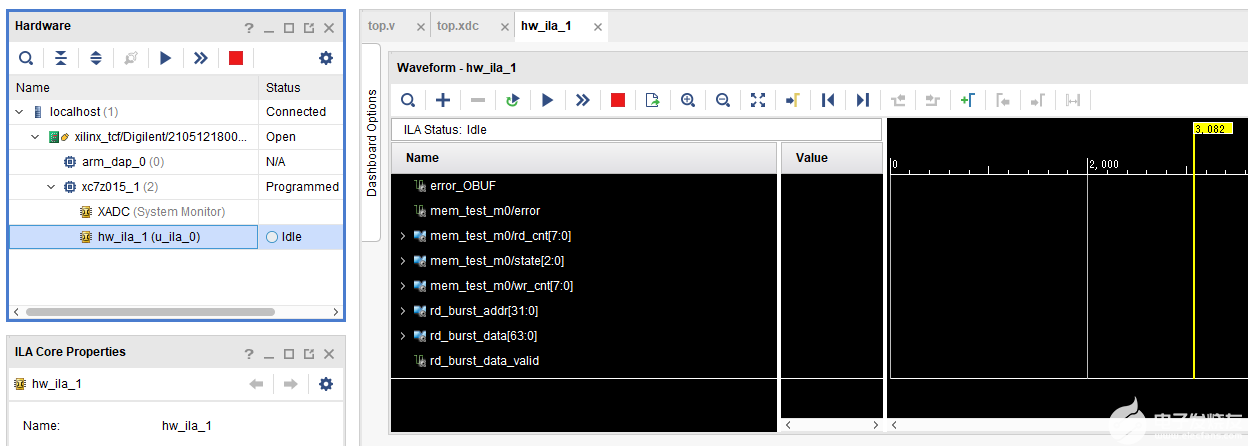

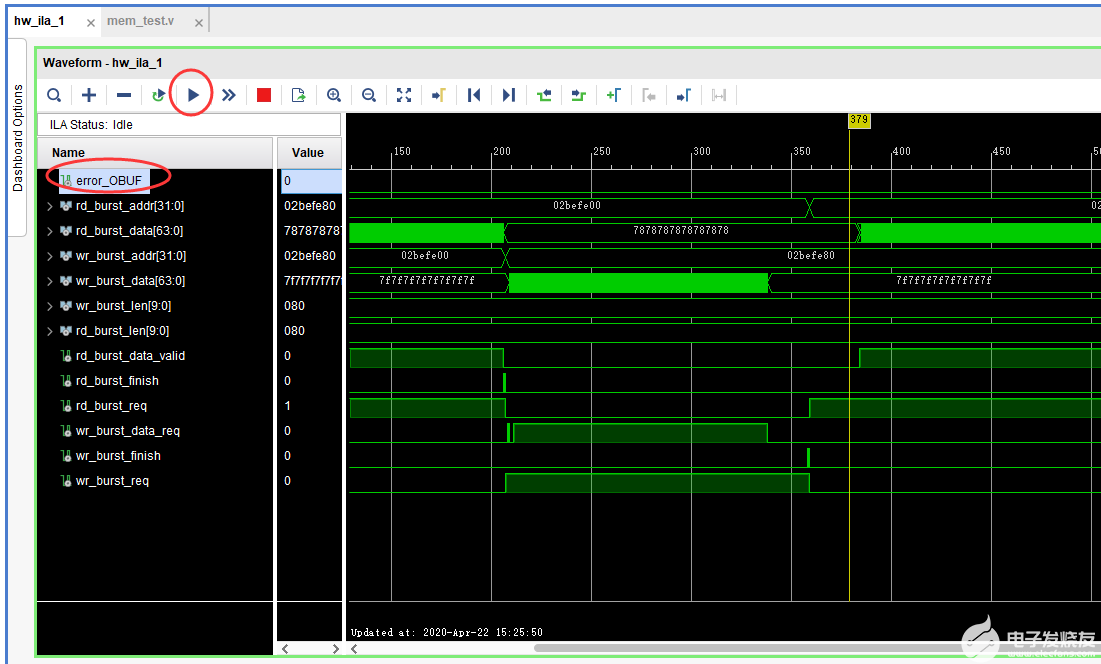

自動連接硬件后可發現JTAG連上的設備,其中有一個hw_ila_1的設備,這個設備就是我們debug設備,選中后可點擊上方黃色三角按鈕捕捉波形。如果有些信號沒有顯示完整,可點擊波形旁邊的“+”按鈕添加。

點擊捕獲波形以后如下圖所示,如果error一直為低,并且讀寫狀態有變化,說明讀寫DDR數據正常,用戶在這里可以自己查看其它的信號來觀察寫入DDR的數據和從DDR讀出的數據。

7. 本章小結

zynq系統相對于單個FPGA或單個ARM要復雜很大,對開發者的基礎知識要求較高,本章內容涉及到AXI協議、zynq的互聯資源、vivado的和Vitis的調試技巧。這些都僅僅是基礎知識,筆者在這里也僅僅是拋磚引玉,大家還是要多多練習,在不斷練習中掌握技巧.

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603419 -

DDR

+關注

關注

11文章

712瀏覽量

65344 -

dma

+關注

關注

3文章

561瀏覽量

100587 -

Zynq

+關注

關注

10文章

609瀏覽量

47182 -

MPSoC

+關注

關注

0文章

198瀏覽量

24283

發布評論請先 登錄

相關推薦

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

《DNK210使用指南 -CanMV版 V1.0》第三十二章 音頻FFT實驗

在米爾電子MPSOC實現12G SDI視頻采集H.265壓縮SGMII萬兆以太網推流

12G-SDI高清視頻開發案例,讓4K視頻采集更便捷!基于Xilinx MPSoC高性能平臺

在米爾電子MPSOC實現12G SDI視頻采集H.265壓縮SGMII萬兆以太網推流

使用TPS65086x PMIC為Xilinx Zynq UltraScale MPSoC供電

開發板的PL端有4片的DDR,怎么管理數據的傳輸

一個更適合工程師和研究僧的FPGA提升課程

有關PL端利用AXI總線控制PS端DDR進行讀寫(從機wready信號一直不拉高)

中高端FPGA如何選擇

AMD推出全新Spartan UltraScale+ FPGA系列

AMD推出Spartan UltraScale+ FPGA系列產品

AMD推出全新Spartan UltraScale+ FPGA系列

在FPGA上為FPGA設計PCB的步驟詳解

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十二章PL讀寫PS端DDR數據

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十二章PL讀寫PS端DDR數據

評論