“點燈”是我們板農們拿到一塊板子后第一個要實現的目標,正如軟件工程師嘗試新的語言必然會先寫出“hello world”一樣。

學習FPGA也不例外,不要小瞧這只小小的LED,它能在你學習的路上帶給你光明,引導一個門外漢跨進可編程邏輯世界的大門!

作為“寒假在家一起練”的第二次直播講座,我們今天就基于1個LED做了1個多小時的分享,從創建第一個FPGA項目、寫下第一句Verilog代碼,到調用FPGA的IP Cores,體驗了FPGA的設計流程以及Verilog的基本語法規范。

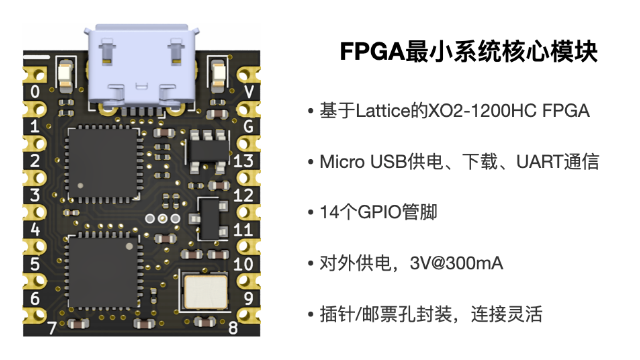

用的平臺是這款:

模塊MIcroUSB右側白色的小東東就是一只用FPGA的IO連接的LED,左側的一只是電源指示燈,只要板上電源工作正常它就能亮。而FPGA連接的LED則可以通過編程FPGA內部的邏輯實現不同的狀態。

BTW,蘇老師所有的FPGA項目中最前面的幾行代碼肯定是一個每秒跳動一次的“心跳燈”,看著它跳動,心安。

先簡單說一下點燈的要素 -LED點燈的工作原理:

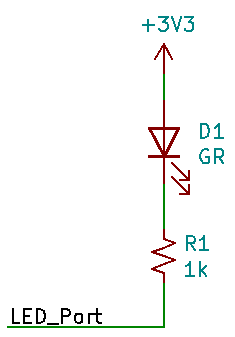

LED的典型連接方式

燈亮以及燈亮時的亮度取決于下面的因素:

供電電源和控制管腳之間的壓差一定要大于LED的正向偏壓Vbias燈才能亮,否則是滅的。不同的器件,不同顏色的LED其偏壓也是不同的,要看數據手冊;

改變電阻值R1(我們一般稱之為限流電阻), I = (3.3V-Vbias)/R1也就發生了變化,LED的亮度也跟著變;

已經設計好的板子,限流電阻的值已經可能動態地改變,如果要調整LED的亮度,就要調節流經LED和限流電阻上的平均電流;

項目1 - 讓LED燈亮起來:

創建項目一個新項目- LED

創建Verilog代碼 module(led),體會Verilog的語法結構;

module LED (led); output led; assign led = 1'b0; endmodule

編譯

分配管腳(查找管腳映射表,通過電路圖或項目中的表格)

生成jed文件

查看資源占用情況

下載到16管腳的FPGA模塊上

項目2 - 讓LED燈跳動起來

在verilog邏輯中通過計數分頻產生12M/223(~1.5Hz) 的周期信號,體會wire、reg的區別以及計數分頻的實現方法

module LED (clk_in,led);input clk_in;output led; reg [23:0] counter; always @(posedge clk_in) counter = counter + 1'b1; assign led = counter[23]; endmodule

編譯

分配管腳中補充新的clk管腳

生成jed文件

查看資源占用情況

下載到16管腳的FPGA模塊上

項目3 - 讓LED燈每秒剛好跳動1次

修改Verilog邏輯,能夠產生精準的1Hz的周期信號,體會偶數分頻乃至奇數分頻的實現方法

module LED (clk_in,led);input clk_in;output led; parameter T1S = 12_000_000;parameter T05S = T1S/2; reg [23:0] counter; always @(posedge clk_in) begin if(counter < T1S-1) counter <= counter + 1'b1; else counter <= 1'b0; end assign led = (counter < T05S); endmodule

生成jed文件

查看資源占用情況

下載到16管腳的fpga模塊上,對比結果

項目4 - 心跳加速會如何?- 50Hz的心跳燈

修改verilog邏輯,產生50Hz的周期信號

生成jed文件

下載到16管腳的fpga模塊上,LED亮度變化,視覺暫留的效果,可以通過調節占空比控制LED的亮度(PWM),亮度與占空比(平均電流)非線性

單色的LED - 通過調節驅動信號的占空比調節LED的亮度

3色的LED - 通過調節每種顏色的LED的亮度實現不同的顏色組合

項目5 - 體驗內部鎖相環的使用以及內部IP Core的調用方式

添加PLL的IP

修改Verilog邏輯,通過PLL輸出的時鐘,產生1Hz的周期信號

生成jed文件

查看資源占用情況

下載到16管腳的fpga模塊上

其實還有更多可玩的,時間關系就讓同學們自己去琢磨和體驗去了,比如:

“呼吸”燈 - 通過PWM來實現呼吸的效果

“流水”燈 -多只LED組合,通過邏輯編程可以實現炫酷的效果(1維)

“交通”燈 - R、G、B三色組合,通過狀態機的編程模擬道路交通燈的工作狀態

數碼管 - 其實也是幾根LED組合在一起的顯示器件

點陣LED屏 - 體會圖形化顯示的基本原理

一顆LED才幾分錢,但可以玩出很多花樣,可以鍛煉很多技能,是不是?

原文標題:通過點燈的邏輯體驗FPGA的編程流程以及Verilog語法基礎

文章出處:【微信公眾號:FPGA入門到精通】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1630文章

21777瀏覽量

604679 -

編程

+關注

關注

88文章

3634瀏覽量

93857

原文標題:通過點燈的邏輯體驗FPGA的編程流程以及Verilog語法基礎

文章出處:【微信號:xiaojiaoyafpga,微信公眾號:電子森林】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

通過點燈邏輯體驗FPGA的編程流程

通過點燈邏輯體驗FPGA的編程流程

評論