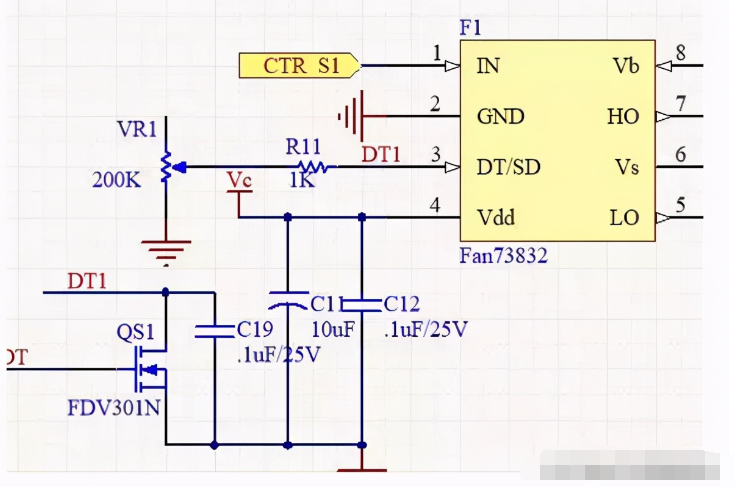

在對某一設計的部分電路進行旁路,雙通道(大電容小電容)或是多通道(三個以上的小電容組成,一般在dsp上用得比較多,目的是使頻率特性更好。)在電容的接地端,(地線的寬與乍會引起頻率的特性),例如在ccd的layout中的bypass,要量電容的接地端的紋波。這就指的是近地端。

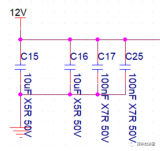

在直流饋線中濾出一切交流成分,可將不同的電容并聯,濾低頻要求電容大,但引線電感不大適合濾高頻,濾高頻要求電容小,不適合濾低頻,如將他們并聯可以同時濾除高低頻。

有些濾波電路用3個電容并聯,分別是電解電容、紙質電容、云母電容,分別濾除電源頻率、音頻和射頻。并聯后電容的esr也會小一點。那么電路圖中經常有一排排電容,大部分是0.1uf的還有10uf的,這大小和個數多少是怎么算的?

一般說是退耦電容。芯片或者說數字電路開關時候對電源影響大,引起電源波動,就要用電容來退歐。容量一般為芯片開關頻率的倒數,如果頻率是1MHz的,就選用1/1M,也就是1uF的電容。可以取大點的。最好就是一個芯片一個退偶電容,電源處還要有,用的數量還是挺大的。

在一般的設計中提到電源去耦通常用0.1uF和10uF、2.2uF、47uF,在實際應用中怎么選擇?根據不同電源輸出還是后續電路呢?

通常情況下,并聯兩個電容就已經足夠了,但對一些電路加上更多的并聯電容效果可能會更好。并聯不同電容值的電容能確保在一個較寬的頻率范圍內都得到一個很低的交流阻抗。

在運放的電源抑制(PSR)能力下降的頻率范圍內,電源旁路尤其重要。電容能夠補償放大器PSR的下降。在很寬的頻率范圍內,這條低阻通路都能確保噪聲不會進入芯片。

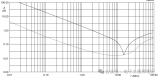

在較低的頻率下,較大的電容能提供一條到地的低阻通路。一旦那些電容達到自諧振頻率,其電容特性消失,轉而變成具有電感特性的元件。這就是為什么使用多個電容并聯的主要原因,它們能夠在很寬的頻率范圍內保持一個較低的交流阻抗。

電源濾波電路中,將0.1uf和10uf的電容并起來使用,有什么作用?

芯片供電要求電源穩定,而實際電源并不穩定,夾雜高頻以及低頻干擾。實際電容與理想電容有很大差別,同時具有RLC三性。

10uf電容對于濾除低頻干擾有較好作用,但對于高頻干擾,電容呈現感性,阻抗很大,無法有效濾除,因此再并一個0.1uf的電容濾除高頻分量。如果你的設計要求不高,也沒必要完全遵照此規則。

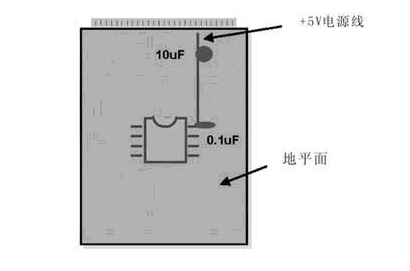

根據經驗,電路的總供電原理圖,原理圖設計時把這些電容畫一起,因為它們是同一網絡,而到實際PCB設計時,這些電容分別放置到各自作用的IC處。電容容量越大、信號頻率越大,電容呈現的交流阻抗越小。

電源(或者信號)或多或少都會疊加一些交流的高頻和低頻信號,這些交流信號對系統來說是不利的。電容并聯放在IC電源腳到地,一般是為了濾除那些對系統不利的交流信號。

10uf的電容和0.1uf一起上是為了使電源(或者是信號)對地的交流阻抗在很寬的頻率范圍內都很小,這樣交流成分能可以被濾除得更干凈。

小結:由于實際供電電源,夾雜著高頻以及低頻干擾雜波,10uf電容對于濾除低頻雜波有較好作用,但對于高頻雜波,電容呈現感性,阻抗很大,無法有效濾除,因此再并一個0。1uf的電容濾除高頻雜波。

責任編輯人:CC

-

電容

+關注

關注

100文章

6045瀏覽量

150344 -

uf

+關注

關注

0文章

3瀏覽量

9932

發布評論請先 登錄

相關推薦

AD5689R創建一個直流電壓源,如何減少輸出噪聲?

CBB電容的誤差范圍 CBB電容的電氣特性

DAC8563 Vout接0.1uF到地的電容時,輸出有約270mV,117khz頻率的正弦紋波,怎么解決?

使用SY7304/SY21314 boost升壓電路紋波過大

求助,關于TPA3123輸出端電容的問題求解

1K的電阻和100uf的低通RC與10K的電阻和10uf的低通RC電路有什么區別?

運放在采用雙電源供電時,如何做好電源的濾波?

OPA551電源10uF去耦電容短路的原因?怎么解決?

用OPA847搭建的小信號放大電路圖,同相輸入端接入0.1uf和100pf這兩個電容,輸出信號自激震蕩怎么解決?

250V10uF的電容能不能代替100V10uF的電容?電容具有哪些作用?

電源濾波電路上的電容參數是如何確定的?

LTM4644在4路都為輕負載輸出情況下,每路COMP接0.1uf電容到地,為什么經常會出現芯片嘯叫?

模擬電路和數字電路PCB布線有何差別?

0.1UF和10UF電容并聯使用的技巧分享

0.1UF和10UF電容并聯使用的技巧分享

評論