邏輯芯片產業正朝著晶體管結構的根本性變革邁進。今天的晶體管,稱為FinFET,將會讓位于被稱為納米片晶體管、多橋溝道FET和柵極全能晶體管的器件。除了制造性能更好、體積更小的晶體管的動力之外,納米片還為電路設計增加了FinFET所缺乏的自由度。本月早些時候,在IEEE國際固態電路會議上,三星的工程師們展示了這種額外的靈活性是如何使片上存儲單元的寫入電壓降低數百毫伏,從而有可能在未來的芯片上節省電力。

盡管中國臺灣半導體制造公司(TSMC)計劃在下一代工藝(3納米節點)中繼續使用FinFET,但三星還是選擇了推出其版本的納米片,即多橋溝道MOSFET(MBCFET)。在場效應晶體管(FinFET)中,溝道區(晶體管中電流流過的部分)是一個從周圍硅中凸出的垂直fin。閘門覆蓋在fin上,覆蓋在fin的三個側面,以控制流經通道的電流。納米片用一堆水平的硅片代替了fin。

三星電子副總裁Taejoong Song在虛擬會議上告訴與會者:“我們已經使用FinFET晶體管大約10年了,但是在3納米晶體管的周圍我們使用的是柵極晶體管。”新的晶體管“提供高速、低功率和小面積”。

但是,正如早期的納米片開發者在IEEE Spectrum上解釋的那樣,新的器件結構增加了finfet所缺乏的設計靈活性。這里的關鍵是晶體管通道的“有效寬度”,即Weff。一般來說,在給定的電壓下,更寬的通道可以驅動更多的電流通過,從而有效地降低其電阻。因為你不能改變FinFET中fin的高度,用今天的晶體管提高Weff的唯一方法就是在每個晶體管上增加更多的fin。所以用FinFET,你可以使Weff增加兩倍或三倍,但不能增加25%或減少20%。然而,你可以改變納米薄片器件的寬度,這樣使用它們的電路就可以由具有各種特性的晶體管組成。

“最近,設計師們在(實現最高設備頻率)和低功耗方面面臨許多挑戰,”Song說。“由于這種設計靈活性,SRAM…可以得到更大的改進。”

宋和他的團隊利用這種靈活性來提高下一代SRAM的性能。SRAM是一種六晶體管的存儲單元,主要用作處理器上的高速緩存,它也是邏輯芯片中最密集的部件之一。三星測試了兩種方案來改善SRAM的寫裕度,即切換電池狀態所需的最小電壓。該值一直處于壓力下,因為芯片互連已縮小,其電阻已因此增加。

SRAM的六個晶體管可分為三對:通柵、上拉和下拉。在FinFET設計中,這三種類型的Weff是相等的。但是對于納米片設備,三星團隊可以自由地進行修改。在其中一處,他們把隘口和斜坡加寬了。在另一個洞里,他們把隘口變寬了,拉下去的通道變窄了。

目的是降低寫入SRAM單元所需的電壓,而不使單元變得如此不穩定以至于讀取時可能會意外地翻轉一點。他們提出的兩種方案利用了這些寬度調整——特別是拓寬通柵晶體管相對于上拉晶體管的寬度——來達到一個SRAM單元,其寫入電壓比正常情況下低230毫伏。

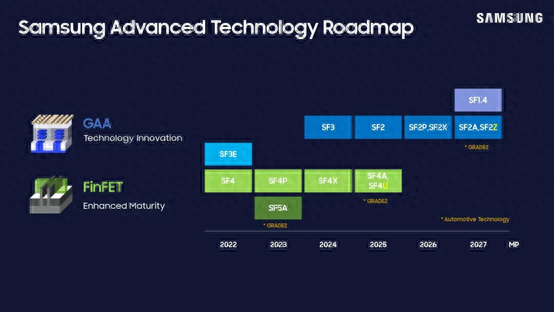

三星預計將在2022年使用3納米制程的MBCFET。

責任編輯:tzh

-

芯片

+關注

關注

456文章

51059瀏覽量

425676 -

MOSFET

+關注

關注

147文章

7212瀏覽量

213821 -

晶體管

+關注

關注

77文章

9723瀏覽量

138621 -

FinFET

+關注

關注

12文章

250瀏覽量

90283

發布評論請先 登錄

相關推薦

英偉達、高通或轉單三星2納米工藝

三星電子:18FDS將成為物聯網和MCU領域的重要工藝

傳2022年三星3納米工藝將使用MBCFET技術

傳2022年三星3納米工藝將使用MBCFET技術

評論